# Development of a Direct Matrix Converter for Micro-grid Applications

# Zahra Malekjamshidi

B.E.(Electrical Engineering)

M.E.(Communication Engineering)

# School of Electrical and Data Engineering University of Technology Sydney Australia

A thesis submitted to the University of Technology Sydney for the Degree of Doctor of Philosophy

May 2018

### CERTIFICATE OF ORIGINALITY

I certify that the work in this thesis has not previously been submitted for a degree nor has it been submitted as part of requirements for a degree except as part of the collaborative doctoral degree and/or fully acknowledged within the text.

I also certify that the thesis has been written by me. Any help that I have received in my research work and the preparation of the thesis itself has been acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis. This research is supported by an Australian Government Research Training Program Scholarship.

Production Note

Signature of Student: Zahra Malekjamshidi Khanehzenyani

Date: 05/05/2018

Signature removed prior to publication.

## ACKNOWLEDGEMENTS

I would like to take this opportunity to gratefully thank to my supervisor, Professor Jianguo Zhu, for his guidance and support, and most importantly, for his utmost patience in me throughout my study at UTS. His extensive knowledge and creative thinking has been a source of inspiration for me throughout the entire research project. I am also thankful to Dr. Ha Pham for his useful suggestions as co-supervisor of the project. I would like to especially thank Dr. Greg Hunter for his advices on practical issues.

Importantly, my appreciation goes towards my parents for their support and unconditional love. Their consistent support and practical experience sharing have been important and helpful during my life.

Last but not least, my minds and thanks always go to my beloved husband, Mohammad, for his love and spiritual support during my PhD study. This thesis would not have been possible without his encouragement and valuable help. I also dedicate this Ph.D. thesis to my two lovely children, Anahid and Avash who are the pride and joy of my life.

#### **ABSTRACT**

Matrix converter is a direct ac-ac converter topology which does not contain a dclink passive component, unlike conventional ac-ac frequency converters. Electrolytic capacitors which are used as the energy storage component have a limited lifetime. They are also bulky and unreliable at very high temperatures. Matrix converter is able to generate controllable sinusoidal ac outputs regarding magnitude and frequency directly from an ac power supply. The other significant advantages offered by matrix converters are the capability of regeneration and adjustable input power factor.

The main objective of this thesis is design, implementation and the stability analysis of the matrix converter for power flow control applications in the context of the microgrids. In this regard, different applications with bidirectional or unidirectional power flow capabilities are considered as the case study. These include using the matrix converter as an interface link between a microgrid and the utility grid, between a variable frequency source such as wind turbine and the microgrid ac bus, and between a variable frequency load such as induction machine and microgrid ac bus.

As bidirectional power flow control between the utility grid and the microgrid is significantly affected by the stability issue, the stability analysis has become an essential part of this research. Details of the input filter design are presented due to the considerable effect of the filter components on the system stability. The effects of the system parameters on the matrix converter stability are investigated using the

small-signal model of the converter. Two methods of stability improvement using the damping resistor and the digital filter are studied in detail. In order to increase the efficiency of the converter, an optimum solution based on the combination of the damping resistor and the digital filter is suggested, and the performance of the proposed method is analyzed. The operation of the matrix converter as an interface between the utility and a microgrid for bidirectional active and reactive power flow control is studied in detail. To control the active and reactive bidirectional power flows, a vector-oriented control method is used.

Two main modulation strategies, the Venturini and space vector modulation, are analyzed and the simulation and experimental results are compared. Due to the better performance of the space vector modulation, this technique is selected for modulation of the designed matrix converter. Different current commutation methods are studied in detail and the simulation and experimental results of four-step semisoft current commutation are presented as the selected commutation method in this work.

Furthermore, a comprehensive simulation study is carried out to investigate the operation of the proposed strategies for modulation, protection, stabilisation and bidirectional power flow control of the matrix converter. To validate the proposed stability analysis and numerical simulations, a prototype direct matrix converter has been developed. The simulation results related to each of the research sections are confirmed through the experimental tests.

# Contents

| CERT   | IFICA'           | TE OF ORIGINALITY                                               | i    |

|--------|------------------|-----------------------------------------------------------------|------|

| ACKN   | NOWLEDGEMENTS    |                                                                 |      |

| ABST   | TRACT            |                                                                 |      |

| CONT   | ΓENTS            |                                                                 |      |

| LIST ( | OF SYMBOLS       |                                                                 |      |

| LIST ( | OF ABBREVIATIONS |                                                                 |      |

| LIST ( | OF FIGURES x     |                                                                 | xiii |

| LIST ( | OF TA            | BLES                                                            | XXV  |

| СНАР   | TER1:            | INTRODUCTION                                                    | 1    |

| 1.1    | Power            | Electronic Converters                                           | . 1  |

|        | 1.1.1            | Indirect ac-ac power converter                                  | 2    |

|        | 1.1.2            | Direct ac-ac power converter                                    | 4    |

| 1.2    | A Rev            | iew on the Matrix Converter Applications in Microgrids          | . 9  |

|        | 1.2.1            | Matrix converter as an interface link between the               |      |

|        |                  | microgrid and the utility grid                                  | . 9  |

|        | 1.2.2            | Other applications of the matrix converters in the microgrids . | . 14 |

| 1.3    | Motiva           | ation and Objectives of the Project                             | 16   |

| 1.4    | Thesis           | Outline                                                         | 18   |

| CHAP   | TER2             | MATRIX CONVERTER FUNDAMENTALS AND                               | 00   |

|        |                  | PROTECTION TECHNIQUES                                           | 20   |

| 2.1  | Introduction                                                             | 20 |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Bidirectional Switches                                                   | 22 |

| 2.3  | Input Filter                                                             | 23 |

|      | 2.3.1 Design of the input filter                                         | 25 |

| 2.4  | Clamp Circuit                                                            | 30 |

| 2.5  | Safe Commutation Techniques For DMCs                                     | 34 |

|      | 2.5.1 Output current direction based four-step semi-soft commuta-        |    |

|      | tion method                                                              | 38 |

|      | 2.5.2 Two-step semi-soft commutation method                              | 46 |

|      | 2.5.3 Overlap current commutation method                                 | 50 |

|      | 2.5.4 Dead-time current commutation method                               | 50 |

|      | 2.5.5 Input voltage polarity based commutation method                    | 51 |

| 2.6  | Conclusion                                                               | 55 |

| CHAD | OTED 2. MODIJI ATIONI METIJODE CIMIJI ATIONIC AND                        |    |

| СПАР | PTER3: MODULATION METHODS, SIMULATIONS AND EXPERIMENTAL RESULTS          | 57 |

| 3.1  |                                                                          | 57 |

| 3.2  |                                                                          | 59 |

| 0.2  |                                                                          | 62 |

|      | 3.2.2 Simulation results of Alesina-Venturini and its optimised method   |    |

| 3.3  | -                                                                        | 64 |

| 0.0  |                                                                          | 66 |

|      |                                                                          | 76 |

|      |                                                                          | 83 |

|      |                                                                          | 91 |

|      | 3.3.5 The inverter stage                                                 |    |

|      | 3.3.6 Indirect space vector modulation for the entire matrix converter 9 |    |

|      | 3.3.7 Simulation results of the indirect matrix converter                |    |

| 3.4  | Conclusion                                                               |    |

|      |                                                                          |    |

| CHAP | PTER4: DESIGN AND IMPLEMENTATION OF A DIRECT                             |    |

|      | MATRIX CONVERTER PROTOTYPE 10                                            |    |

| 4.1  | Introduction                                                             |    |

| 4.2  | The Power Module                                                         |    |

| 4.3  | Gate Drive Circuits                                                      |    |

| 4.4  | Interface Board                                                          | )8 |

| 4.5  | Input  | Filter                                                                    | 111 |

|------|--------|---------------------------------------------------------------------------|-----|

| 4.6  | Clamp  | Circuit                                                                   | 114 |

| 4.7  | Matri  | x Converter Control                                                       | 115 |

| 4.8  | Measu  | rement and Protection Circuits                                            | 119 |

|      | 4.8.1  | Input voltage measurement and protection circuits                         | 121 |

|      | 4.8.2  | Output current measurement                                                | 123 |

| 4.9  | Concl  | usion                                                                     | 125 |

| СНИВ | търк   | : STABILITY ANALYSIS OF THE MATRIX                                        |     |

| CHAF | TERO   |                                                                           | 129 |

| 5.1  | Introd | luction                                                                   |     |

| 5.2  |        | ity Analysis of the MC                                                    |     |

|      | 5.2.1  | Developing the mathematical model                                         |     |

|      | 5.2.2  | Small-Signal Model                                                        |     |

|      | 5.2.3  | Numerical approach for stability analysis                                 |     |

|      | 5.2.4  | Stability analysis for maximum output power                               | 142 |

| 5.3  | Stabil | ity Analysis of the MC With Damping Resistor                              | 148 |

|      | 5.3.1  | Numerical approach for stability analysis of the MC with the              |     |

|      |        | damping resistor                                                          | 151 |

| 5.4  | Stabil | ity of the MC With Digital Low-Pass Input Filter                          | 155 |

|      | 5.4.1  | Numerical approach for stability analysis of the MC with dig-             |     |

|      |        | ital input filter                                                         | 158 |

| 5.5  | Concl  | usion                                                                     | 161 |

| CHAP | TER6   | : BIDIRECTIONAL POWER FLOW CONTROL                                        | 162 |

| 6.1  | Introd | luction                                                                   | 162 |

|      | 6.1.1  | System stabilisation using the damping resistor                           | 164 |

|      | 6.1.2  | Improving the stability using the digital filter                          | 169 |

| 6.2  | Syster | n Stabilisation by Applying a Combination of the Damping                  |     |

|      | Resist | ance and Digital Input Filter                                             | 170 |

| 6.3  | Unidi  | rectional Power Flow Control                                              | 181 |

|      | 6.3.1  | Unidirectional power flow control with damping resistor $\mathcal{R}_d$   | 183 |

|      | 6.3.2  | Unidirectional power flow control with digital input filter $ . $ . $ . $ | 184 |

|      | 6.3.3  | Unidirectional power flow control with a combination of the               |     |

|      |        | damping resistor and digital input filter                                 | 188 |

|      | 6.3.4  | Experimental results for unidirectional active power flow control         | 190 |

| 6.4    | Bidire         | ctional Power Flow Control                                        | 192 |

|--------|----------------|-------------------------------------------------------------------|-----|

|        | 6.4.1          | Bidirectional power flow control with damping resistor $R_d$      | 196 |

|        | 6.4.2          | Bidirectional power flow control with                             |     |

|        |                | digital input filter                                              | 202 |

|        | 6.4.3          | Bidirectional power flow control using a combination of the       |     |

|        |                | damping resistor and the digital input filter stabilisation meth- |     |

|        |                | ods                                                               | 206 |

|        | 6.4.4          | Experimental results of bidirectional power flow control          | 208 |

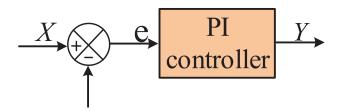

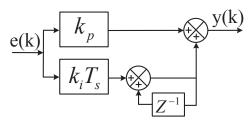

| 6.5    | PI Co          | ${ m ntroller}$                                                   | 215 |

| 6.6    | Anti-w         | vindup PI Controller                                              | 217 |

| 6.7    | Conclu         | ısion                                                             | 218 |

| CHAP   | $	ext{TER7}$ : | CONCLUSIONS AND FUTURE WORK                                       | 220 |

| 7.1    | Conclu         | isions                                                            | 220 |

| 7.2    | Recom          | nmendation For Future Work                                        | 222 |

| LIST ( | )F PU          | BLICATIONS BASED ON THE THESIS WORK                               | 224 |

| REFEI  | REFERENCES 238 |                                                                   | 238 |

# LIST OF SYMBOLS

q Voltage gain

$i_x, i_y, i_z$  Instantaneous output currents, A

$v_x, v_y, v_z$  Instantaneous output voltages, V

$i_A, i_B, i_C$  Instantaneous input currents, A

$L_f$  Input filter inductance

$C_f$  Input filter capacitance

$R_f$  Resistance of the input filter inductance

$\omega_{coff}$  Cut-off frequency of the input filter

$\zeta$  The damping factor of the input filter

$R_d$  Damping resistance

$R_s$  Line resistance

$L_s$  Line inductance

$L_l$  Load inductance

$R_l$  Load resistance

$C_c$  Clamp capacitance

$\tilde{\beta}_i$  Phase angle of the input current vector

$\tilde{\alpha}_o$  Phase angle of the output voltage vector

$i_i(t)$  Instantaneous input current, A

$v_{si}(t)$  Instantaneous output voltages, V

$v_{im}(t)$  Input voltage amplitude, V

$I_{im}(t)$  Input current amplitude, A

$v_{om}(t)$  Output voltage amplitude, V

$I_{om}(t)$  Output current amplitude, A

$P_i$  Input power

$P_o$  Output power

$\varphi_i$  Input displacement angle

$\varphi_o$  Output displacement angle

$PF_{in}$  Input power factor

$\omega_i$  Input angular frequency

$\omega_o$  Output angular frequency

$S_{kj}$  Switching function of a single switch

$m_{kj}$  Duty cycle of the switch  $S_{kj}$

$t_{kj}$  Conduction time of the switch  $S_{kj}$

$T_s$  Switching period

$v_{o,ref}$  Output reference voltage

$k_i$  Input current sector

$k_v$  Output voltage sector

$f_i$  Input frequency

$f_o$  Output frequency

$f_s$  Switching frequency

$\vec{V_o}$  Output voltage space vector

$\vec{I}_i$  Input current space vector

P Active power

Q Reactive power

# LIST OF ABBREVIATIONS

ac alternative current

ac direct current

ADC Analog to Digital Converter

BBVSC Back-to-Back Voltage Source Converter

CD Current Direction

CSR Current Source Rectifier

DB-VSI Diode-Bridge Voltage Source Inverter

DAC Digital to Analog Converter

DMC Direct Matrix Converter

DSP Digital Signal Processor

DSVM Direct Space Vector Modulation

FCC Forced Commutated Cycloconverter

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

IC Integrated Circuit

IGBT Insulated-Gate Bipolar Transistor

ILMC Inverting Link Matrix Converter

IMC Indirect Matrix Converter

ISVM Indirect Space Vector Modulation

LPF Low-Pass Filter

MC Matrix Converter

NCC Naturally Commutated Cycloconverter

OC Over Current

OV Over Voltage

PC Personal computer

PCB Printed Circuit Board

PF Power Factor

PI Proportional and Integral

PLL Phase Locked Loop

PWM Pulse Width Modulation

RBIGBT Reverse Blocking Insulated-Gate Bipolar Transistor

rms root mean square

SMC Sparse Matrix Converter

SVM Space Vector Modulation

THD Total Harmonic Distortion

TL Threshold Level

USMC Ultra Sparse Matrix Converter

VHDL Very high peed integrated circuit Hardware Description Language

VOC Voltage Oriented Control

VSI Voltage Source Inverter

VSMC Very Sparse Matrix Converter

3LVSI Three-Level Voltage Source Inverter

ZOH Zero Order Hold

# List of Figures

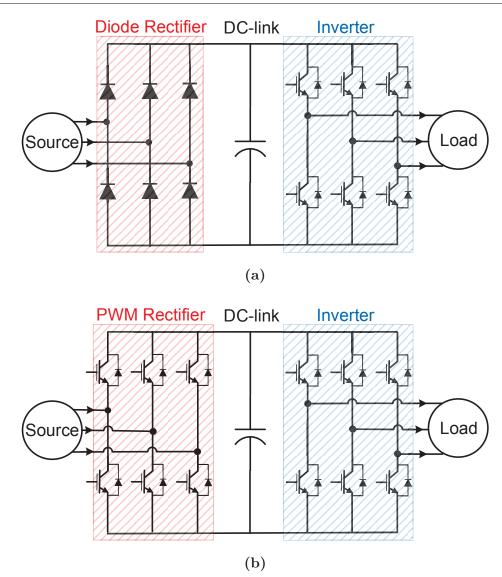

| Figure 1.1  | ac-ac indirect power converter, with the intermediate $dc-link$                        |    |

|-------------|----------------------------------------------------------------------------------------|----|

| stage a     | a) With diode bridge on the supply side (DB-VSI) b) back-to-                           |    |

| back v      | oltage source converter (BBVSC)                                                        | 2  |

| Figure 1.2  | ac-ac indirect power converter, with the $dc-link$ stage and                           |    |

| 3LVSI       | on the output side                                                                     | 4  |

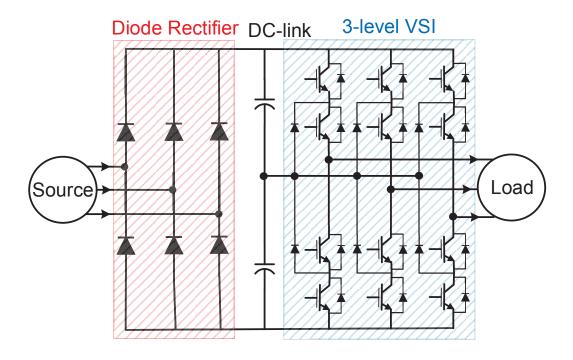

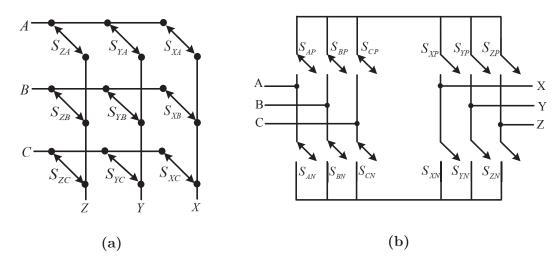

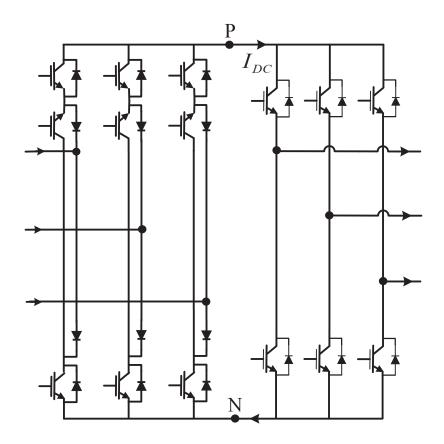

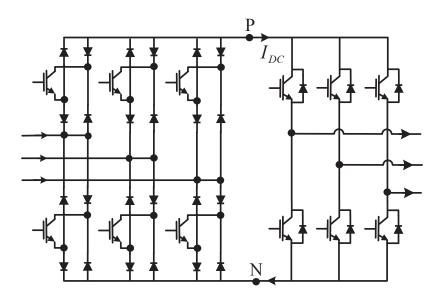

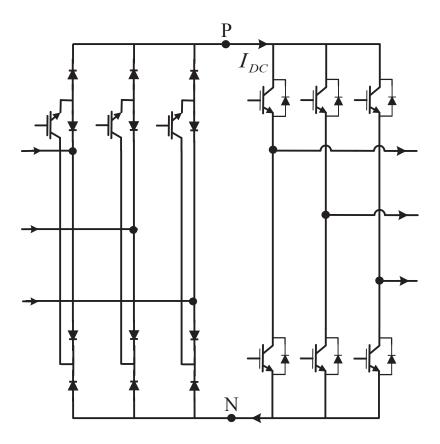

| Figure 1.3  | ac-ac direct power converters a) DMC b) IMC                                            | 5  |

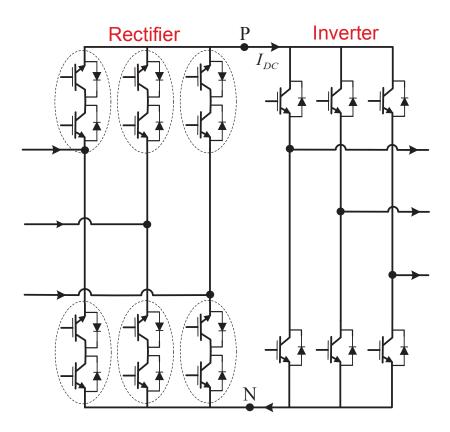

| Figure 1.4  | Schematic of the Indirect Matrix Converter (IMC)                                       | 6  |

| Figure 1.5  | Schematic of the sparse matrix converter (SMC)                                         | 7  |

| Figure 1.6  | Schematic of the very sparse matrix converter (VSMC) $$                                | 7  |

| Figure 1.7  | Schematic of the ultra sparse matrix converter (USMC)                                  | 8  |

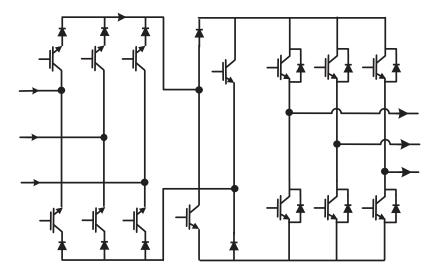

| Figure 1.8  | Schematic of the inverting link matrix $\operatorname{converter}(\operatorname{ILMC})$ | 8  |

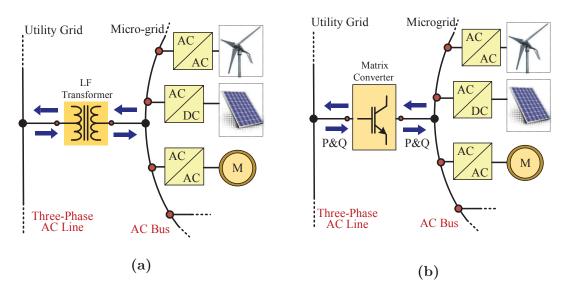

| Figure 1.9  | a) Using a transformer as an interface link between the micro-                         |    |

| grid ar     | nd the utility grid at the PCC, b) Using a matrix converter as                         |    |

| an inte     | erface link at the PCC                                                                 | 10 |

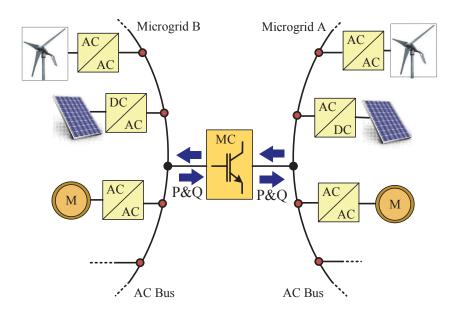

| Figure 1.10 | Application of the MC as a link between two microgrids $$                              | 11 |

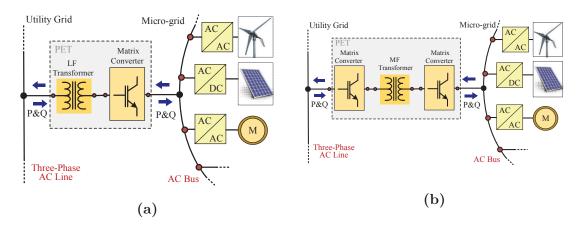

| Figure 1.11 | Application of the MC as a link between the utility grid and a                         |    |

| microg      | grid, a) Using a MC with a low-frequency transformer, b) Using                         |    |

| two M       | Cs with a medium-frequency transformer                                                 | 12 |

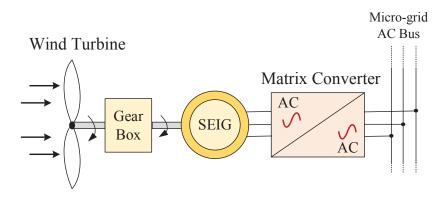

| Figure 1.12 | Application of the MC as an interface between a variable-                              |    |

| freque      | ncy wind turbine generator or a high-frequency generator and                           |    |

| the mi      | crogrid ac bus                                                                         | 14 |

| Figure 1.13 | Application of the MC in doubly fed induction generators                               |    |

| (DFIG       | ) for variable speed generation systems                                                | 15 |

| Figure 1.14 | Application of the MC as an interface between the microgrid                            |    |

| ac bus      | and the ac load with variable frequency                                                | 16 |

|             |                                                                                        |    |

| Figure 2.1 Back-to-back bidirectional switches configurations a) Common-               |    |

|----------------------------------------------------------------------------------------|----|

| collector b) Common-emitter                                                            | 21 |

| Figure 2.2 Other possible bidirectional switch arrangements a) Switch-                 |    |

| diode bridge b) Antiparallel reverse blocking IGBTs (RBIGBTs) c)                       |    |

| Switch and diode in series configuration                                               | 21 |

| Figure 2.3 Package and the circuit configuration of Dynex IGBT bidirec-                |    |

| tional switch module $[1,2]$                                                           | 21 |

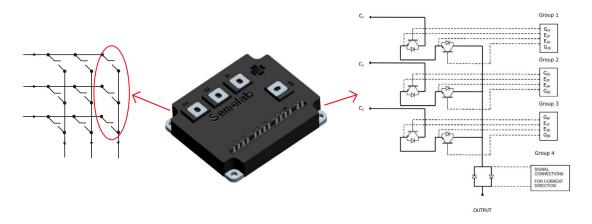

| Figure 2.4 SEMELAB SML150MAT12 bidirectional module [3]                                | 22 |

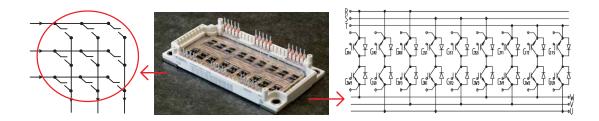

| Figure 2.5 EconoMAC three-phase bidirectional switch module [4] $ \dots $              | 22 |

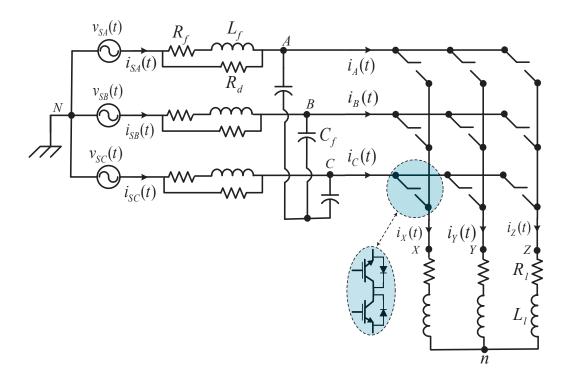

| Figure 2.6 Basic power circuit of the DMC with the input filter and RL                 |    |

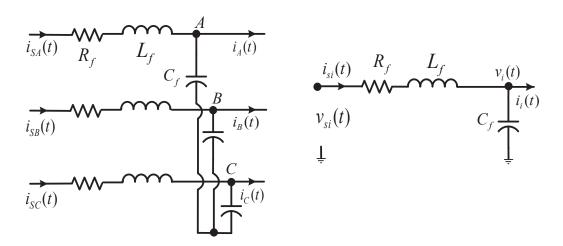

| load                                                                                   | 24 |

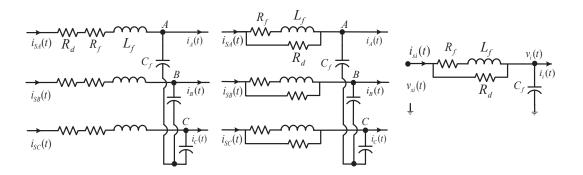

| Figure 2.7 Second order LC filter, three-phase and single-phase                        | 25 |

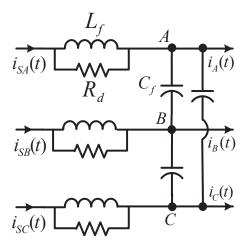

| Figure 2.8 Second order LC filter with damping resistors a) In series with             |    |

| the inductors b) In parallel with the inductors c) Single-phase diagram                |    |

| for parallel damping resistor                                                          | 27 |

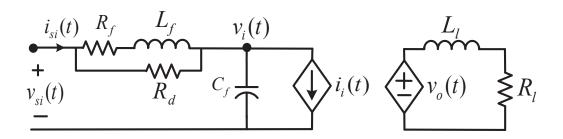

| Figure 2.9 Per-phase equivalent scheme of direct matrix converter $\dots$ .            | 28 |

| Figure 2.10 Second order LC filter with bypass relays for preventing of                |    |

| more power loss, and damping resistors a) in parallel b) in series with                |    |

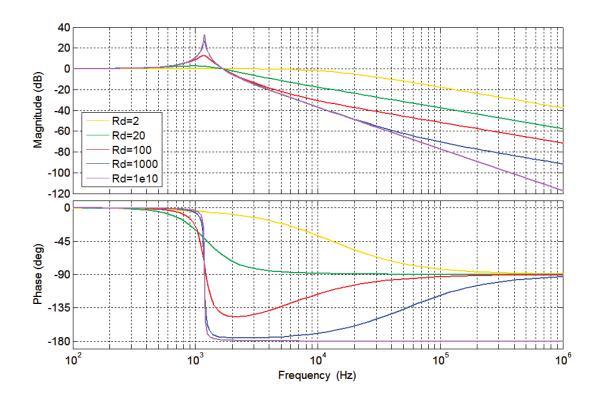

| the inductors                                                                          | 30 |

| Figure 2.11 Comparison of the bode plots of the damped LC filter transfer              |    |

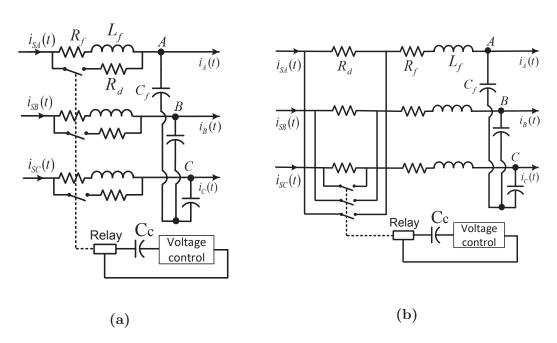

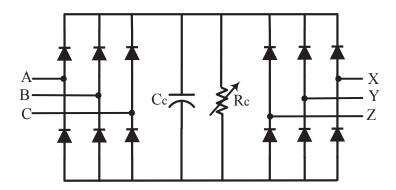

| function for different values of the damping resistor                                  | 31 |

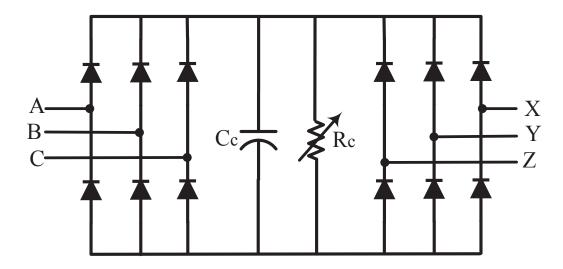

| Figure 2.12 Circuit diagram of the voltage clamp used for converter pro-               |    |

| tection against overvoltage spikes                                                     | 32 |

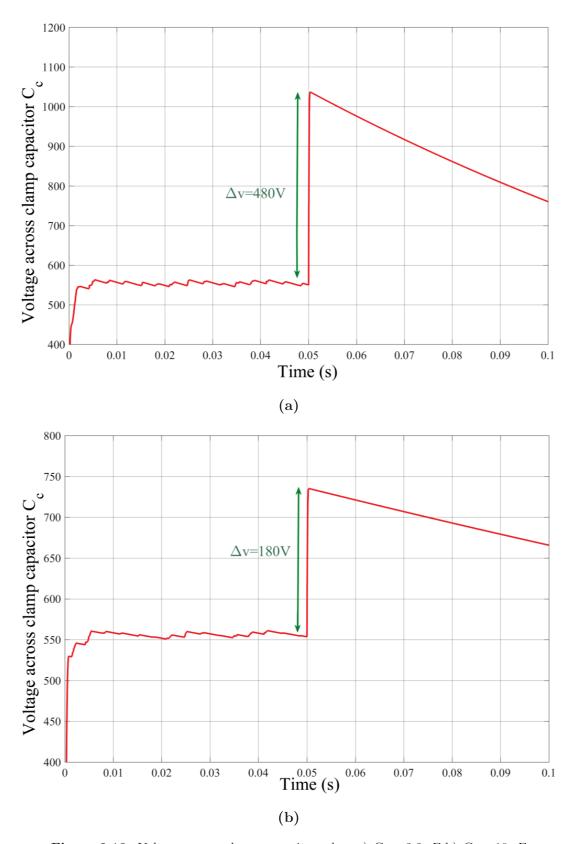

| Figure 2.13 Voltage across clamp capacitor when a) $C_c = 3.2 \mu F$ b) $C_c =$        |    |

| $10\mu F$                                                                              | 33 |

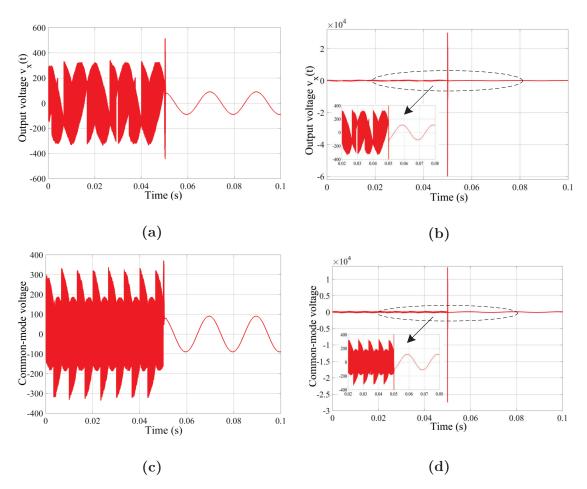

| Figure 2.14 a) Output voltage $v_x(t)$ with clamp circuit, b) Output voltage           |    |

| $v_x(t)$ without clamp circuit, c) Common-mode voltage with clamp                      |    |

| circuit, and d) Common-mode voltage without clamp circuit                              | 35 |

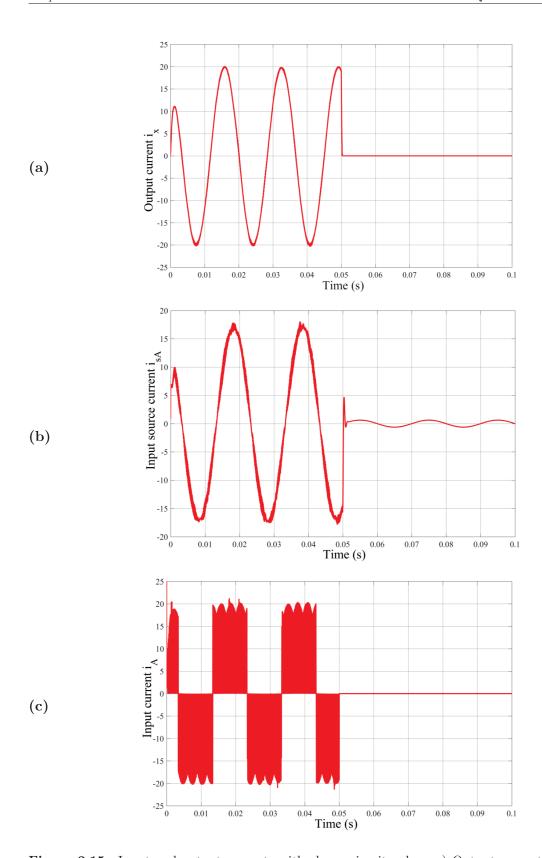

| Figure 2.15 Input and output currents with clamp circuit, where a) Output              |    |

| current $i_x(t)$ , b) Input source current $i_{sA}(t)$ , and c) Input current $i_A(t)$ | 36 |

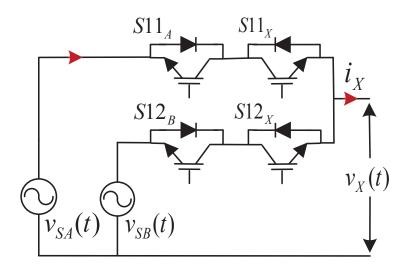

| Figure 2.16 Matrix converter with two-phase input source and single-phase              |    |

| load                                                                                   | 37 |

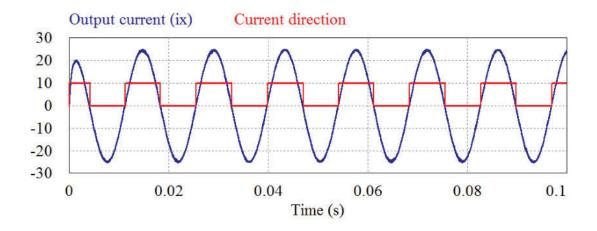

| Figure 2.17 Simulation results of the output current direction                         | 38 |

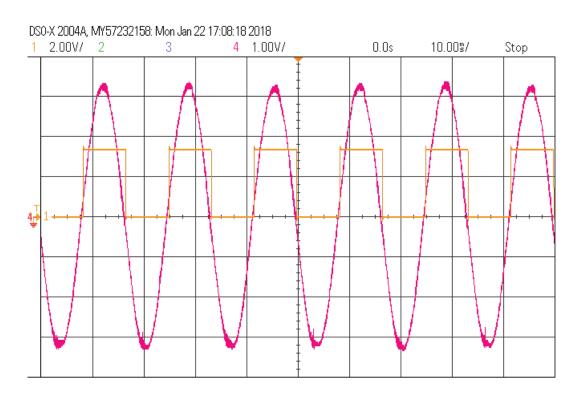

| Figure 2.18 Experimental result of the output current $i_v$ and its direction.         | 39 |

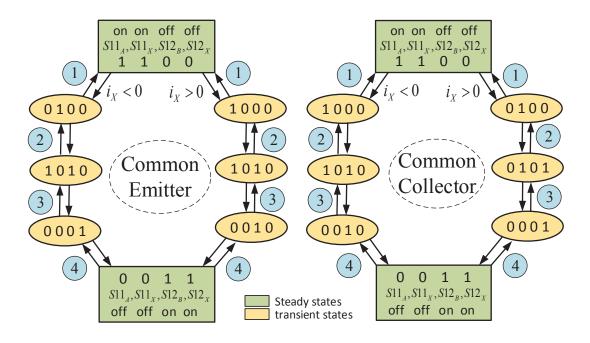

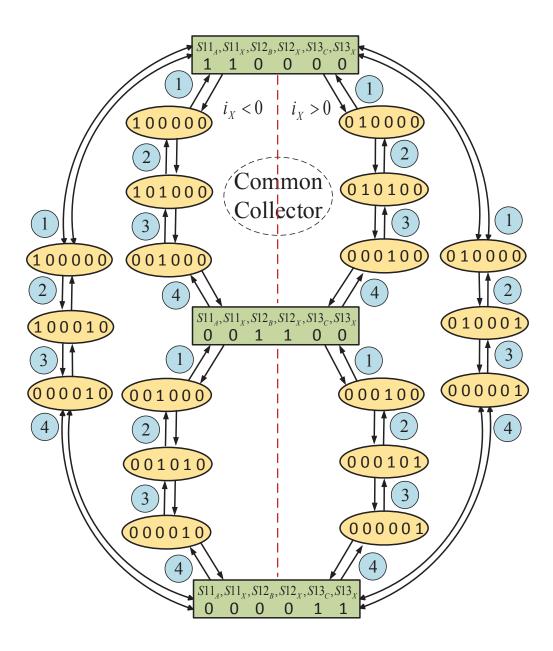

| Figure 2.19 State diagram of the soft-switching four-step commutation                   |    |

|-----------------------------------------------------------------------------------------|----|

| strategy for both switch cell arrangements                                              | 39 |

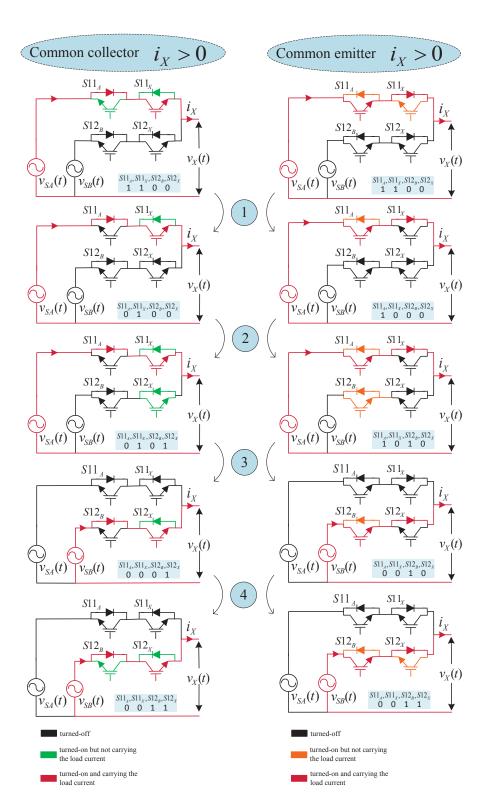

| Figure 2.20 Four step semi-soft commutation of the bidirectional switches               |    |

| for a two-phase to single-phase DMC, when the current direction is                      |    |

| toward the load $i_x > 0$ (common-collector and common-emitter modes)                   | 41 |

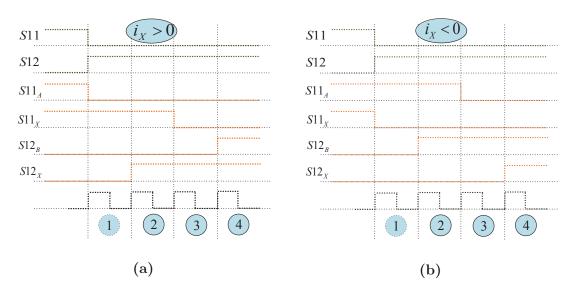

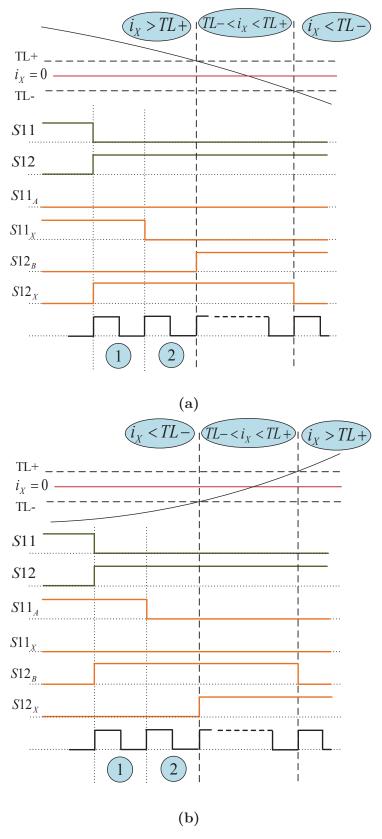

| Figure 2.21 Timing diagram of the four-step commutation strategy for                    |    |

| common-collector switch cell arrangement, where a) $i_x > 0$ , and b)                   |    |

| $i_x < 0$                                                                               | 42 |

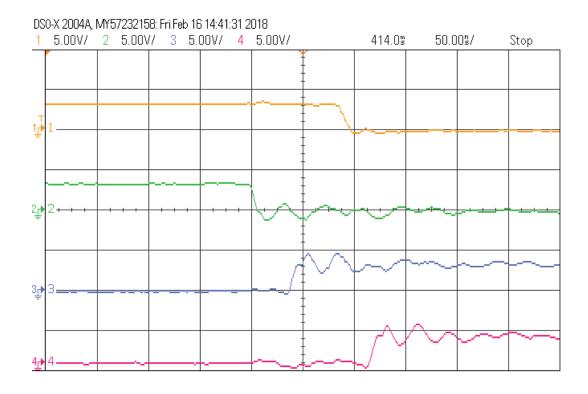

| Figure 2.22 Experimental result of the four-step semi-soft commutation                  | 42 |

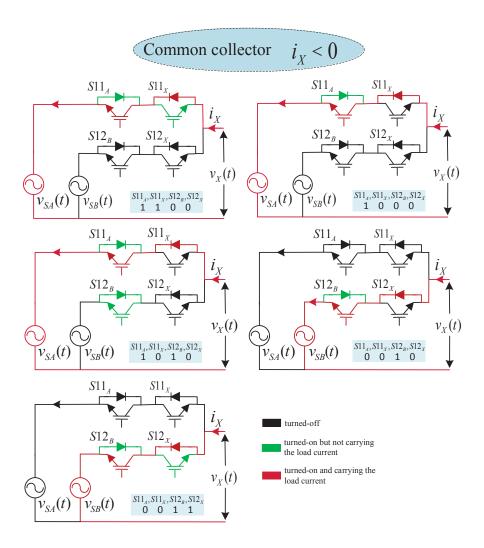

| Figure 2.23 Four-step semi-soft commutation of the bidirectional switches               |    |

| for a two-phase to single-phase DMC when the current direction is                       |    |

| from the load (common-collector) $\dots$                                                | 43 |

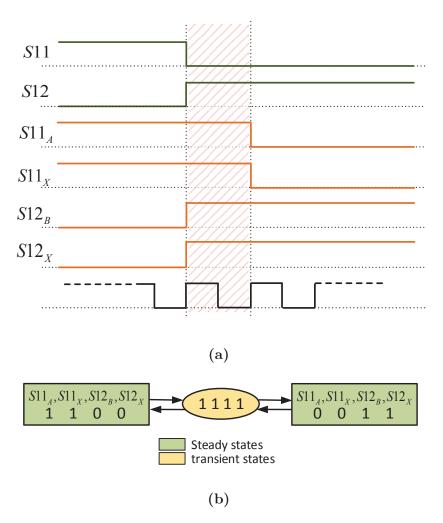

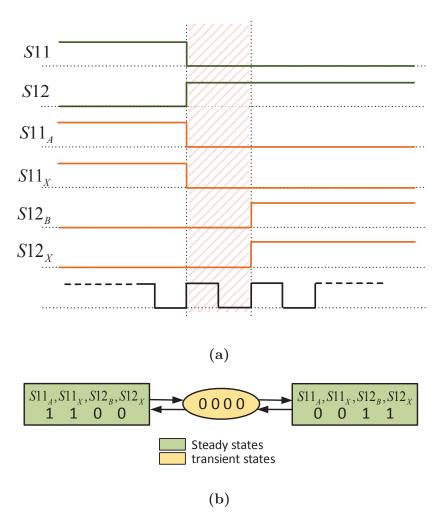

| Figure 2.24 State diagram of the semisoft-switching four-step commuta-                  |    |

| tion strategy for a three-phase to single-phase DMC                                     | 44 |

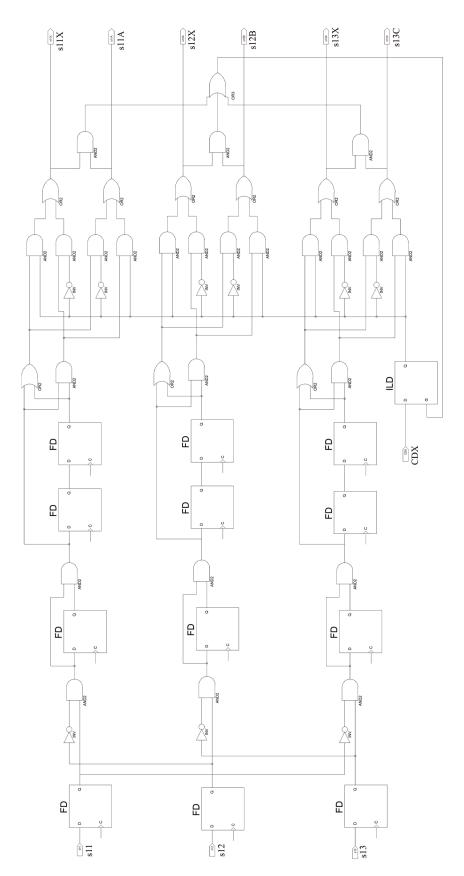

| Figure 2.25 Schematic of the four-step commutation strategy for a three-                |    |

| phase to single-phase DMC using the logic elements $[5]$                                | 45 |

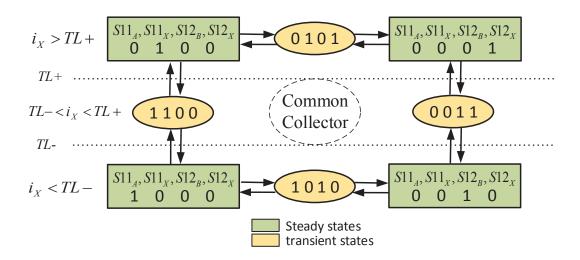

| Figure 2.26 State diagram of the current-direction based two-step commu-                |    |

| tation strategy for two bidirectional switches                                          | 47 |

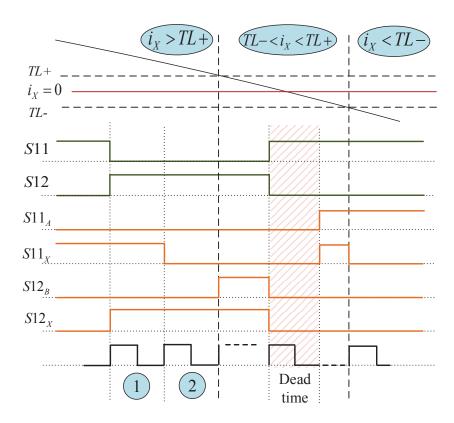

| Figure 2.27 Timing diagram of the current direction based two-step com-                 |    |

| mutation when the commutation is needed within the threshold levels                     | 48 |

| Figure 2.28 Timing diagram of two-step commutation for common-collector                 |    |

| switch cell arrangement a) $i_x > 0$ b) $i_x < 0 \dots \dots \dots \dots$               | 49 |

| Figure 2.29 Overlap current commutation, where a) Timing diagram, and                   |    |

| b) state diagram                                                                        | 51 |

| Figure 2.30 Dead-time current commutation, where a) Timing diagram,                     |    |

| and b) state diagram                                                                    | 52 |

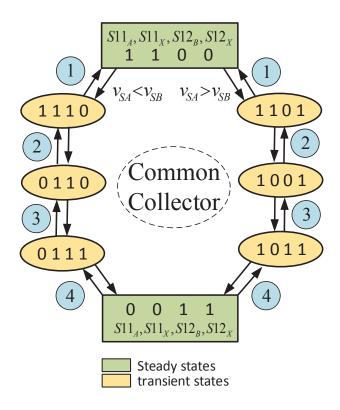

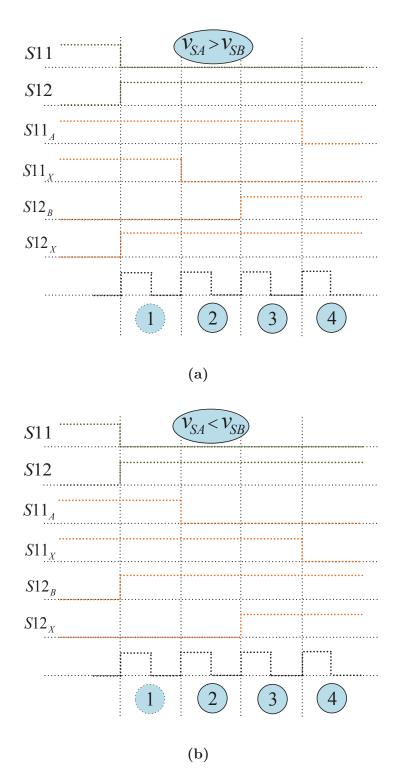

| Figure 2.31 State diagram of the voltage-polarity based four-step commu-                |    |

| tation strategy for two bidirectional switches                                          | 53 |

| Figure 2.32 Timing diagram of the voltage-polarity based four-step com-                 |    |

| mutation strategy for common-collector switch cell arrangement, where                   |    |

| a) $v_{SA} > v_{SB}$ , and b) $v_{SA} < v_{SB}$                                         | 54 |

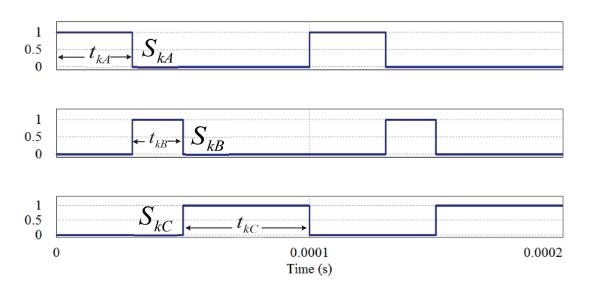

| Figure 3.1 Switching pattern of the $kth$ output phase in Venturini method              | 61 |

| Figure 3.2 Sinusoidal output voltages $(\bar{v}_{kN})$ , fitting into input three-phase |    |

| voltages                                                                                | 62 |

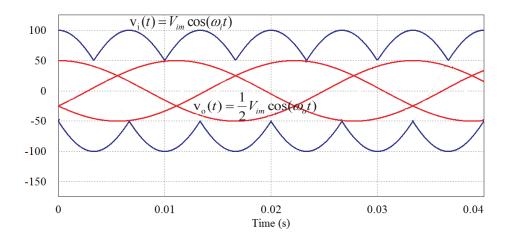

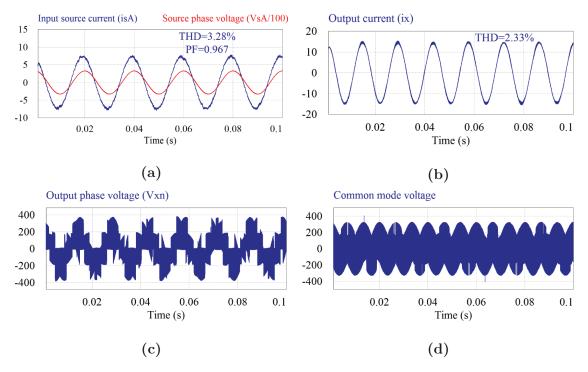

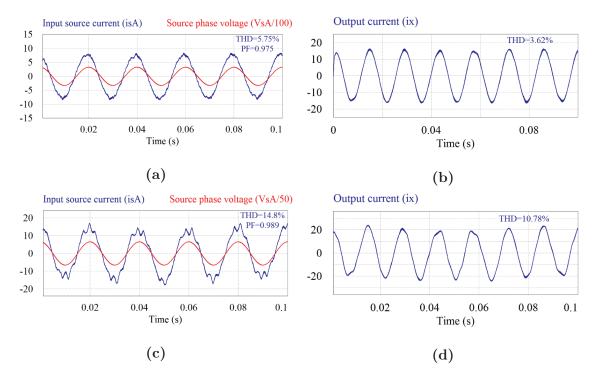

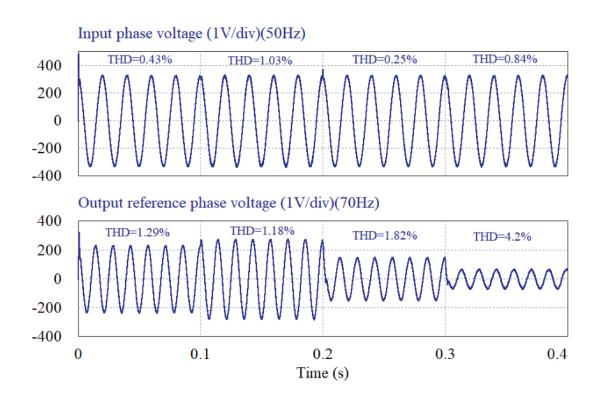

| Figure 3.3 Simulation results of Alesina-Venturini method for output ref-           |    |

|-------------------------------------------------------------------------------------|----|

| erence voltage $v_{o,ref} = 195V(line-line)$ , where a) Input source cur-           |    |

| rent and voltage of phase (A), b) Output current $i_x$ , c) Output phase            |    |

| voltage $v_{xn}$ , and d) Common mode voltage                                       | 64 |

| ${\bf Figure~3.4~~Simulation~results~of~Alesina-Venturini~optimised~method,~where}$ |    |

| a and c) Input source current and voltage of phase (A) when output                  |    |

| reference voltage is $v_{o,ref} = 200V$ and $v_{o,ref} = 300V$ (line-line), and b   |    |

| and d) Output current $i_x$ when output reference voltage $v_{o,ref} = 200V$        |    |

| and $v_{o,ref} = 300V$ (line-line), respectively                                    | 65 |

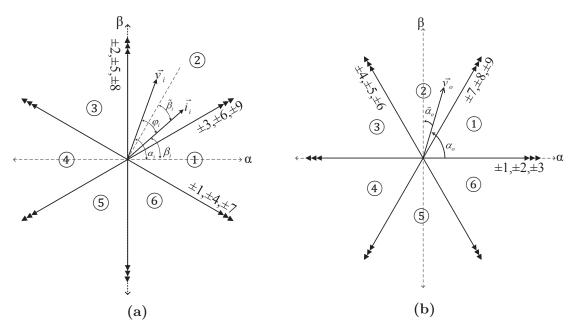

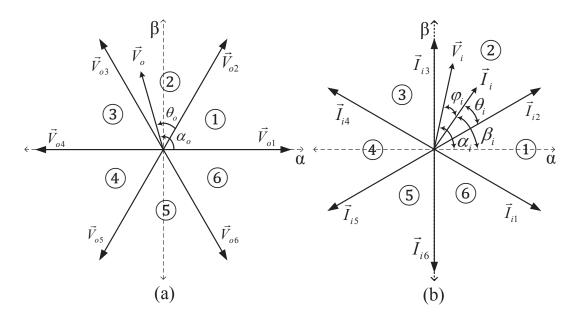

| Figure 3.5 Complex space vector for active configurations a) Input cur-             |    |

| rent switching vectors b) Output voltage switching vectors                          | 68 |

| Figure 3.6 $$ Connected switches in case of using one zero configuration $$ . $$    | 71 |

| Figure 3.7 $$ Connected switches in case of using three zero configurations $$ .    | 71 |

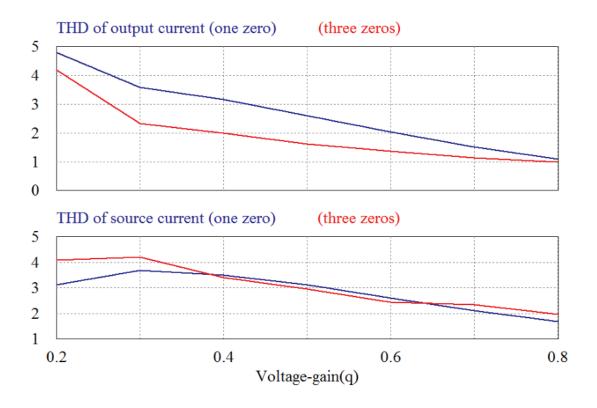

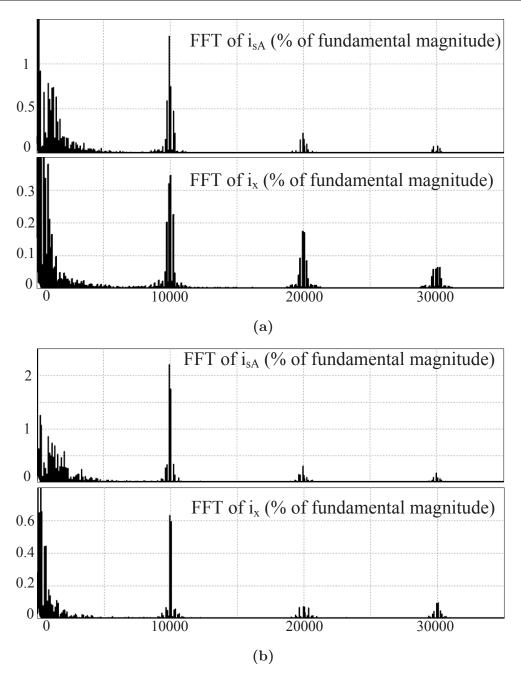

| Figure 3.8 THD of the input source current and the output current using             |    |

| the switching pattern with one and three zeros                                      | 72 |

| Figure 3.9 Input power factor using the switching pattern with one and              |    |

| three zeros                                                                         | 73 |

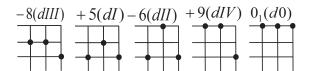

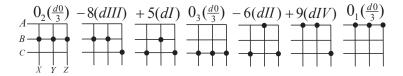

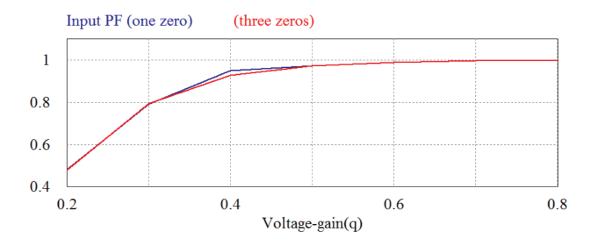

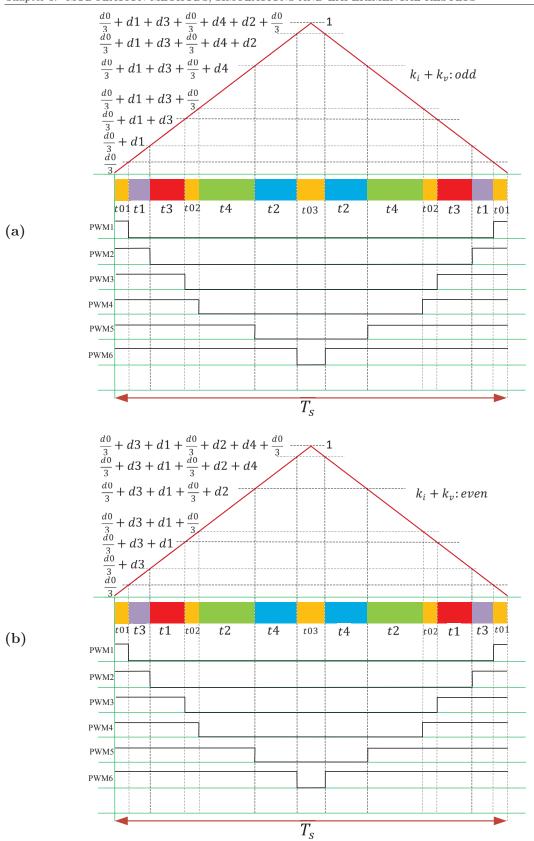

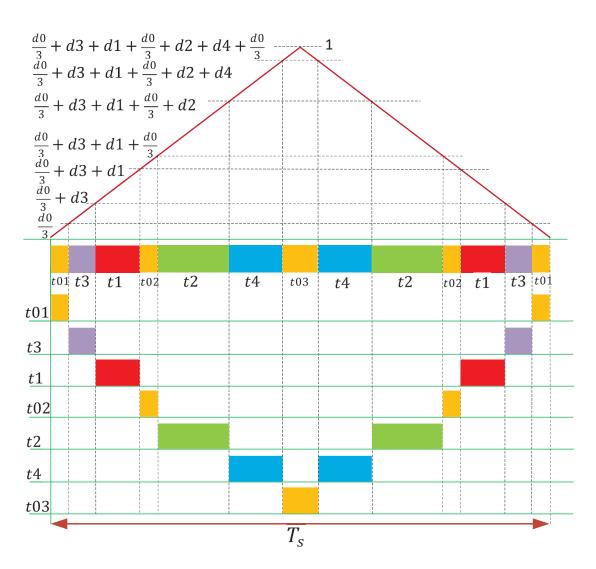

| Figure 3.10 Generation of symmetrically distributed switching pulses, where         |    |

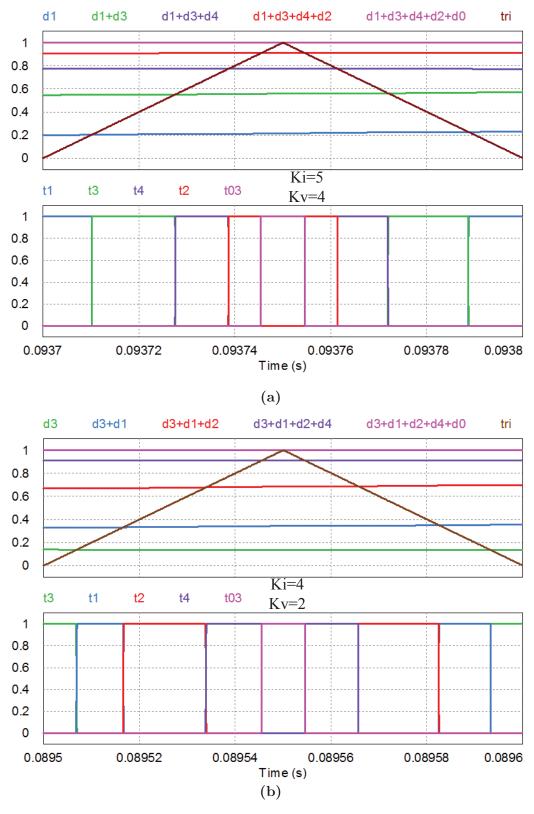

| a) When $k_i + k_v$ is odd, and b) When $k_i + k_v$ is even                         | 74 |

| Figure 3.11 Generation of symmetrically distributed switching pulses, time          |    |

| duration of each switching configuration for a switching sequence with              |    |

| period $T_s$ When $k_i + k_v$ is even                                               | 75 |

| Figure 3.12 Simulation results of time duration of each switching config-           |    |

| uration for a switching sequence with period $T_s$ When $k_i + k_v$ is: a)          |    |

| odd, and b) even $\ldots$                                                           | 77 |

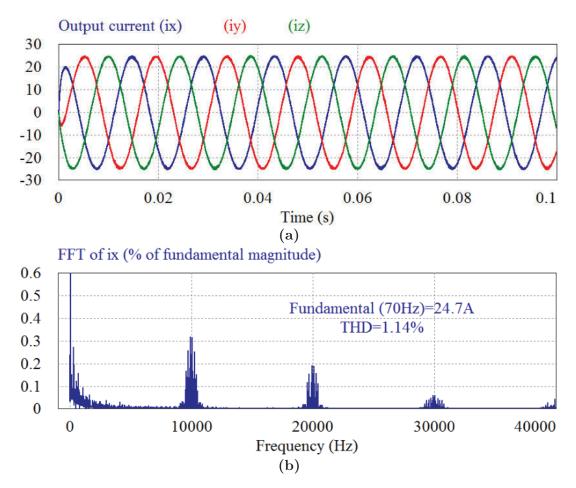

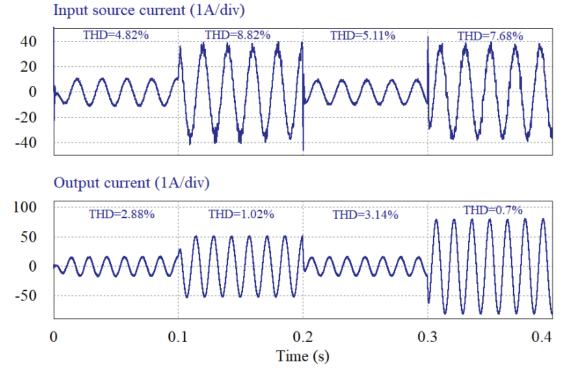

| Figure 3.13 Simulation results of DSVM when $v_{o,ref} = 330V(L - to - L)$ ,        |    |

| where a) Three-phase output currents, and b) Frequency spectrum of                  |    |

| $i_x$                                                                               | 78 |

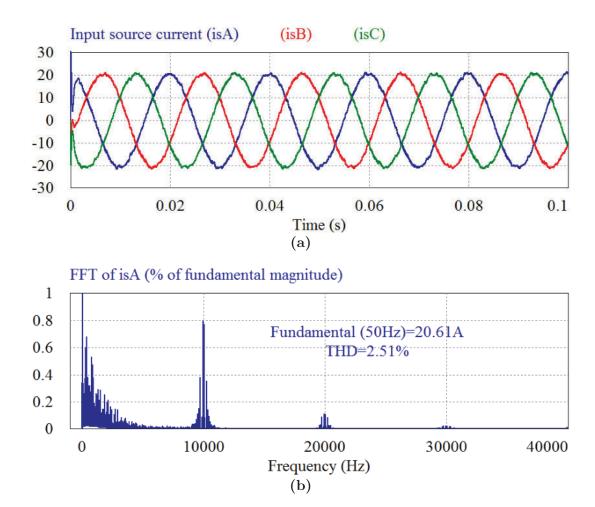

| Figure 3.14 Simulation results of DSVM with $v_{o,ref} = 330V(L-L)$ , where         |    |

| a) Three-phase input source currents, and b) Frequency spectrum of                  |    |

| $i_{sA}$                                                                            | 79 |

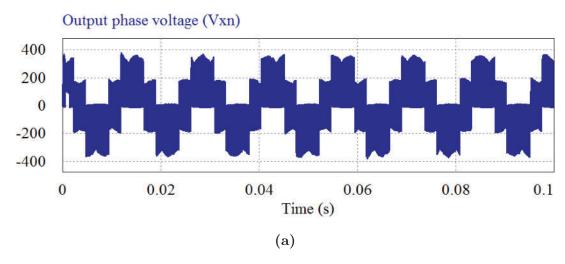

| Figure 3.15 Simulation results of DSVM with $v_{o,ref} = 330V(L-L)$ , where         |    |

| a) Output phase voltage $v_{xn}$ , and b) Frequency spectrum of $v_{xn}$            | 80 |

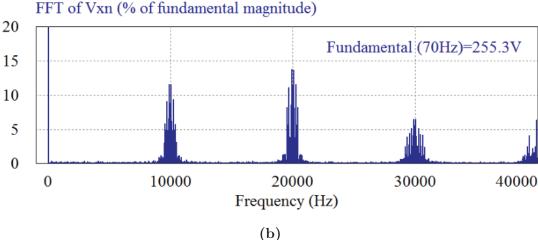

| Figure 3.16 Simulation results of DSVM with $v_{o,ref} = 330V(L-L)$ , where                                                    |

|--------------------------------------------------------------------------------------------------------------------------------|

| a) Input phase voltage $v_A$ , b) Output line voltage $v_{xy}$ , c) Output                                                     |

| phase voltage with respect to the input neutral point $v_{xN}$ , and d)                                                        |

| Common mode voltage                                                                                                            |

| Figure 3.17 Simulation results when output reference voltage (line-line) is:                                                   |

| a) $v_{o,ref} = 330V$ , b) $v_{o,ref} = 200V$ , and c) $v_{o,ref} = 80V$ 82                                                    |

| Figure 3.18 Simulation results of DSVM with $v_{o,ref} = 330VL - L$ and                                                        |

| $f_o = 30Hz \dots \dots$ |

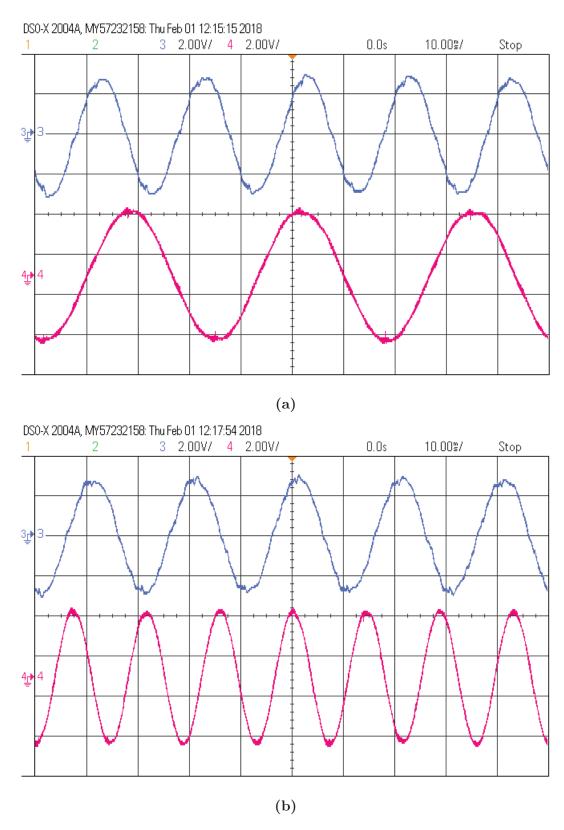

| Figure 3.19 Experimental results of DSVM when $q = 0.86, f_i = 50Hz, f_o =$                                                    |

| 60Hz, where a) Three-phase input source currents, and b) Input                                                                 |

| source current $i_{sB}$ and its frequency spectrum                                                                             |

| Figure 3.20 Experimental results of DSVM, input source current $i_{sB}$ and                                                    |

| output current $i_y$ when $q = 0.86$ and $f_i = 50Hz$ , where a) $f_o = 30Hz$ ,                                                |

| and b) $f_o = 70Hz$                                                                                                            |

| Figure 3.21 Experimental results of DSVM, input source current $i_{sB}$ and                                                    |

| output current $i_y$ when $f_i = 50Hz$ and $f_o = 60Hz$ , where a) $q = 0.86$ ,                                                |

| and b) $q = 0.5 \dots 86$                                                                                                      |

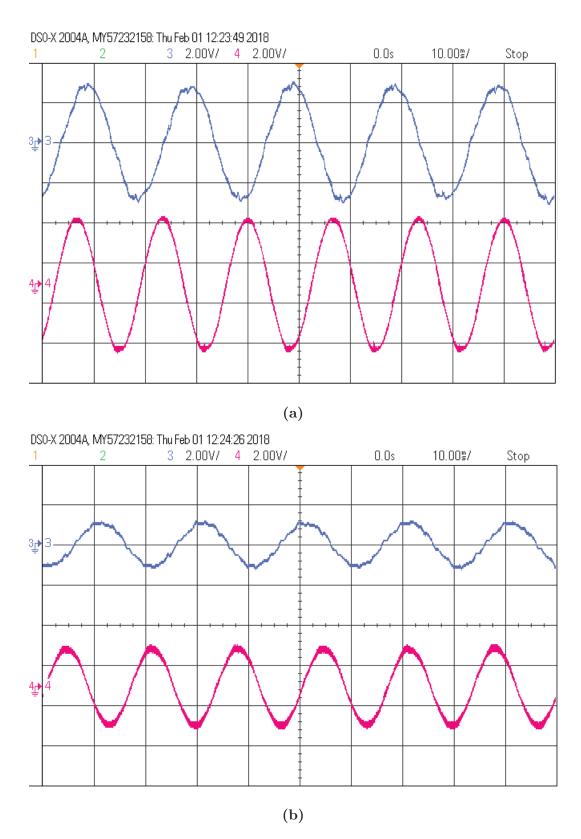

| Figure 3.22 Experimental results of DSVM, when $q=0.86,\ f_i=50Hz$                                                             |

| and $f_o = 60Hz$ , where a) input source current and voltage $i_{sB}$ and                                                      |

| $v_{sB}$ , and b) input source voltage $v_{sB}$ and its frequency spectrum 87                                                  |

| Figure 3.23 Experimental results of DSVM when $q = 0.86, f_i = 50 Hz and f_o =$                                                |

| 60Hz, where a) Three-phase output currents, and b) Output current                                                              |

| $i_y$ and its frequency spectrum                                                                                               |

| Figure 3.24 Experimental results of DSVM when $q = 0.86, f_i = 50 Hz and f_o =$                                                |

| $60Hz$ , where a) Output phase voltage $v_{yN}$ and its spectrum, and b)                                                       |

| Output line-to-line voltage $v_{xy}$ and its spectrum 89                                                                       |

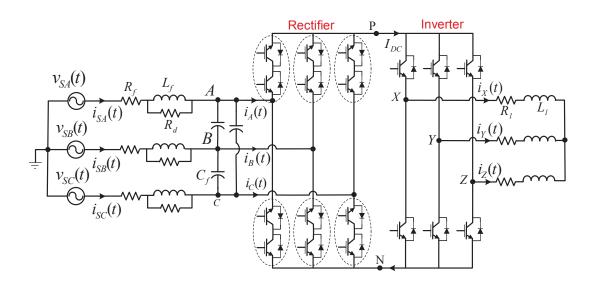

| Figure 3.25 IMC with an RLC filter and a three-phase RL load 90                                                                |

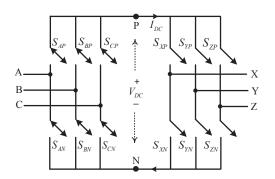

| Figure 3.26 The schematic diagram of ideal IMC 91                                                                              |

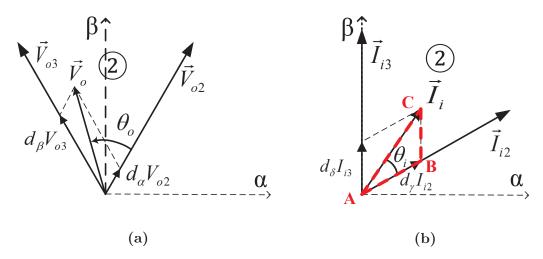

| Figure 3.27 IMC space vectors of a) The output voltage b) The input current 93                                                 |

| Figure 3.28 Synthesising the output reference voltage and input current                                                        |

| vectors by two adjacent space vectors in a given sector 95                                                                     |

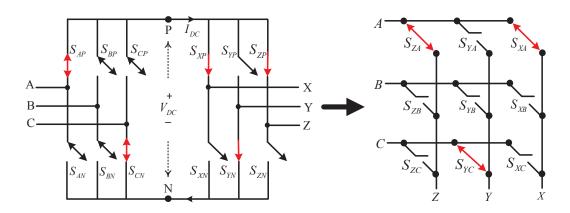

| Figure 3.29 Graphical representation of the switch states of IMC and its                                                       |

| equivalent circuit in DMC                                                                                                      |

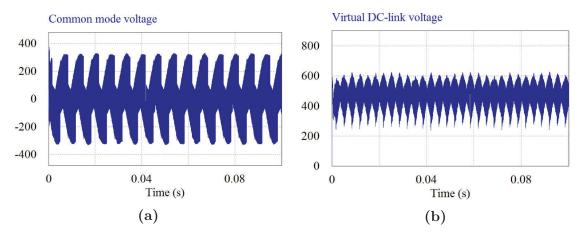

| Figure 3.30 Simulation results of IMC, where a) Common mode voltage,                                                           |

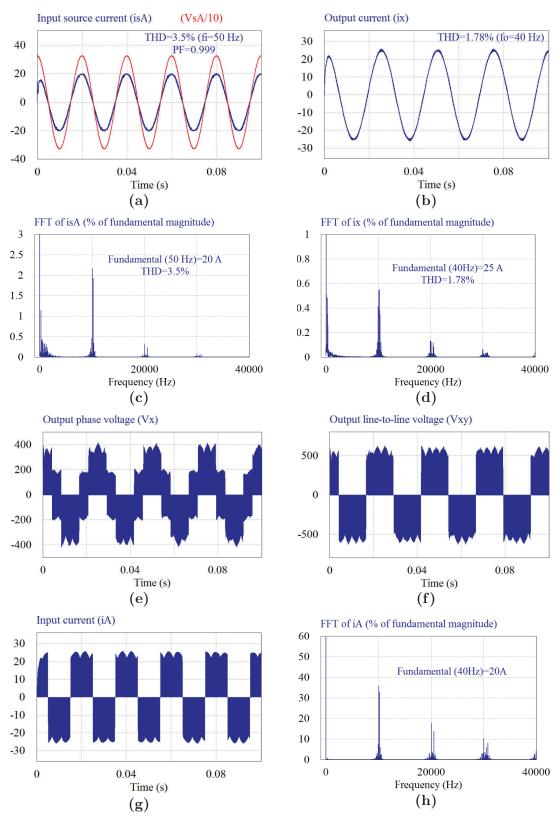

| and b) Virtual dc-link voltage $V_{DC}$                                                                                        |

| Figure 3.31 Si   | mulation results of IMC, where a) Input source current and                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| voltage $i$      | $s_A$ and $v_{sA}$ , b) Output current $i_x$ , c) Frequency spectrum                                                                                 |

| of $i_{sA}$ , d) | Frequency spectrum of $i_x$ , e) Output phase voltage $v_x$ , f)                                                                                     |

| Output li        | ine-to-line voltage $v_{xy}$ , g) Input current $i_A$ , and h) Frequency                                                                             |

| spectrum         | of input current $i_A$                                                                                                                               |

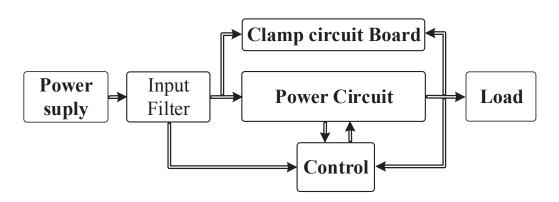

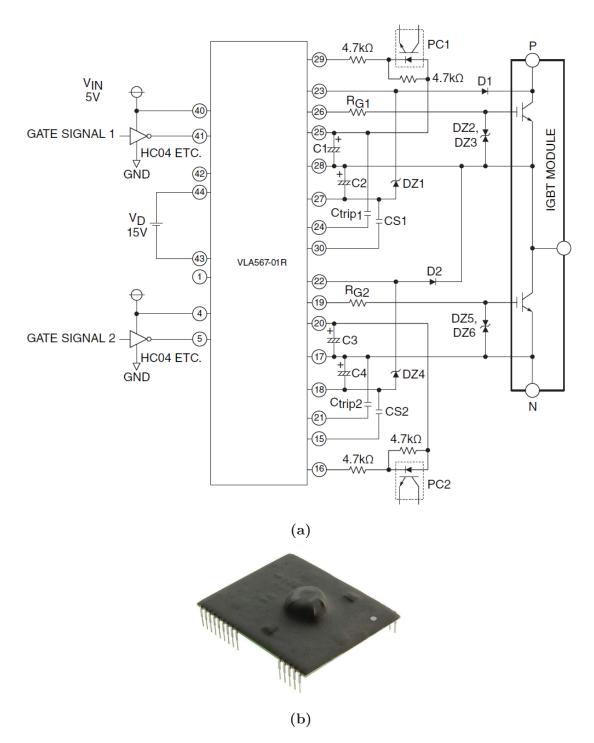

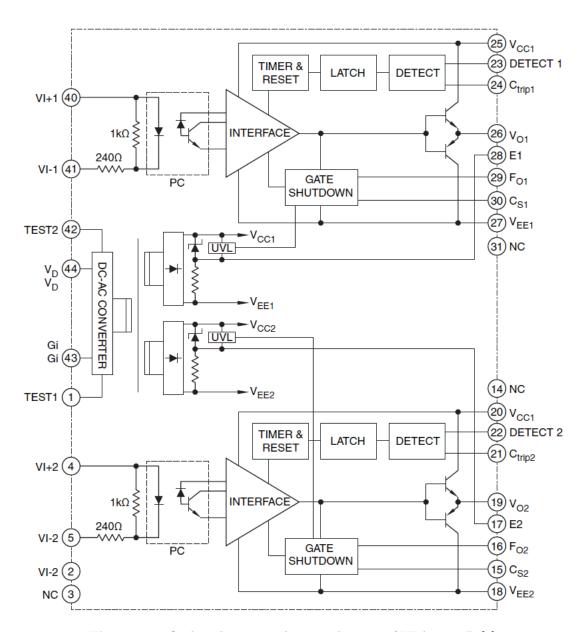

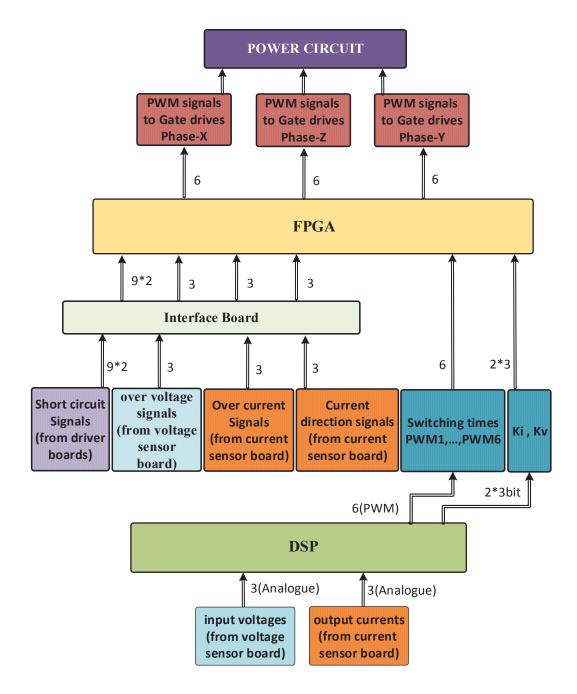

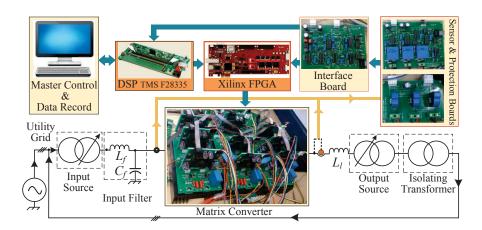

| Figure 4.1 B     | lock diagram of the overall structure of the designed DMC $$ . $105$                                                                                 |

| Figure 4.2 B     | lock diagram of the overall structure of the control plan $$ $106$                                                                                   |

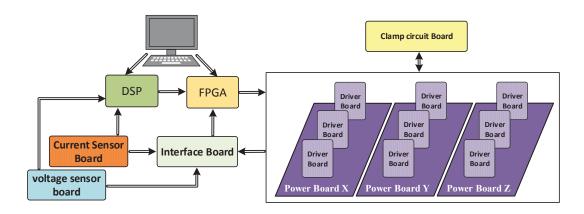

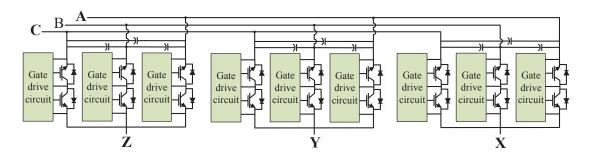

| Figure 4.3 T     | he schematic of the power module with driver boards $\dots$ 107                                                                                      |

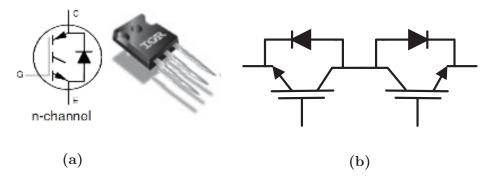

| Figure 4.4 IC    | GBT switch, where a) TO-247ADIRG7PH42UD1-EP, and b)                                                                                                  |

| Schemati         | c of a single bidirectional-switch                                                                                                                   |

| Figure 4.5 D     | Priver integrated circuit, where a) Schematic of the driver                                                                                          |

| board us         | ing VLA567-01R driver integrated circuit, and b) VLA567-                                                                                             |

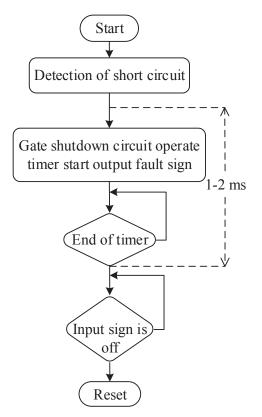

| 01R drive        | er integrated circuit [6]                                                                                                                            |

| Figure 4.6 O     | utline drawing and circuit diagram of VLA567-01R [6] 110 $$                                                                                          |

| Figure 4.7 O     | peration flowchart on detecting short circuit [6] 111                                                                                                |

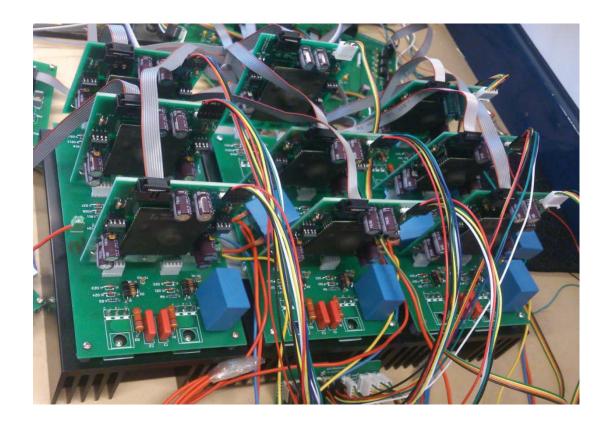

| Figure 4.8 Pl    | hotograph of the power boards with the driver boards on them $112$                                                                                   |

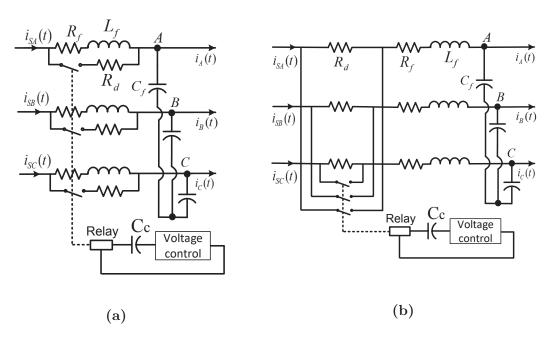

| Figure 4.9 So    | chematic of the input filter circuit with damping resistors in                                                                                       |

| parallel v       | with the filter inductances                                                                                                                          |

| Figure 4.10 Se   | econd order LC filter with bypass relays for preventing of                                                                                           |

| more pov         | ver loss, and damping resistors, where a) in parallel, and b)                                                                                        |

| in series        | with the inductors                                                                                                                                   |

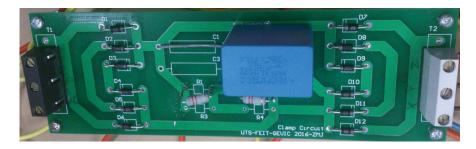

| Figure 4.11 So   | chematic of the clamp circuit                                                                                                                        |

| Figure 4.12 P    | hotograph of the clamp circuit                                                                                                                       |

| Figure 4.13 T    | MS320F28335 Experimenter Kit [7] $\dots \dots \dots$ |

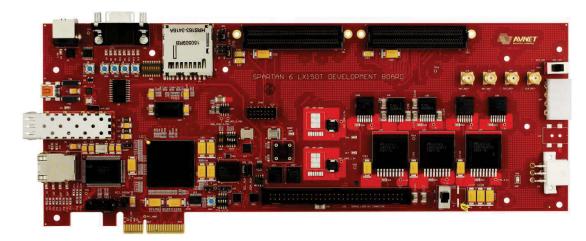

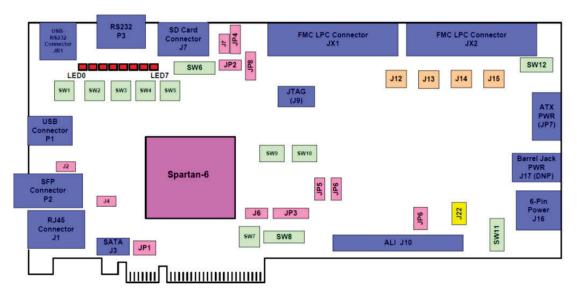

| Figure 4.14 X    | ILINX Spartan-6 LX150T Development Board used for this                                                                                               |

| prototype        | e [8]                                                                                                                                                |

| Figure 4.15 X    | ILINX Spartan-6 LX150T development board main compo-                                                                                                 |

| nents [8]        |                                                                                                                                                      |

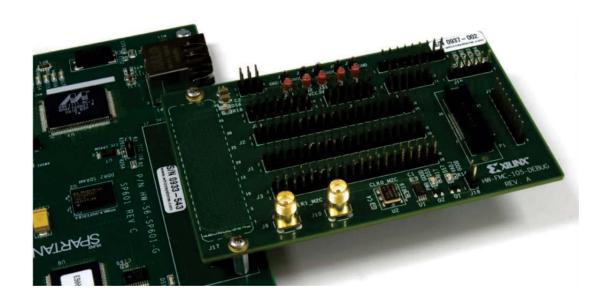

| Figure 4.16 In   | stallation of Mezzanine Card to Board FMC Connector $[9]$ . 118                                                                                      |

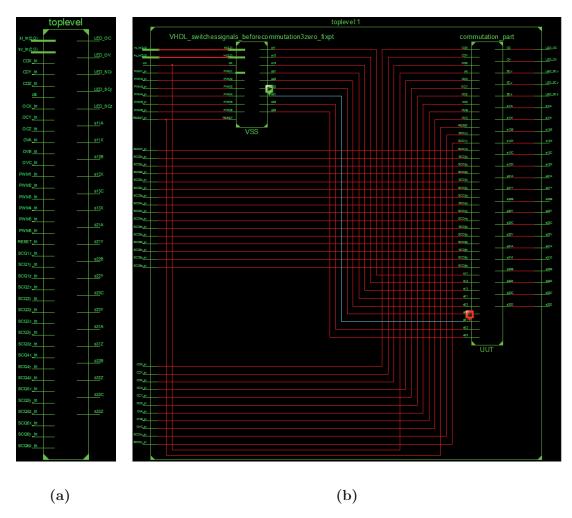

| Figure 4.17 T    | he control algorithm in the FPGA, where a) Top-level block,                                                                                          |

| and b) In        | nside the top-level block                                                                                                                            |

| Figure 4.18 O    | verall structure of the control platform                                                                                                             |

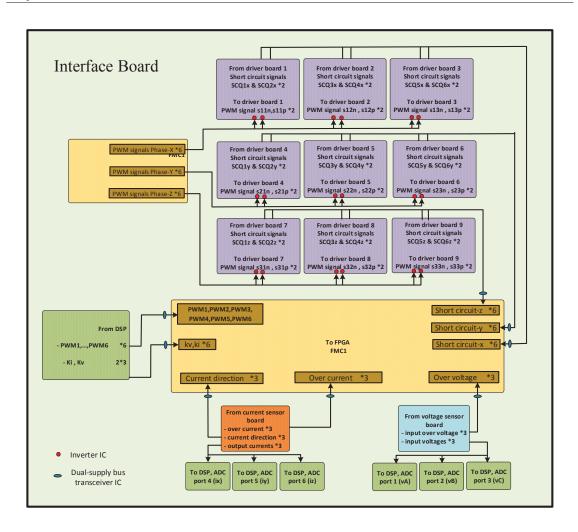

| Figure 4.19 O    | verall structure of the interface board                                                                                                              |

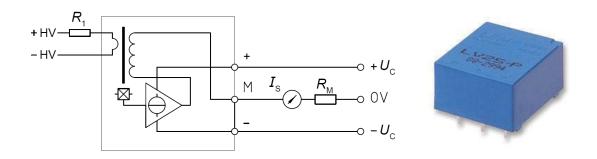

| Figure 4.20 V    | oltage transducer LV 25-P [10]                                                                                                                       |

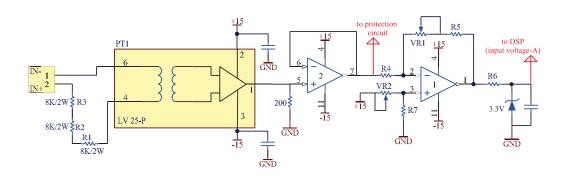

| Figure 4.21 | Schematic of the voltage measurement circuit                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

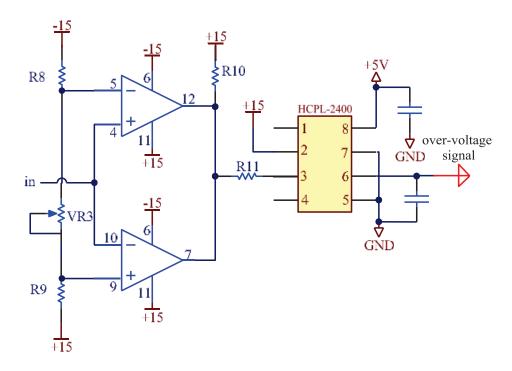

| Figure 4.22 | Schematic of the over-voltage protection circuit $\dots \dots \dots$ |

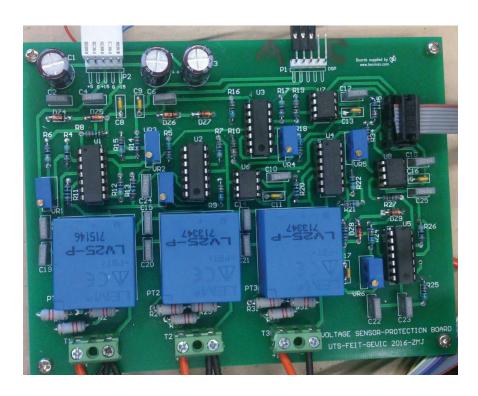

| Figure 4.23 | The voltage measurement and protection board $\dots \dots 124$                                                                                                       |

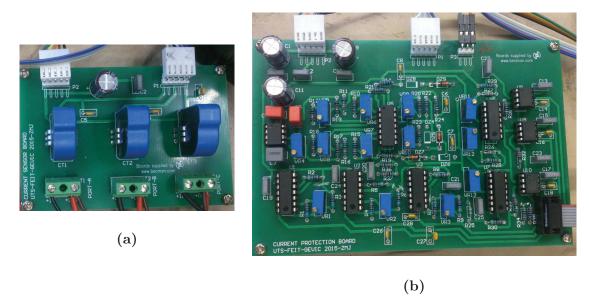

| Figure 4.24 | Prototype current measurement board, where a) Current sen-                                                                                                           |

| sor boa     | ard, and b) Current measurement and protection circuits $124$                                                                                                        |

| Figure 4.25 | Current transducer LTSR 25-N [11] $\ \ldots \ \ldots \ \ldots \ \ldots \ 125$                                                                                        |

| Figure 4.26 | Input-output characteristic of the current transducer LTSR                                                                                                           |

| 25-N [      | 11]                                                                                                                                                                  |

| Figure 4.27 | Schematic of the over-current protection circuit $\dots \dots 126$                                                                                                   |

| Figure 4.28 | Current direction measurement circuit                                                                                                                                |

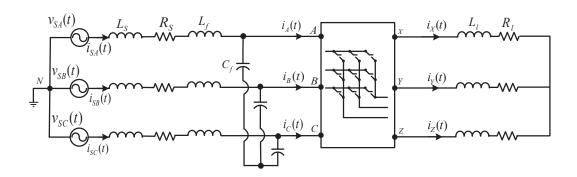

| Figure 5.1  | Schematic of the DMC with LC input filter and RL load $$ 132                                                                                                         |

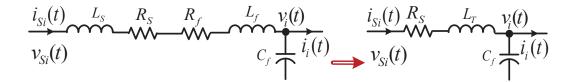

| Figure 5.2  | The single-phase model of the input low-pass LC filter $$ 132                                                                                                        |

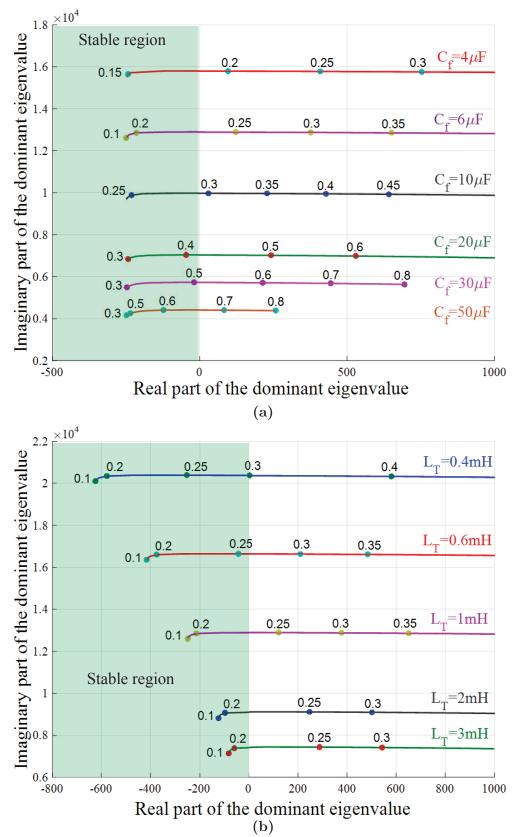

| Figure 5.3  | Position of the dominant eigenvalue of the state matrix A in                                                                                                         |

| the co      | mplex plane as a function of the voltage gain $q$ , where a) For                                                                                                     |

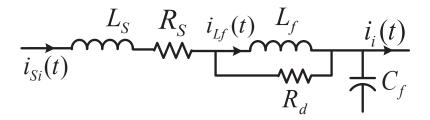

| differe     | nt values of $C_f$ , and b) For different values of $L_T$                                                                                                            |

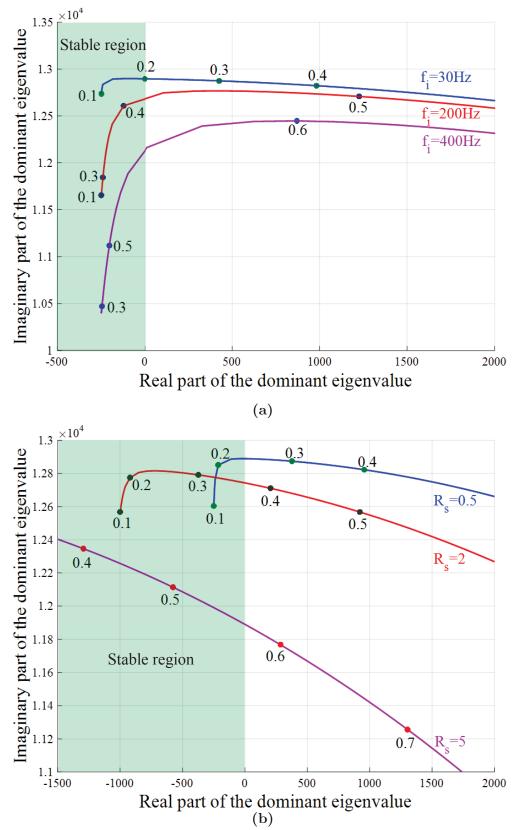

| Figure 5.4  | Position of the dominant eigenvalue of the state matrix A in                                                                                                         |

| the con     | mplex plane as a function of the voltage gain $q$ , where a) For                                                                                                     |

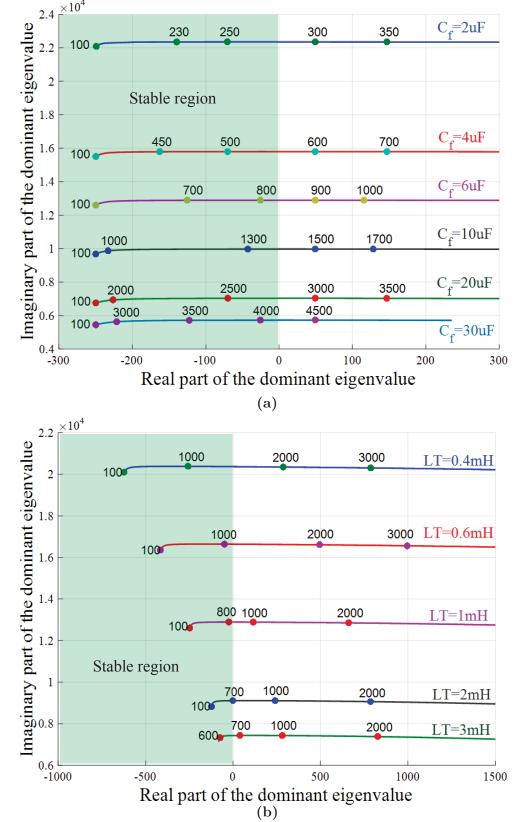

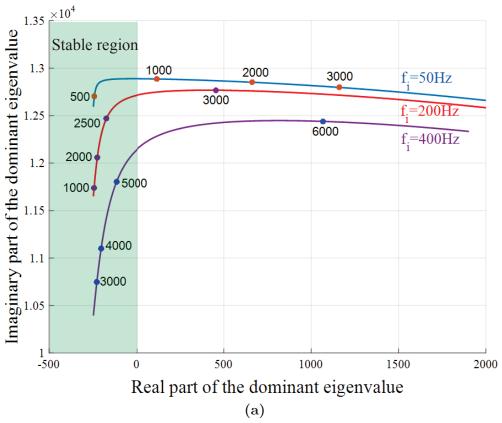

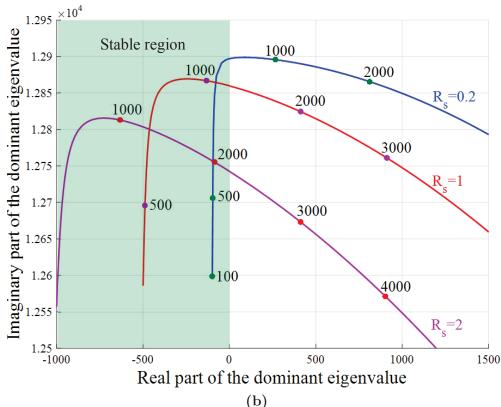

| differe     | nt values of $f_i$ , and b) For different values of $R_s$                                                                                                            |

| Figure 5.5  | Position of the dominant eigenvalue of the state matrix A in                                                                                                         |

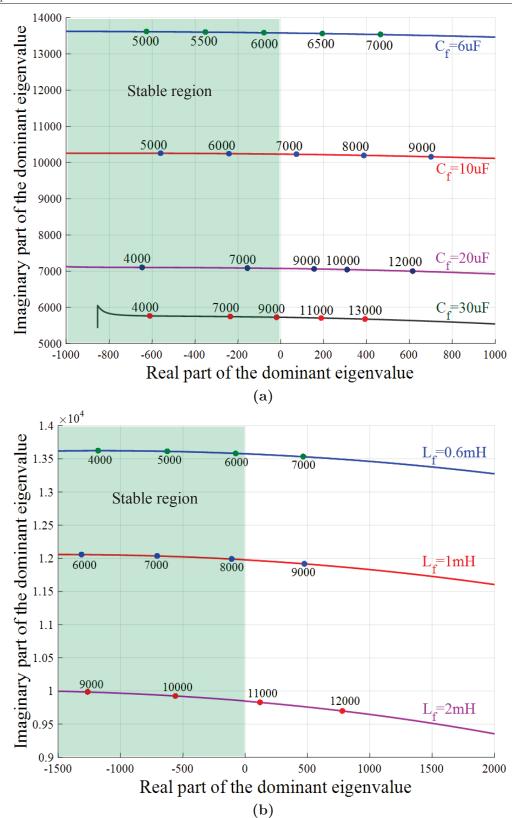

|             | mplex plane as a function of the output power $p_o$ , where a) For                                                                                                   |

| differe     | nt values of $C_f$ , and b) For different values of $L_T$                                                                                                            |

| 0           | Position of the dominant eigenvalue of the state matrix A in                                                                                                         |

|             | mplex plane as a function of the output power $p_o$ , where a) For                                                                                                   |

|             | nt values of $f_i$ , and b) For different values of $R_s$                                                                                                            |

|             | Schematic of the low-pass LC filter with the parallel damping                                                                                                        |

| resisto     | r                                                                                                                                                                    |

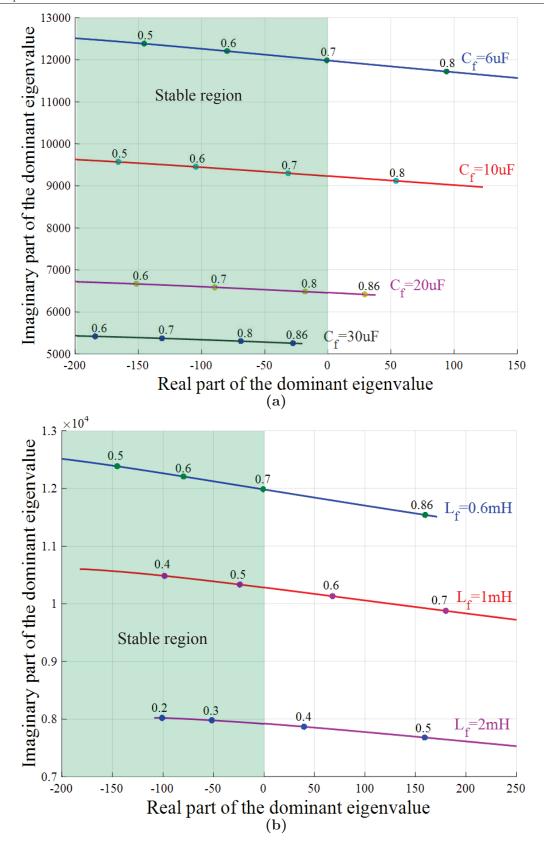

| Figure 5.8  | Position of the dominant eigenvalue of the state matrix $A_{d1}$ in                                                                                                  |

| the co      | mplex plane as a function of the output power po with $R_d =$                                                                                                        |

|             | where a) For different values of $C_f$ , and b) For different values                                                                                                 |

| of $L_f$    |                                                                                                                                                                      |

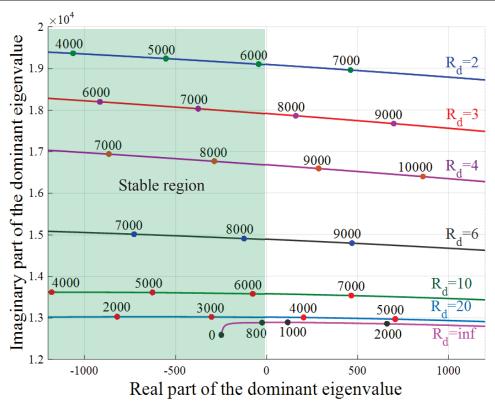

|             | Position of the dominant eigenvalue of the state matrix $A_{d1}$ in                                                                                                  |

|             | mplex plane as a function of the output power $p_o$ for different                                                                                                    |

| values      | of $R_d$                                                                                                                                                             |

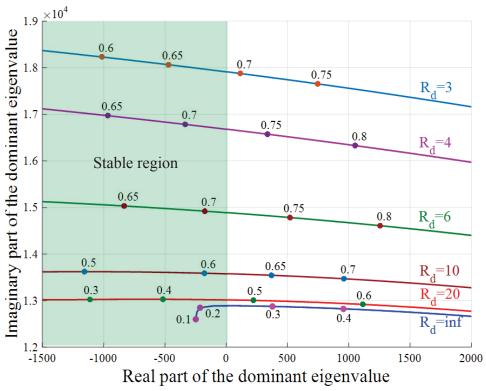

| Figure 5.10 Position of the dominant eigenvalue of the state matrix $A_{d2}$                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| in the complex plane as a function of the voltage gain $q$ for different                                                                            |

| values of $R_d$                                                                                                                                     |

| Figure 5.11 Position of the dominant eigenvalue of the state matrix $A_{d2}$ in                                                                     |

| the complex plane as a function of the voltage gain q with $R_d = 10\Omega$ ,                                                                       |

| where a) For different values of $C_f$ , and b) For different values of $L_f$ . 154                                                                 |

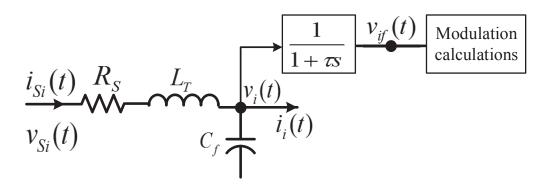

| Figure 5.12 Block diagram of the single-phase input filter with a digital                                                                           |

| low-pass filter                                                                                                                                     |

| Figure 5.13 Position of the dominant eigenvalue of the state matrix $A_f$ in                                                                        |

| the complex plane as a function of the voltage gain $q$ , where a) For                                                                              |

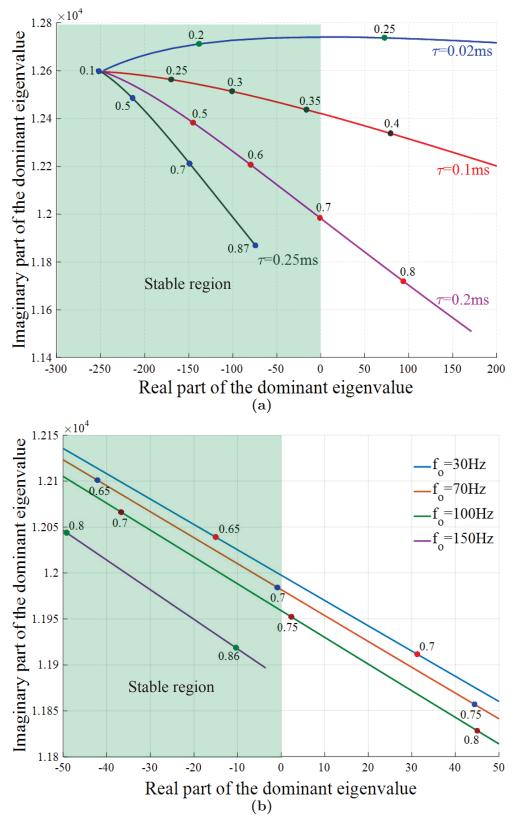

| different values of $\tau$ , and b) For different values of $f_o$ when $\tau = 0.2ms$ 159                                                           |

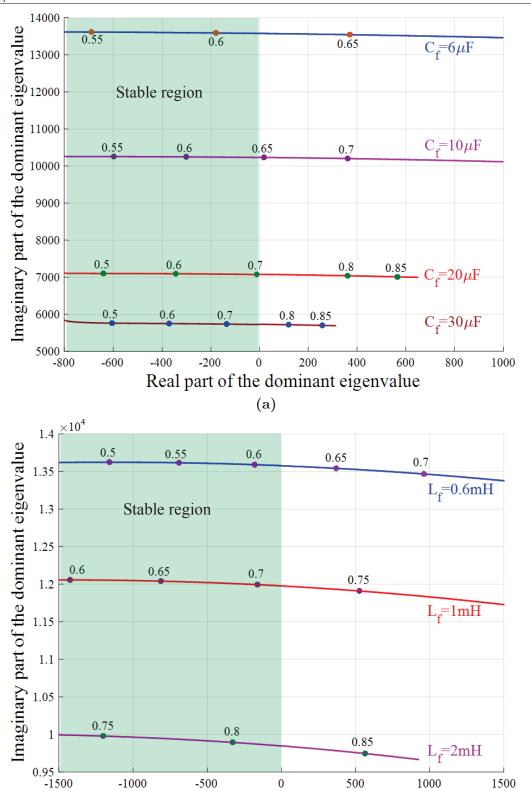

| Figure 5.14 Position of the dominant eigenvalue of the state matrix $A_f$ in                                                                        |

| the complex plane as a function of the voltage gain $q$ when $\tau = 0.2ms$ ,                                                                       |

| where a) For different values of $C_f$ , and b) For different values of $L_f$ . 160                                                                 |

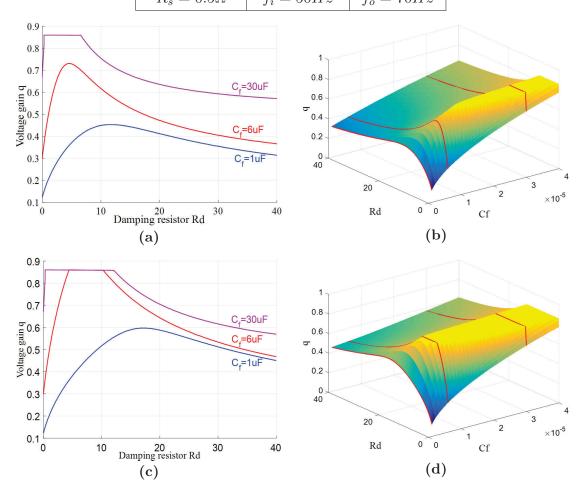

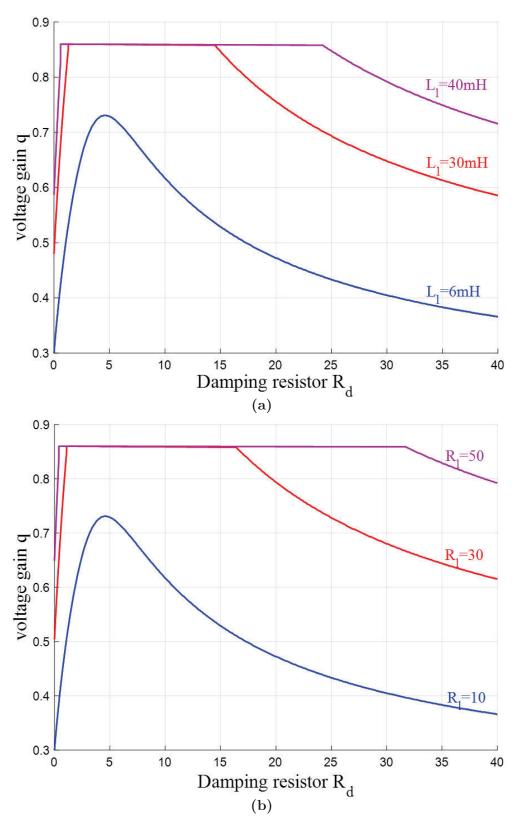

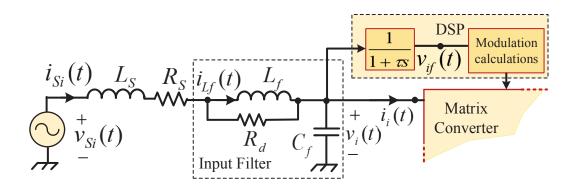

| Figure 6.1. Stability region of the DMC system, voltage gain 'e' against                                                                            |

| Figure 6.1 Stability region of the DMC system, voltage gain 'q' against                                                                             |

| damping resistor $R_d$ , where a) For three different filter-capacitance                                                                            |

| $C_f$ when $L_f = 0.6mH$ , b) 3D graph of the case (a), c) For three different filter capacitance $C_f$ when $L_f = 3mH$ , and d) 3D graph of       |

| the case (c) $\dots \dots \dots$                    |

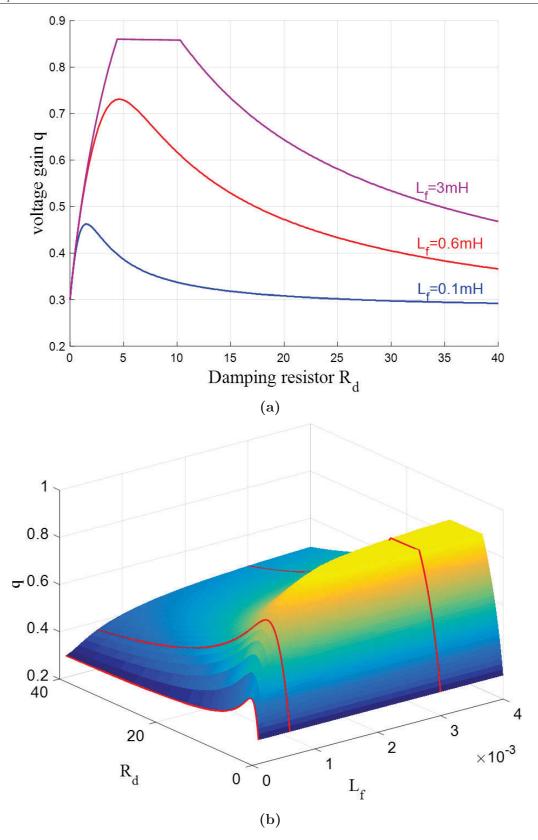

| Figure 6.2 Stability region of the DMC system, voltage gain 'q' against                                                                             |

| damping resistor $R_d$ , where a) For three different filter inductance $L_f$ ,                                                                     |

| and b) 3D graph of the case (a) $\dots \dots \dots$ |

| Figure 6.3 Stability region of the DMC system, voltage gain 'q' against                                                                             |

| damping resistor $R_d$ , where a) For different values of the load induc-                                                                           |

| tance $L_l$ , and b) For different values of the load resistance $R_l$ 167                                                                          |

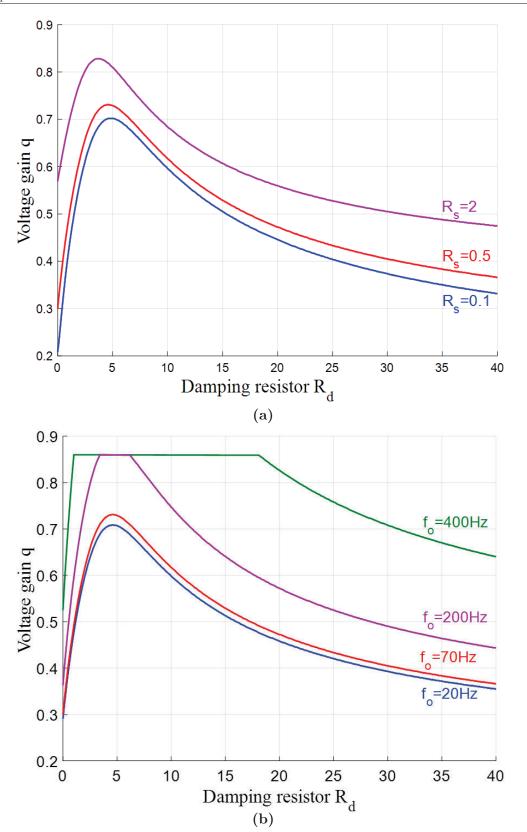

| Figure 6.4 Stability region of the DMC system, voltage gain 'q' against                                                                             |

| damping resistor $R_d$ , where a) For different values of the line resistor                                                                         |

| $R_s$ , and b) For different values of the output frequency $f_o$                                                                                   |

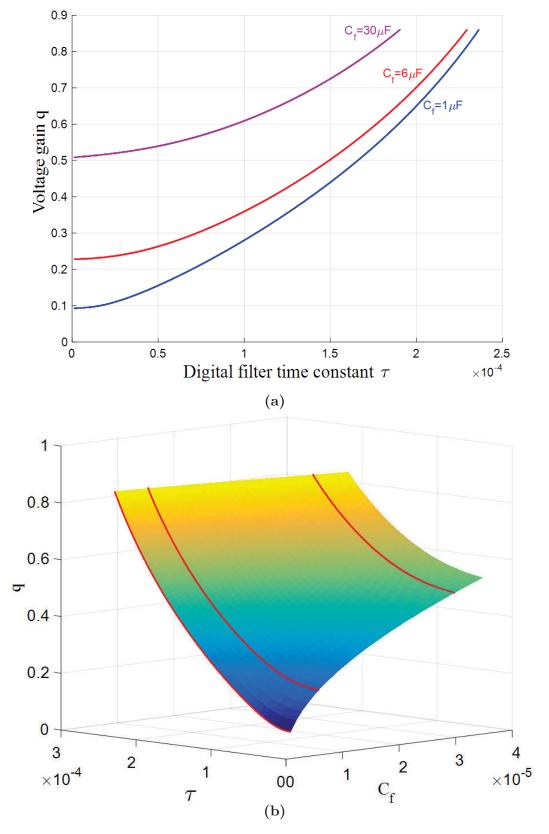

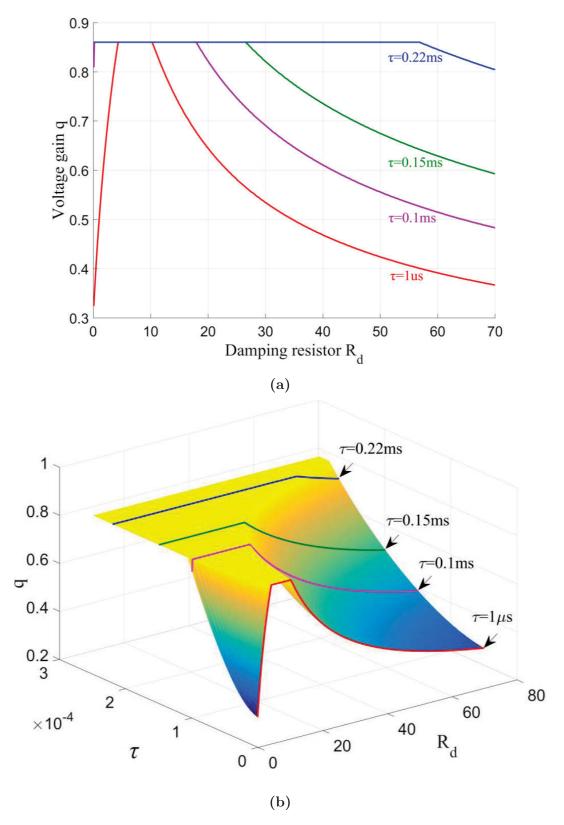

| Figure 6.5 Stability region of the DMC system, voltage gain 'q' against                                                                             |

| input digital filter time constant $\tau$ , where a) For three different filter                                                                     |

| capacitance $C_f$ , and b) 3D graph of the case (a)                                                                                                 |

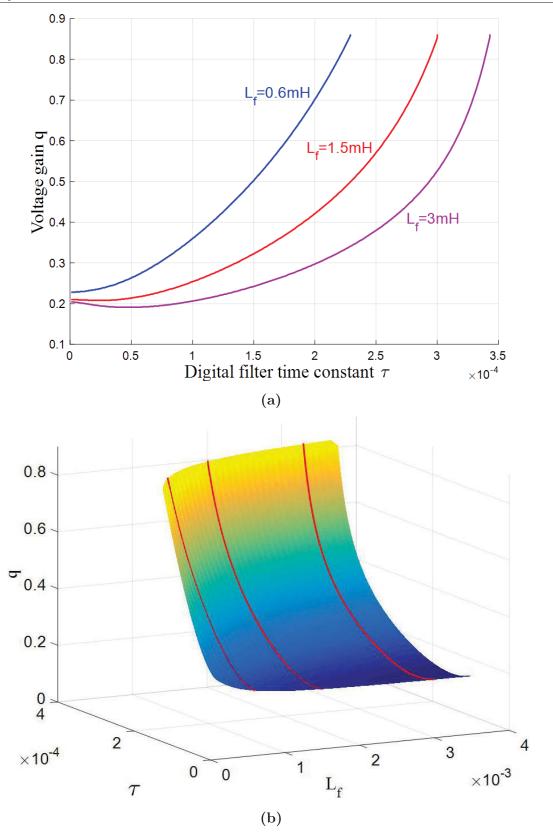

| Figure 6.6 Stability region of the DMC system, voltage gain 'q' against                                                                             |

| input digital filter time constant $\tau$ , where a) For three different filter                                                                     |

| inductance $L_f$ , and b) 3D graph of the case (a)                                                                                                  |

| $\Sigma_j$ , and $\Sigma_j$ 3D graph of the case $(\alpha_j, \ldots, \alpha_j, \ldots, \alpha_j)$                                                   |

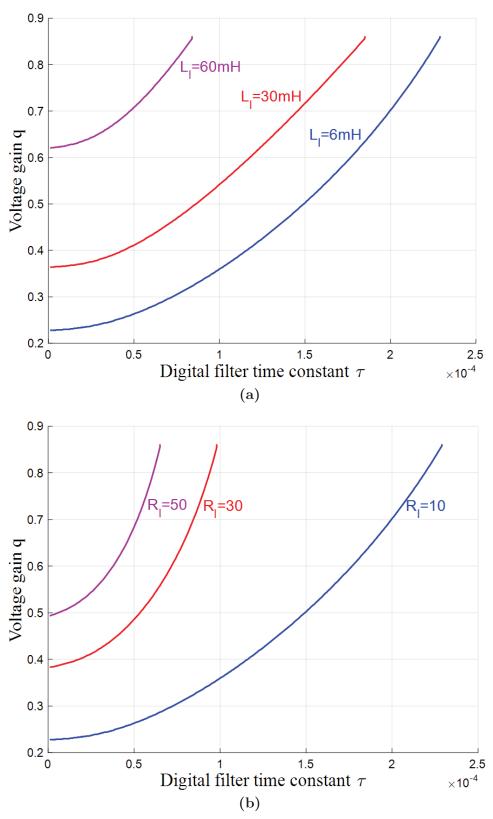

| Figure 6.7 Stability region of the DMC system, voltage gain 'q' against input digital filter time constant $\tau$ , where a) For different values of the load inductance $L_l$ , and b) For different values of the load resistance $R_l$ 173                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.8 Stability region of the DMC system, voltage gain 'q' against input digital filter time constant $\tau$ , where a) For different values of the line resistance $R_s$ , and b) For different values of the output frequency $f_o \dots \dots$                 |

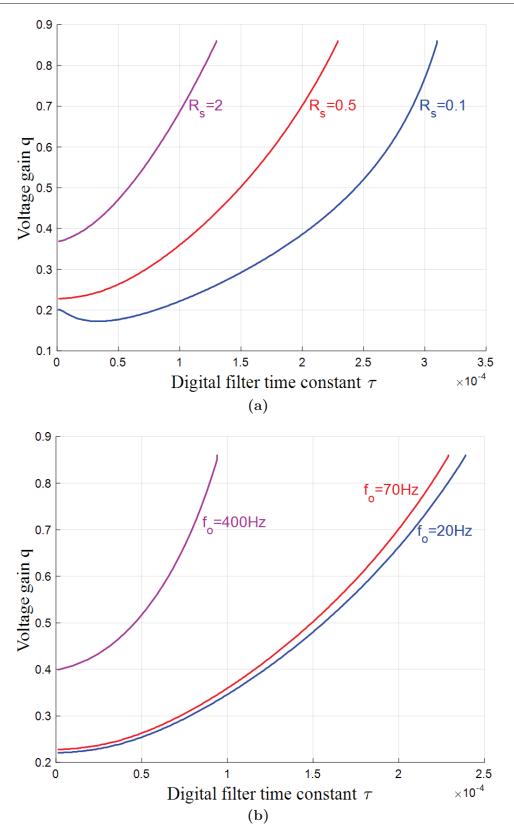

| Figure 6.9 Block diagram of one of the input phases with a digital low-pass filter and the damping resistor                                                                                                                                                                                                                                                                  |

| Figure 6.10 Stable region of the DMC system, voltage gain 'q' against $R_d$ , where a) For different values of $\tau$ , and b) 3D graph of the case (a) 180                                                                                                                                                                                                                  |

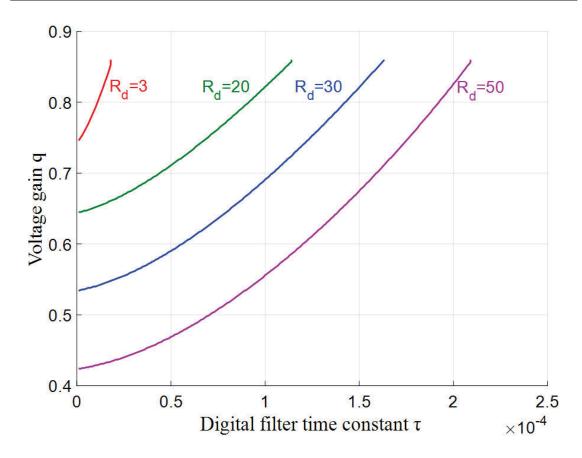

| Figure 6.11 Stable region of the DMC system, voltage gain 'q' against digital filter time constant $\tau$ for different values of damping resistor $R_d$ 18.                                                                                                                                                                                                                 |

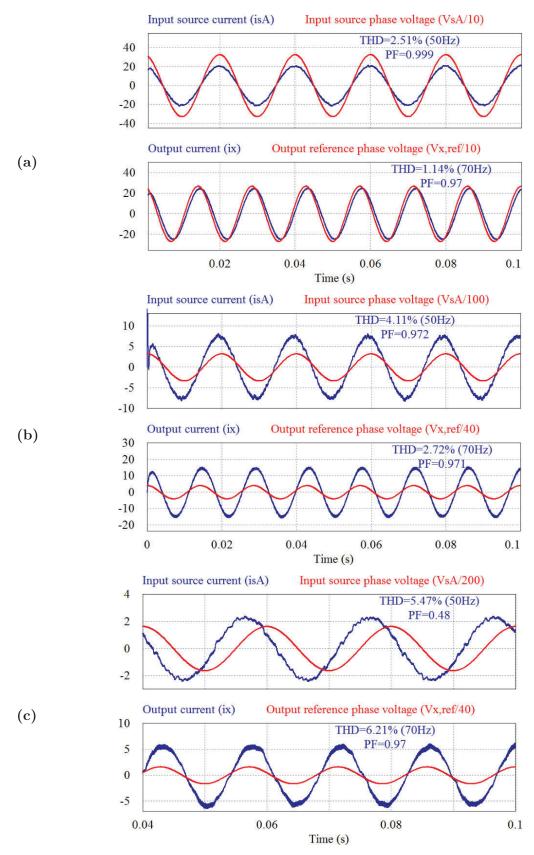

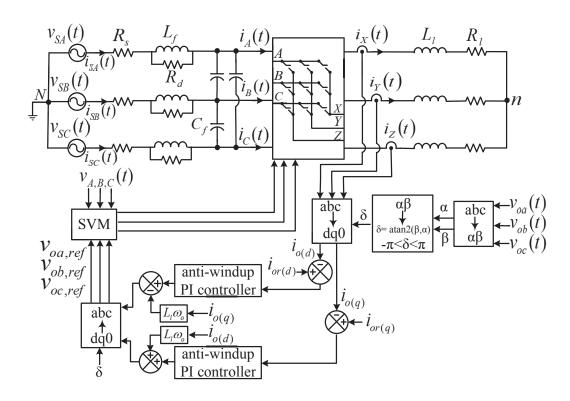

| Figure 6.12 Unidirectional output power control using the voltage oriented control                                                                                                                                                                                                                                                                                           |

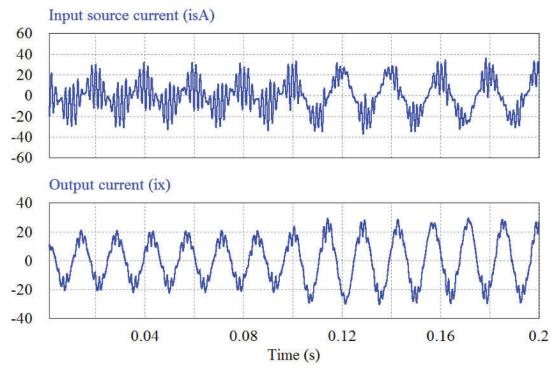

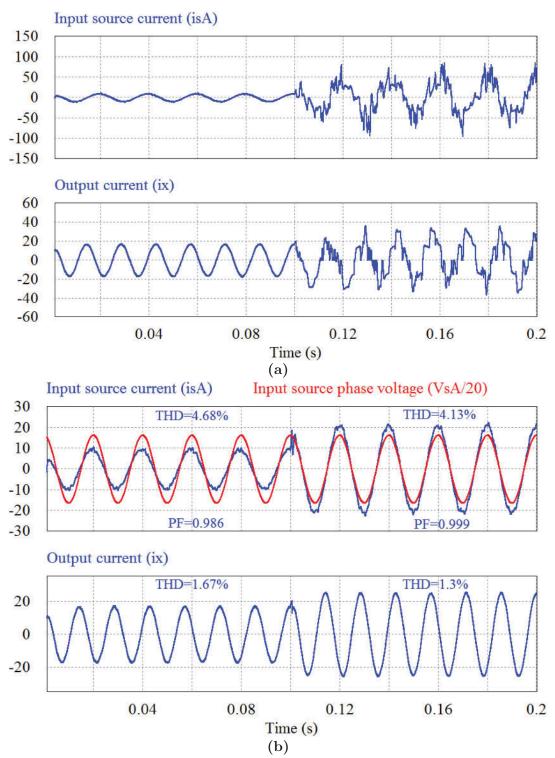

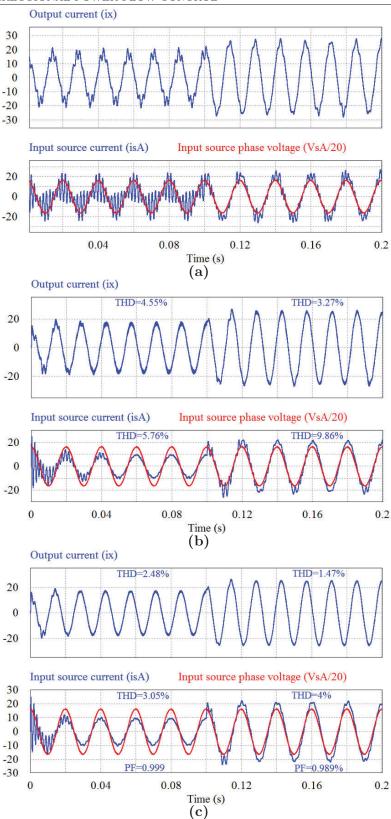

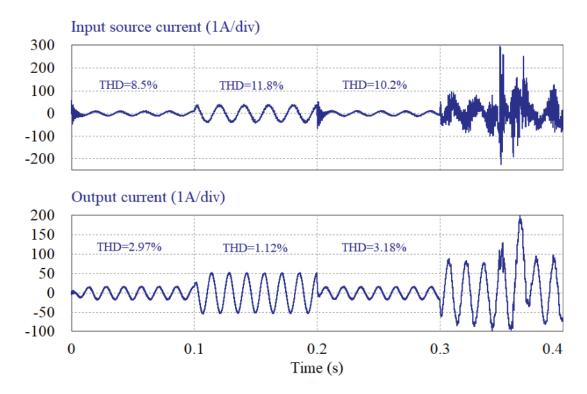

| Figure 6.13 Waveforms of the input source current and the output current for the unidirectional power flow, without applying any stabilisation method                                                                                                                                                                                                                        |

| Figure 6.14 The input and output waveforms for unidirectional power flow control with $R_d = 5\Omega$                                                                                                                                                                                                                                                                        |

| Figure 6.15 Waveforms of the input source current and the output current for the unidirectional power flow control, with $R_d = 8\Omega$ and switching pattern using three zero vectors, where a) With normal PI controller, and b) With anti-windup PI controller                                                                                                           |

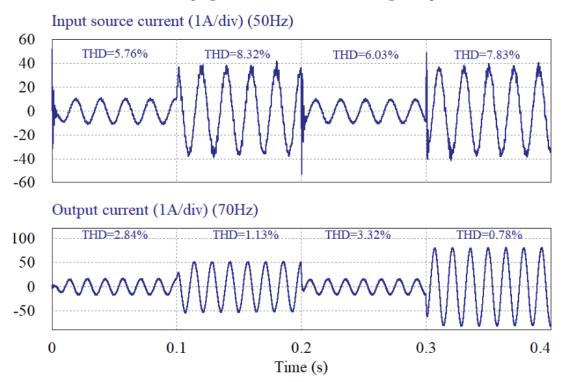

| Figure 6.16 The input and output waveforms for unidirectional power flow control with $R_d = 5\Omega$ , switching pattern using three zero vectors and conventional PI controllers                                                                                                                                                                                           |

| Figure 6.17 Waveforms of the output and input source currents for uni-<br>directional power flow control with switching pattern using one zero<br>vector and digital filter with time constant, where a) $\tau = 0.35ms$ ,<br>switching frequency $f_s = 10kHz$ , b) $\tau = 0.35ms$ and switching<br>frequency $f_s = 5kHz$ , and c) $\tau = 0.5ms$ and switching frequency |

| Figure 6.18 Waveforms of the output and input source currents for uni-                                                                                 |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| directional power flow control with switching pattern using one zero                                                                                   |     |

| vector, damping resistor $R_d = 50\Omega$ and the digital filter time constant                                                                         |     |

| $\tau = 0.5ms \dots \dots$                       | 190 |

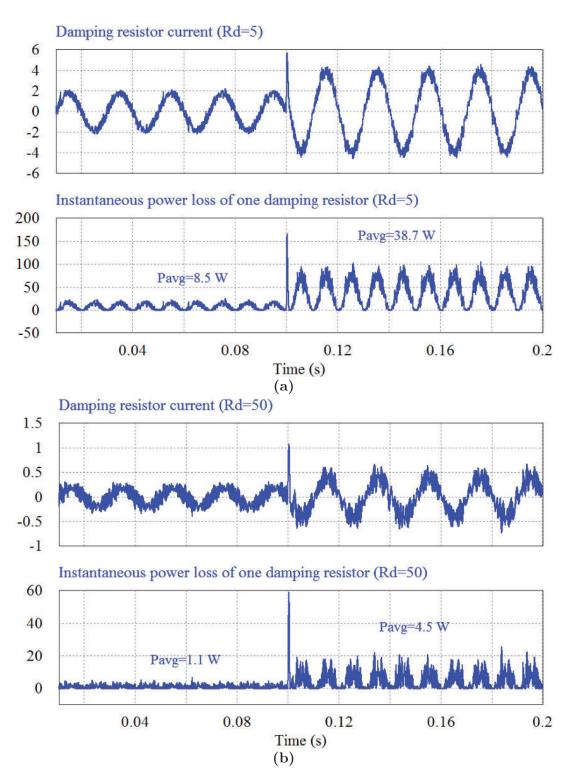

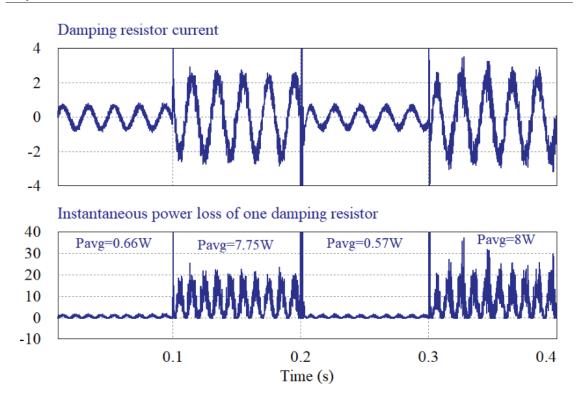

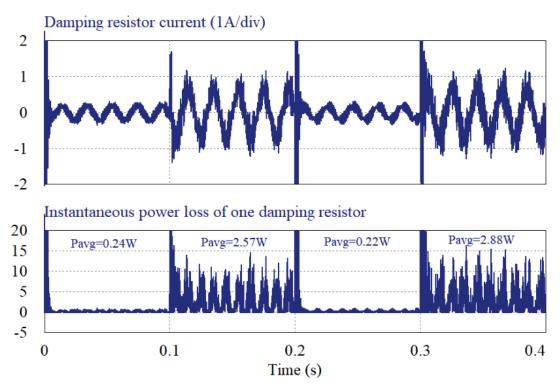

| Figure 6.19 Waveforms of the current and instantaneous power loss in                                                                                   |     |

| a damping resistor for the unidirectional active power-flow control,                                                                                   |     |

| where a) Using only the damping resistor, $R_d = 5\Omega$ , and b) Using the                                                                           |     |

| damping resistor $R_d = 50\Omega$ and digital filter $\tau = 0.5ms$                                                                                    | 191 |

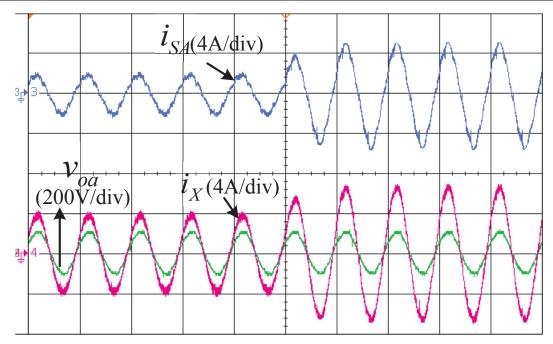

| Figure 6.20 Experimental results for unidirectional active power flow con-                                                                             |     |

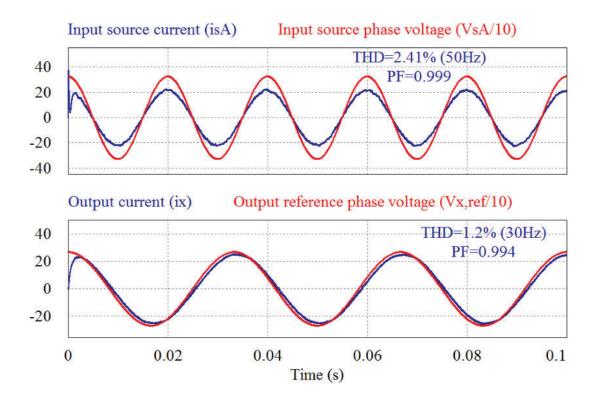

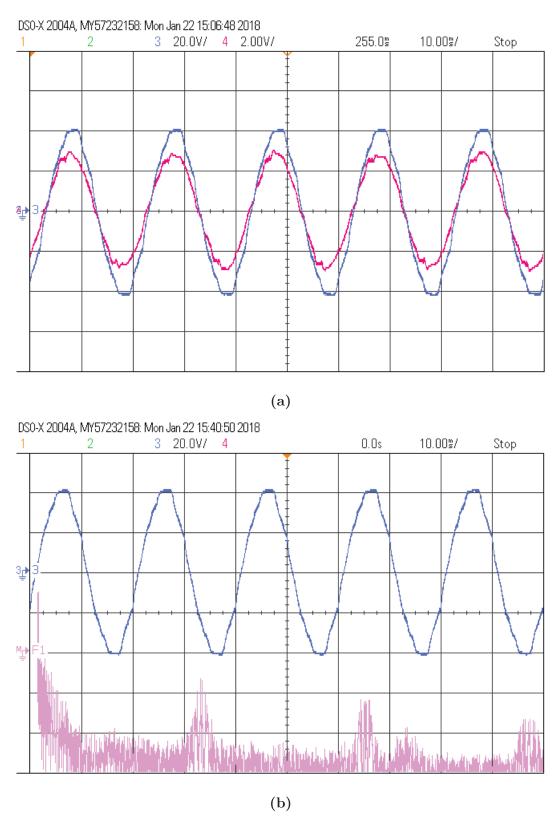

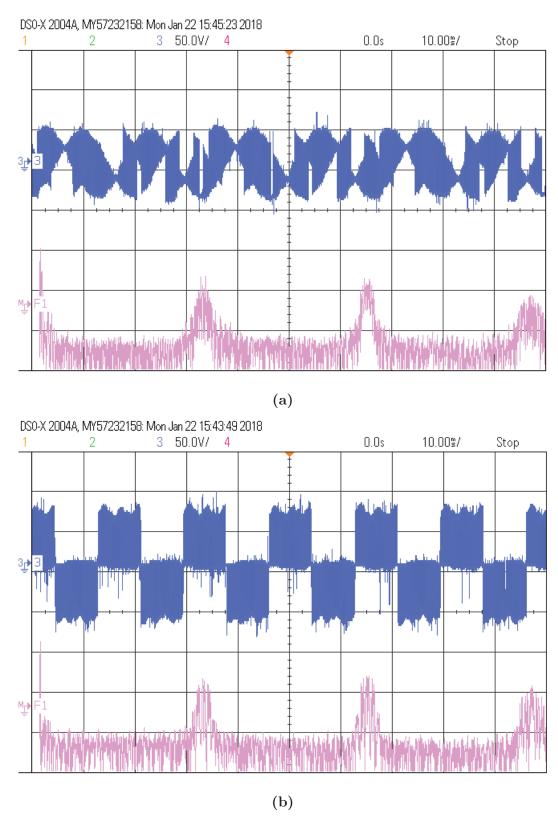

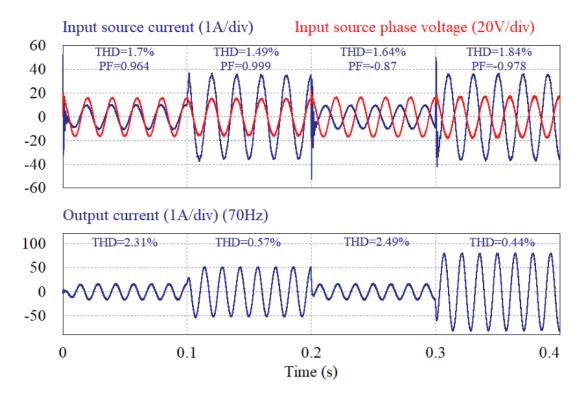

| trol with $R_d = 5\Omega$ , $ior(q) = 0$ and $ior(d)$ steps up from 4A to 7A 1                                                                         | 192 |

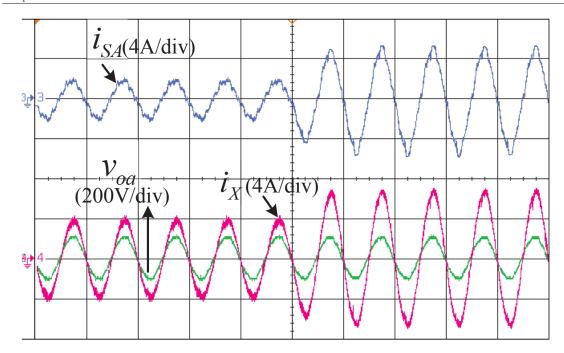

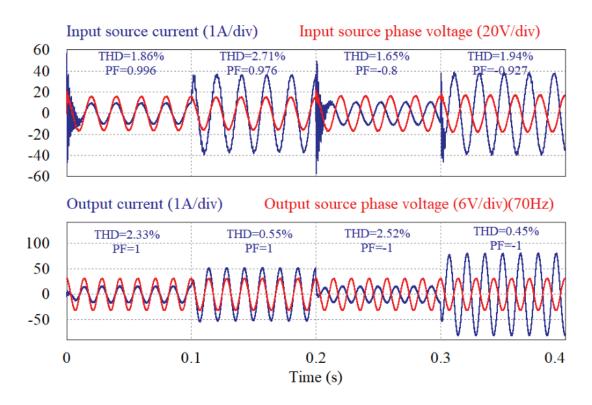

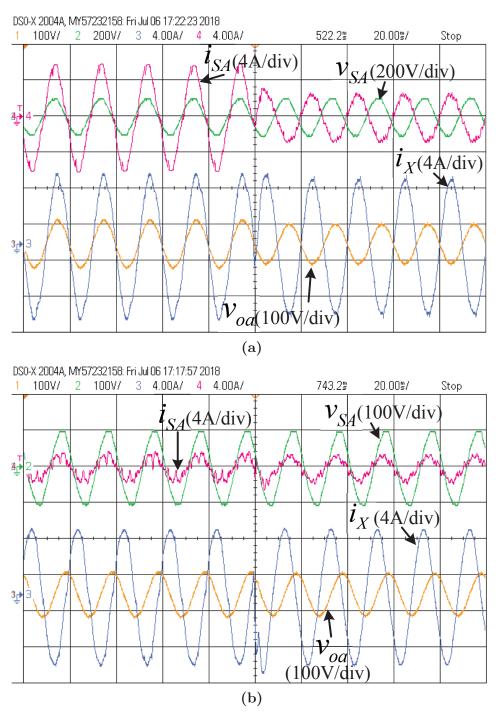

| Figure 6.21 Experimental results for unidirectional active and reactive                                                                                |     |

| power flow, with $R_d = 47\Omega$ and $\tau = 0.5ms$ , where a) $ior(q) = 0$                                                                           |     |

| and $ior(d)$ changes from 4A to 7A, and b) $ior(d) = 0$ and $ior(q)$                                                                                   |     |

| changes from 4A to 7A                                                                                                                                  | 193 |

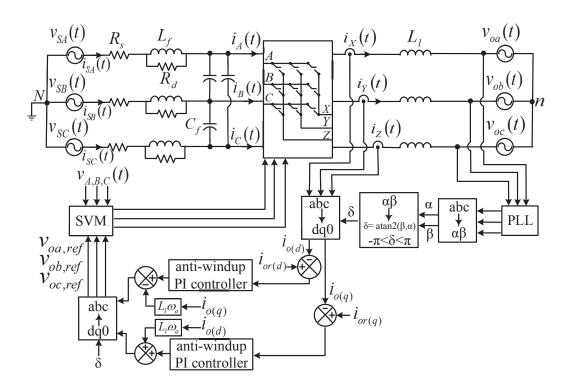

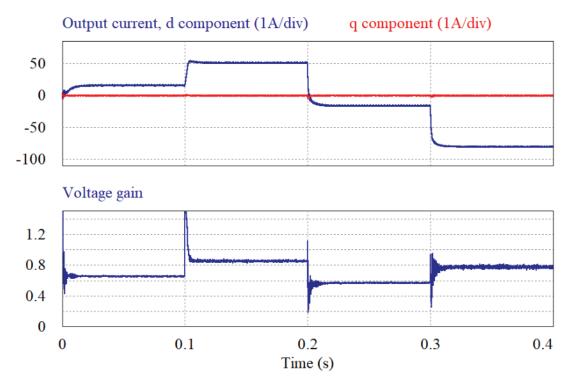

| Figure 6.22 Bidirectional active and reactive output power flow control                                                                                |     |

| using the VOC method                                                                                                                                   | 194 |

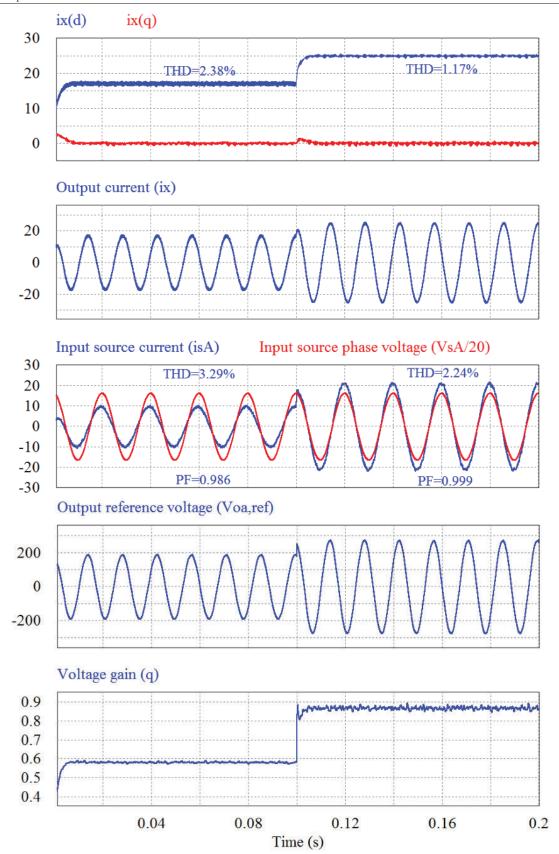

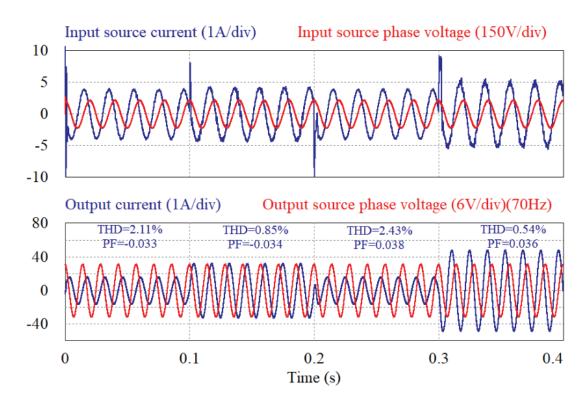

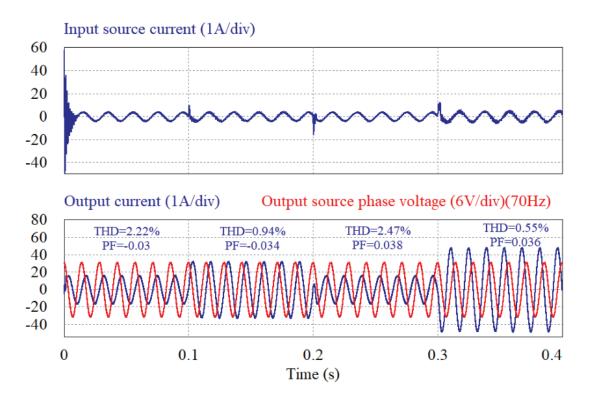

| Figure 6.23 Waveforms of the input source current and output current for                                                                               |     |

| bidirectional active power-flow with $R_d = 3\Omega$                                                                                                   | 195 |

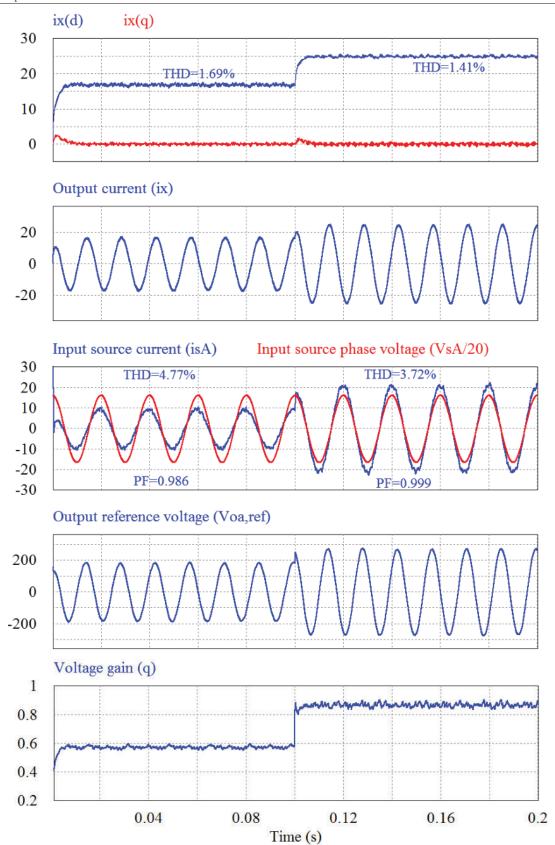

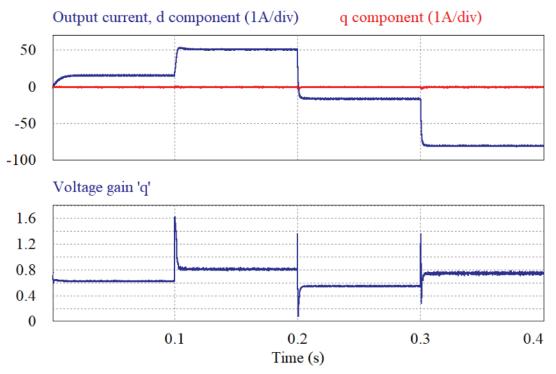

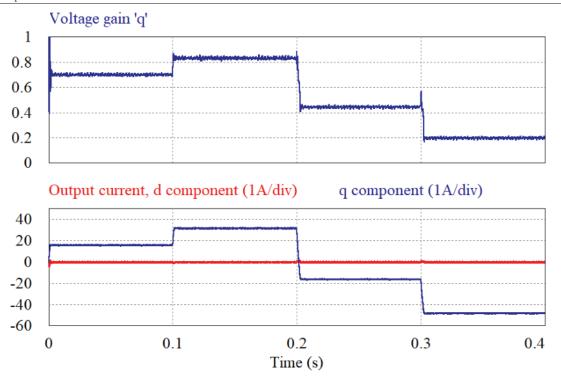

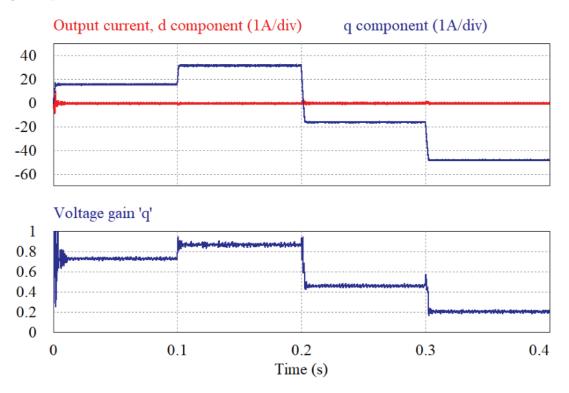

| Figure 6.24 d-q components of the output current and voltage gain for                                                                                  |     |

| bidirectional active power-flow, with $R_d = 3\Omega$                                                                                                  | 195 |

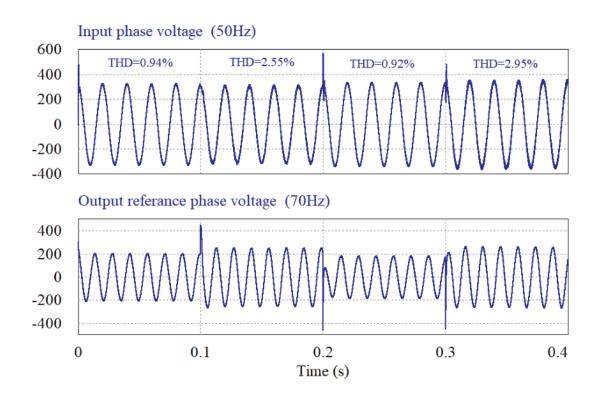

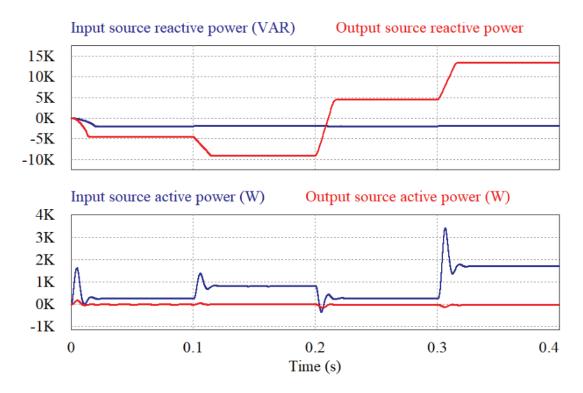

| Figure 6.25 Waveforms of the input voltage and output reference voltage                                                                                |     |

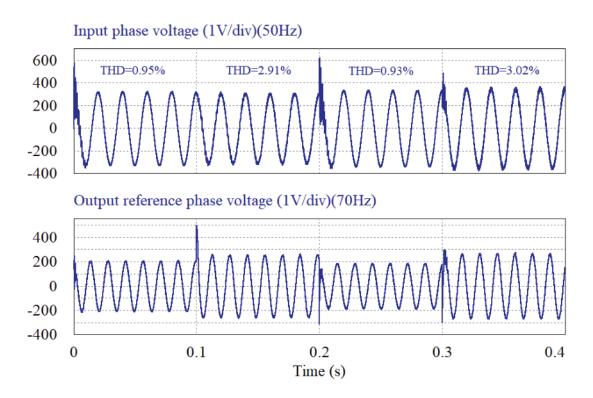

| for bidirectional active power-flow, with $R_d = 3\Omega$                                                                                              | 197 |

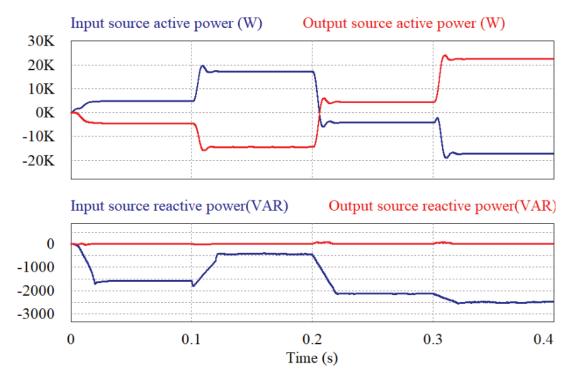

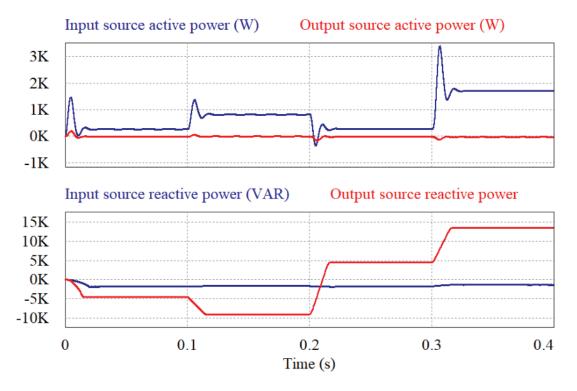

| Figure 6.26 The input and output sources active and reactive powers for                                                                                |     |

| bidirectional active power-flow control, with $R_d = 3\Omega$                                                                                          | 197 |

| Figure 6.27 Waveform of the current and instantaneous power loss in a                                                                                  |     |

| damping resistor $(R_d = 3\Omega)$ for the bidirectional active power-flow                                                                             |     |

| control                                                                                                                                                | 198 |

| Figure 6.28 The voltage gain and d-q components of the output current                                                                                  |     |

| for bidirectional reactive power-flow, with $R_d = 3\Omega$                                                                                            | 199 |

| Figure 6.29 The input source current and output current for bidirectional                                                                              |     |

| reactive power-flow, with $R_d = 3\Omega \dots $ | 200 |

| Figure 6.30 The input and output sources reactive and active powers for                                                                                |     |

| bidirectional reactive power-flow, with $R_d = 3\Omega$                                                                                                | 200 |

| Figure 6.31 The input voltage of the MC and output reference phase volt-                                                                               |     |

| age for hidirectional reactive power-flow with $R_{\rm d}=3\Omega$                                                                                     | 201 |

| Figure 6.32 The input source current and output current for bidirectional                                                    |     |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| active power-flow, with $R_d=3\Omega$ and simulation time-step $4\mu s$                                                      | 201 |

| Figure 6.33 Input source current and output current for bidirectional ac-                                                    |     |

| tive power-flow, with digital input filter $\tau = 0.8ms$                                                                    | 203 |

| Figure 6.34 d-q components of the output current and voltage gain 'q' for                                                    |     |

| bidirectional active power-flow, with digital input filter $\tau=0.8ms$                                                      | 203 |

| Figure 6.35 Input voltage and output reference voltage for bidirectional                                                     |     |

| active power-flow, with digital input filter $\tau = 0.8ms$                                                                  | 204 |

| Figure 6.36 d-q components of the output current and voltage gain 'q' for                                                    |     |

| bidirectional reactive power-flow, with digital input filter $\tau=0.8ms$ .                                                  | 204 |

| Figure 6.37 The input source current and output current for bidirectional                                                    |     |

| reactive power-flow, with digital input filter $\tau = 0.8ms$                                                                | 205 |

| Figure 6.38 The input and output sources active and reactive powers for                                                      |     |

| bidirectional reactive power-flow, with digital input filter $\tau=0.8ms$ .                                                  | 205 |

| Figure 6.39 The input source current and output current for bidirectional                                                    |     |

| active power-flow, with digital input filter $\tau = 0.8ms$ and time-step                                                    | 200 |

| $4\mu s$                                                                                                                     | 206 |

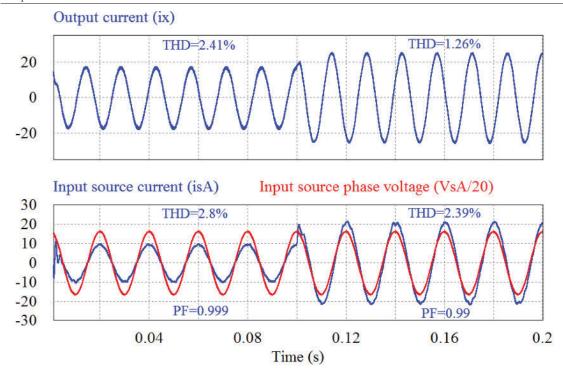

| Figure 6.40 The input source current and output current for bidirectional                                                    |     |

| active power-flow, with the combination of the damping resistor $R_d = 10\Omega$ and the digital input filter $\tau = 0.2ms$ | 207 |

| Figure 6.41 The input source current and output current for bidirectional                                                    | 201 |

| active power-flow, with the combination of the damping resistor $R_d =$                                                      |     |

| $10\Omega$ and the digital input filter $\tau = 0.2ms$ when time-step is $4\mu s$                                            | 207 |

| Figure 6.42 Waveform of the current and instantaneous power loss in a                                                        |     |

| damping resistor for the bidirectional active power-flow control. Sta-                                                       |     |

| bilisation method is a combination of the damping resistor $R_d = 10\Omega$                                                  |     |

| and the digital input filter $\tau=0.2ms$ , when time-step is $4\mu s$                                                       | 208 |

| Figure 6.43 Schematic of the designed system for the experimental test of                                                    |     |

| the MC bidirectional power flow using utility grid                                                                           | 208 |

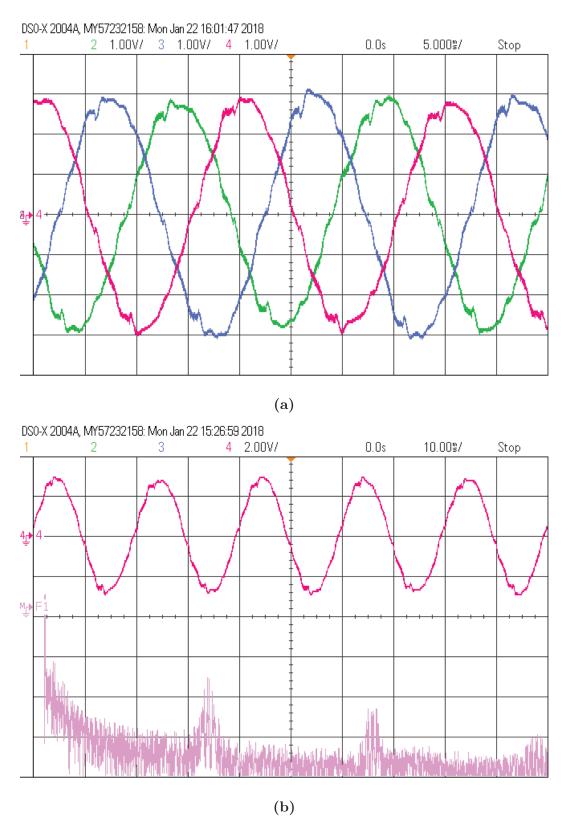

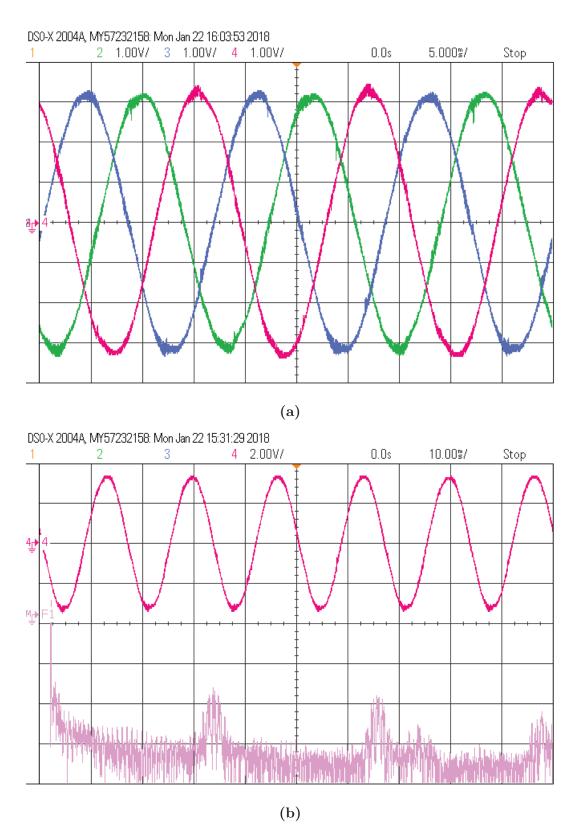

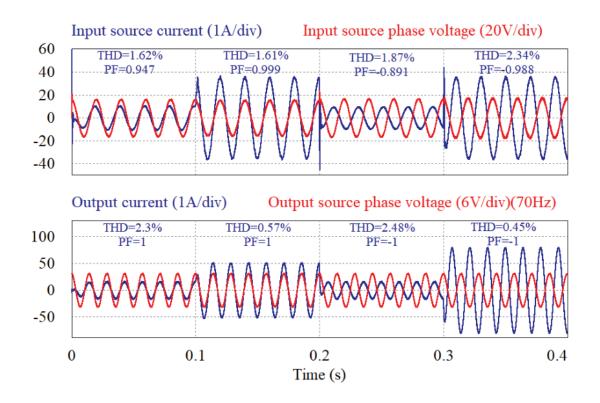

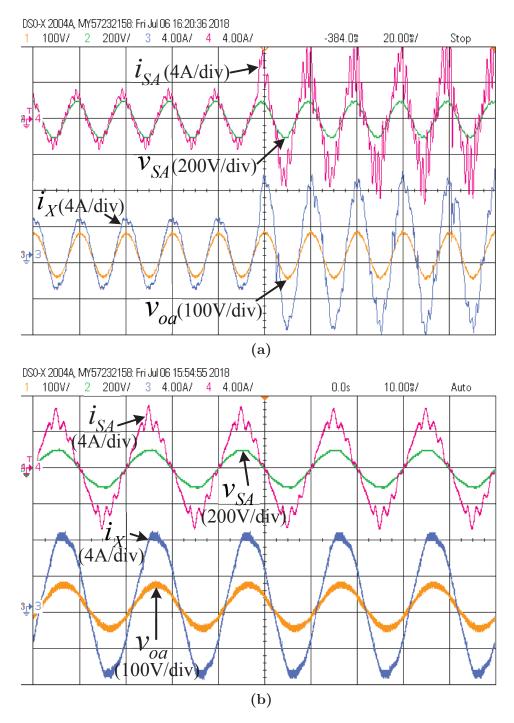

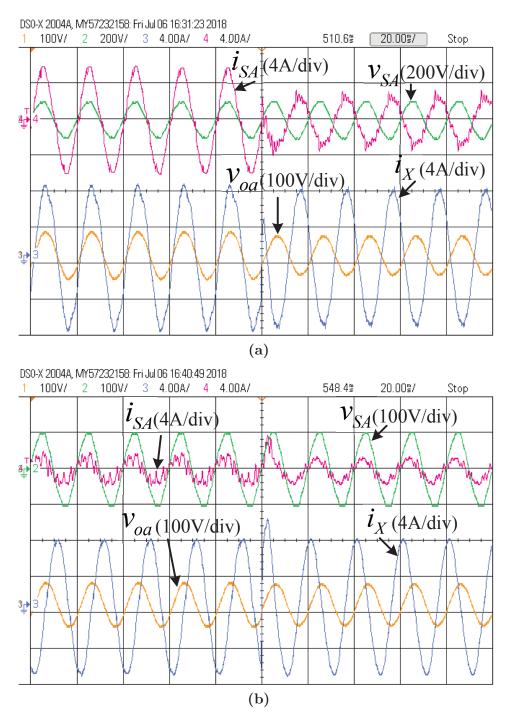

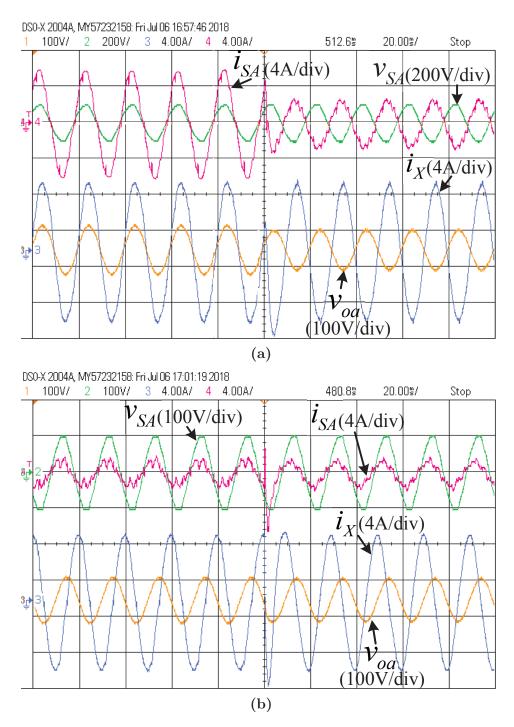

| Figure 6.44 Experimental results for bidirectional active power control,                                                     |     |

| input and output currents and voltages a) Without applying any                                                               |     |

| stabilization method b) By adding only the large damping resistor                                                            |     |

| $R_A = 47\Omega$                                                                                                             | 210 |

# List of Tables

| Table 2.1  | Matrix converter simulation parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1  | Safe switching configurations of DMC and the output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

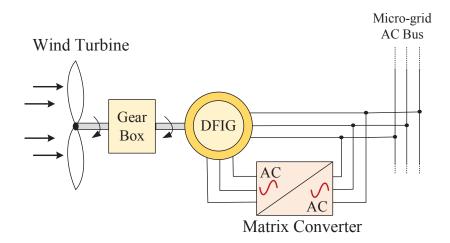

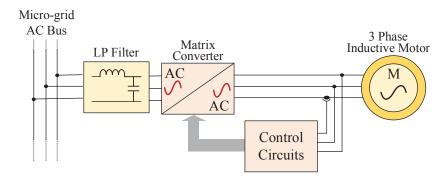

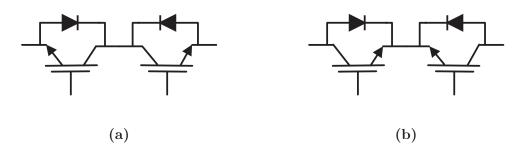

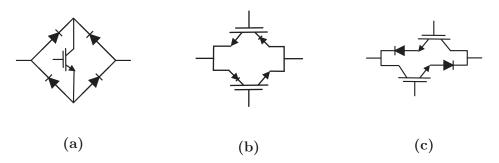

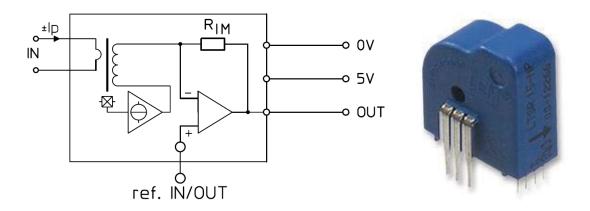

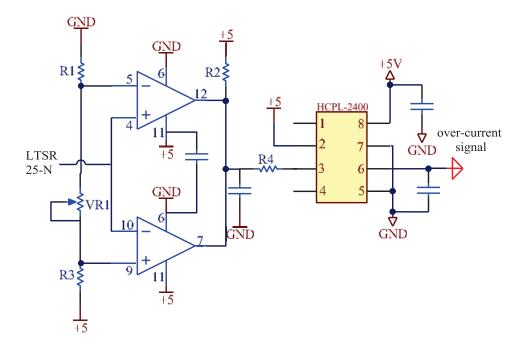

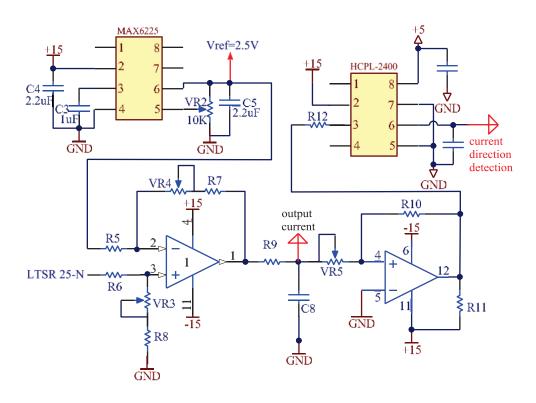

| and the    | he input current vectors associated with them 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |