© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# Power Factor Operation of a Boost Integrated Three-Phase Solar Inverter using Current Unfolding and Active Damping Methods

1<sup>st</sup> Ha Pham N. School of Electrical and Data Eng. University of Technology, Sydney Sydney, Australia phamngocha@ieee.org 2<sup>nd</sup> Tomoyuki Mannen Dept. of Electrical Eng. Tokyo University of Science Tokyo, Japan mannen@rs.tus.ac.jp 3<sup>rd</sup> Keiji Wada Dept. of Electrical and Electronic Eng. Tokyo Metropolitan University Tokyo, Japan kj-wada@tmu.ac.jp

Abstract—This paper proposes a three-phase solar inverter with integrated boost function. The circuit operating principle is based on current unfolding and injection method. This approach requires only two high frequency switches for the boost function as well as shaping its output currents, thus leading to a significant + reduction in switching losses. Other switches only operate at line frequency to unfold the output currents to sinusoidal three-phase currents, and thus can be optimized to reduce conduction losses. The proposed inverter therefore could deliver high efficiency. This paper discusses the basic operating principle and control method for the inverter. The paper proposes an active damping method to overcome intrinsic oscillation due to overlapping time in switching operation. It also shows that the inverter is capable of supplying reactive power up to a limit of 0.866 power factor. Stable operation of the proposed inverter is confirmed by both simulation and experiment.

Index Terms—three-phase inverter, current unfolding, oscillation, active damping

#### I. INTRODUCTION

Solar or Photovoltaic (PV) energy is becoming more competitive due to continuous drop in PV panel production cost. To reduce loss on transmission lines, PV generation can take advantages of three-phase grid connection. Thus, research related to three-phase PV inverters is a focus. For examples, additional boost stage is needed to increase effectiveness of a conventional three-phase PV inverter [1]– [3]. Advanced modulation methods were introduced in [4], [5] to reduce switching loss in three-phase inverters. References [5]– [7] discussed current unfolding and harmonic injection methods to improve the performance of grid-connected three-phase inverters. Other researches applied multilevel approach to reduce voltage stress on high frequency switching devices [8]– [11].

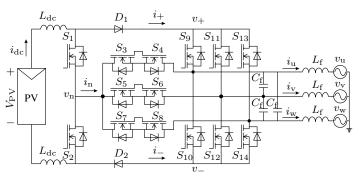

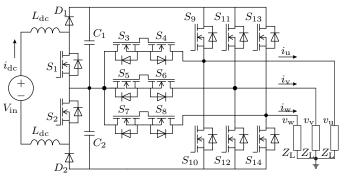

This paper proposes a three-phase inverter with integrated boost function as shown in Fig. 1. The proposed inverter employs 14 switches in total, however, only two of them are operated at high frequency. The remaining 12 switches operate at low frequency and thus have negligible switching losses. These low-frequency switches can be selected to optimise their conduction losses. As a result, the proposed inverter

Fig. 1. Circuit configuration of the proposed three-phase solar inverter.

can reduce both switching and conduction losses. Considering its integrated boost function, the inverter can achieve high efficiency.

The proposed inverter consists of two parts: a boosting stage which controls two output dc currents and a current unfolding stage which acts like a current-source inverter. This configuration has a similar operating principle compared to a SWISS rectifier [7], but it converts electrical power from dc to three-phase ac.

Similar to other current-source inverters, the switching patterns for the proposed inverter must incorporate overlapping time to avoid open circuit conditions. This paper demonstrates that the overlapping causes unwanted fluctuation at the output. Therefore, this type of inverter has to deal with oscillation problem unlike the SWISS rectifier where this effect is not as severe thanks to uncontrolled rectifier bridge. In order to suppress oscillation, active damping method using current feedback control was proposed for dc to dc converter [12]. This paper proposes that existing voltage sensors at the output can be used to suppress the oscillation via voltage feedback and changing the duty cycle at the boosting stage.

Due to new regulation in grid-connected inverters which requires the inverters to be capable of providing reactive power to the grid. This paper proves that the proposed three-phase inverter can deliver that requirement and provide power factor within a reasonable range between 0.866 to 1.

The operation of the proposed method is studied via a scaled down 20-kVA model, connecting a PV to a 400-V threephase transformer before joining a 6.6-kV grid. Simulation results verify stable operation of the inverter as well as the capability of non-unitary power factor operation. In addition, a mini laboratory prototype operating in off-grid mode is built to confirm the feasibility of the inverter in both unitary and non-unitary power factor operations.

## II. CIRCUIT CONFIGURATION

Fig. 1 shows a circuit diagram of the proposed three-phase solar inverter. A PV panel is connected to the positive and negative terminals of the inverter via two dc inductors  $L_{dc}$ to reduce common mode noise. The two dc inductors are then connected to two boost converters which control the input current  $i_{dc}$  and achieve maximum power point tracking (MPPT) for the PV operation at  $V_{\rm PV}$ . The inverter requires only two high frequency switches  $S_1$ ,  $S_2$  and two diodes  $D_1$ ,  $D_2$  to control three currents:  $i_+$  at the positive terminal,  $i_{\rm n}$ at the neutral point, and  $i_{-}$  at the negative terminal. Then, it employs 12 switches  $S_3 \sim S_{14}$  to unfold those currents to form three-phase currents  $i_{\rm u}$ ,  $i_{\rm v}$ ,  $i_{\rm w}$ . Those switches only operate at low frequency and thus have negligible switching loss. Since the circuit operates as a current-source inverter with pulsating output currents, a three-phase filter capacitor  $C_{\rm f}$  is needed at the output terminals. Due to the pulsating output currents, there will be small switching ripples remaining at the filter capacitors. Therefore, before connecting to a three-phase grid, a small three-phase filter inductor  $L_{\rm f}$  can be applied to minimize ripple effect on sinusoidal grid.

# **III. OPERATING PRINCIPLES**

# A. Low-frequency switches

Assume that the output three-phase voltages are balanced as:

$$v_{\rm u} = \sqrt{2V_{\rm o}\cos(\omega t)},\tag{1}$$

$$v_{\rm v} = \sqrt{2V_{\rm o}}\cos(\omega t - 120^\circ), \qquad (2)$$

$$v_{\rm w} = \sqrt{2V_{\rm o}\cos(\omega t + 120^\circ)},\tag{3}$$

where  $V_{\rm o}$  is the rms phase voltage and  $\omega$  is the angular frequency.

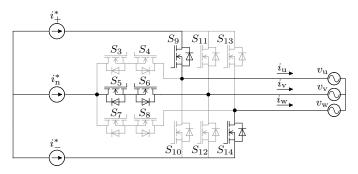

The first principle of the proposed three-phase inverter is to fold the three-phase voltages  $v_{\rm u}$ ,  $v_{\rm v}$  and  $v_{\rm w}$  at the output to match the terminal voltages  $v_+$ ,  $v_{\rm n}$ , and  $v_-$  from the positive, neutral, and negative terminals respectively. Thus, the switching patterns of  $S_3 \sim S_{14}$  are determined by the varying comparative relations of the instantaneous values of the phase voltages  $v_{\rm u}$ ,  $v_{\rm v}$ ,  $v_{\rm w}$ . First, the switches  $S_9 \sim S_{14}$ are operated as a synchronous rectifier to enable reversed current flow from the positive and negative terminals to any two phases which have the highest and lowest voltages. On the other hand, the switches  $S_3 \sim S_8$  connect the neutral terminal to the remaining phase. For this reason, the proposed inverter requires six operating sectors with an equal interval

Fig. 2. Voltage folding principle of the proposed three-phase inverter. Voltages are displayed as per unit compared to base value  $V_{\rm o}$ .

TABLE I

THEORETICAL MODULATION OF THE LOW-FREQUENCY SWITCHES.

| Switches        | Ι | II | ш | IV | V | VI |

|-----------------|---|----|---|----|---|----|

| $S_3, S_4$      | 0 | 1  | 0 | 0  | 1 | 0  |

| $S_5, S_6$      | 1 | 0  | 0 | 1  | 0 | 0  |

| $S_7, S_8$      | 0 | 0  | 1 | 0  | 0 | 1  |

| $S_9$           | 1 | 0  | 0 | 0  | 0 | 1  |

| S <sub>10</sub> | 0 | 0  | 1 | 1  | 0 | 0  |

| S <sub>11</sub> | 0 | 1  | 1 | 0  | 0 | 0  |

| S <sub>12</sub> | 0 | 0  | 0 | 0  | 1 | 1  |

| S <sub>13</sub> | 0 | 0  | 0 | 1  | 1 | 0  |

| $S_{14}$        | 1 | 1  | 0 | 0  | 0 | 0  |

of 60° according to its rotating phase angle  $\omega t$ . These sectors determine the switching sequences for  $S_3 \sim S_{14}$  as shown in Table I, where '1' and '0' indicate 'ON' and 'OFF' conditions of the switching devices respectively. It should be noted that the bidirectional switches  $S_3 \sim S_8$  are operated at double the line frequency, e.g. 100 Hz, because they turn on twice during a cycle, while  $S_9 \sim S_{14}$  only switch at line frequency, e.g. 50 Hz, as they only turn on once.

For examples, sector I is defined for the case when  $v_u > v_v > v_w$ . Here, phase u is always positive and thus, is connected to the positive terminal  $v_+$  via switch  $S_9$ , making  $v_+ = v_u$ . On the other hand, phase w is always negative and is connected to the negative terminal  $v_-$  via switch  $S_{14}$ , and thus  $v_- = v_w$ . The remaining phase v can have either positive or

negative voltage, so it is connected to the neutral terminal  $v_n$  via switches  $S_5$  and  $S_6$  which can enable bidirectional current flow. As a result,  $v_n = v_v$ .

Fig. 2 illustrates how the sectors are allocated as well as how the terminal voltages look like. Notice that all voltages are normalized to a common base of  $V_{\rm o}$ . It is also noted that  $v_+$  at the positive terminal always takes positive value while  $v_-$  at the negative terminal remains negative all the time

$$v_+ > 0, \tag{4}$$

$$v_{-} < 0.$$

(5)

The neutral terminal can take either positive or negative values but it should meet the following condition

$$v_{+} + v_{-} + v_{n} = v_{u} + v_{v} + v_{w} = 0$$

(6)

in a balanced three-phase system. It is also noticed that

$$v_{+} > v_{\rm n} > v_{-}.$$

(7)

which is an important condition to implement the two boost converters because the output voltages of those must be positive.

The differences in terminal voltages

$$v_{+-} = v_{+} - v_{-} \tag{8}$$

$$v_{+n} = v_{+} - v_{n}$$

(9)

$$v_{n-} = v_n - v_-$$

(10)

determine the stress level on switching devices and indicate a selection guide for the switches. For examples, the maximum value of  $v_{+-}$  applies on  $S_9 \sim S_{14}$ , while the maximum value of  $v_{+n}$  and  $v_{n-}$  apply on  $S_1$ ,  $D_1$  and  $S_2$ ,  $D_2$  as well as  $S_3 \sim S_8$  accordingly. Also, the output of the boosting stages  $v_{+-}$  must always be higher than the input voltage from the PV panel, i.e.  $\min(v_{+-}) > V_{\rm PV}$ . Therefore, the operating condition of input voltage is given by

$$V_{\rm PV} < \frac{3\sqrt{2}}{2} V_{\rm o} \approx 2.12 V_{\rm o}.$$

(11)

# B. High-frequency switches

The proposed three-phase inverter operates as a current source inverter with an unfolding operation determined by the aforementioned six operating sectors in Table I. Fig. 3 further explains how the current unfolding operation is realized with the low frequency switches in section I. Considering the dc side as current sources which actually generate pulsating currents. Their average values are determined by the references  $i_{+}^{*}$ ,  $i_{n}^{*}$ ,  $i_{-}^{*}$ . It can be seen that the phase currents in sector I is connected to the corresponding current sources so that

$$i_{\rm u} = i_+^*$$

(12)

$$i_{\rm v} = i_{\rm p}^* \tag{13}$$

$$i_{\rm w} = i^*$$

. (14)

The relationship from  $(12) \sim (14)$  mean that the desired output currents can be used to extract the reference values for the current sources at the input. Similarly, applying the

Fig. 3. Equivalent circuit of the proposed three-phase solar inverter for operation in sector I.

Fig. 4. Creating sinusoidal three-phase currents  $i_u$ ,  $i_v$ ,  $i_w$  by unfolding  $i_+$ ,  $i_-$ ,  $i_n$  via low-frequency switching sequences.

unfolding scheme for the remaining sectors, the full references for terminal currents at the dc side can be achieved.

Fig. 4 illustrates how a balanced three-phase currents determines the corresponding references for the current sources. Notice that  $i^*_+$  is always positive and  $i^*_-$  always takes negative value. The remaining neutral current  $i_n$  can take either positive or negative value depending on the phase condition and the operating power factor. Its value is automatically determined by Kirchhoff's current law

$$i_{\rm n} = -i_+ - i_-$$

(15)

and thus, it is only needed to control  $i_+$  and  $i_-$  by adjusting the duty cycles  $D_+$  and  $D_-$  in the two boost converters to

Fig. 5. Commutation transition in switching operation from sector I to sector II.

achieve three sinusoidal outputs. However, the condition to keep  $i_+$  positive and  $i_-$  negative all the time is that the power angle must stay between  $-30^{\circ}$  and  $+30^{\circ}$  as seen in Fig. 4, thus the adjustable power factor of the inverter must be higher than  $\cos 30^{\circ} = 0.866$ . Nevertheless, this limit is more than adequate to future operation of grid-connected PV inverters according to the Medium-Voltage Guidelines of the German Federal Association of the Energy and Water Industry.

# C. Commutation transition in low-frequency switching operation

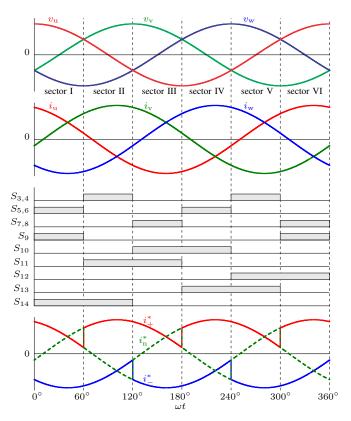

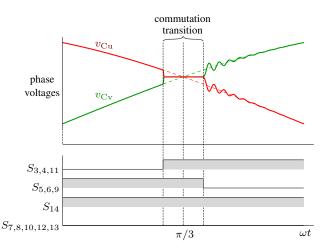

Since the low-frequency part of the proposed topology operates as a current source inverter, it requires filter capacitors and the modulation needs overlap transition instead of blanking time. Fig. 5 shows the transition when changing from sector I to sector II. It can be seen that the positive and neutral terminals are shorted during the transition because of two temporary paths created by switches  $S_3$ ,  $S_4$ ,  $S_9$  and  $S_5$ ,  $S_6$ ,  $S_{11}$ .

Ideally, this occurs exactly at  $\omega t = \pi/3$  when  $v_u = v_w$ , thus  $v_{+n} = 0$ , i.e. there should not be any short-circuit problem. However, the overlap time is not zero in practice due to limitation in switching speed as well as difficulty in synchronization of the ON/OFF timing. Therefore, the transition starts before and ends after  $\omega t = \pi/3$  as shown in Fig. 6. When the short circuit occurs, the voltage difference at the output is quickly reduced to zero. As a result, the current at the positive terminal  $i_+$  experiences a temporary glitch due to the short circuit. After the transition, the difference will appear again and thus cause oscillation in both output voltage and current waveforms because of resonance between output filter capacitors and equivalent circuit inductors.

## D. Active damping

The aforementioned oscillation at the output due to current unfolding transition will cause distortion as well as increased THD. This paper proposes an active damping method to reduce the unwanted effect.

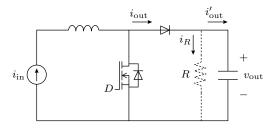

Considering the boost converter at the input, a normal switching operation yields

$$\overline{i_{\text{out}}} = Di_{\text{in}}, \qquad (16)$$

Fig. 6. Voltage waveforms during the commutation transition from sector I to sector II.

Fig. 7. Boost converter equipped with active damping resistor.

where D represents the 'ON' duty cycle of active switch in a boost converter circuit. If the output is connected to a capacitor, resonant oscillation will occur at certain operating conditions.

Fig. 7 illustrates a boost converter equipped with a parallel resistor R at the output. The output current becomes

$$i'_{\rm out} = i_{\rm out} - i_R, \tag{17}$$

and thus,

$$\overline{i'_{\text{out}}} = Di_{\text{in}} - \frac{v_{\text{out}}}{R}.$$

(18)

This resistor R acts as a damping factor to suppress oscillation in the boost converter. However, real resistor will consumes power and thus increases power loss. Therefore, the duty cycle can be redefined as

$$D' = \frac{\overline{i'_{\text{out}}}}{i_{\text{in}}} = D - \frac{v_{\text{out}}}{i_{\text{in}}R},$$

(19)

to provide active damping without implementing real resistor. Unfortunately, this form will cause unwanted output current reduction which leads to distortion from sinusoidal reference. Thus, we only consider deviation from target value to suppress the unwanted oscillation. Equation (19) is therefore adjusted to be

$$D' = D - \frac{v_{\rm out} - v_{\rm out}^*}{i_{\rm in}R}.$$

(20)

This new duty cycle provides active damping at the output voltage without affecting the control for large signal.

Fig. 8. Control block diagram of the three-phase solar inverter for operation in sector I.

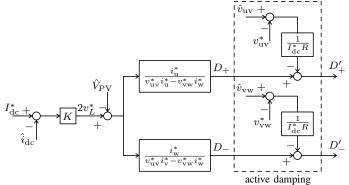

## E. Control method

Applying Kirchoff's voltage law at the dc side yields

$$V_{\rm PV} - 2v_L = v_{L+} - v_{L-},\tag{21}$$

where  $v_{L+}$  and  $v_{L-}$  are the voltages at the output of the upper and lower dc inductors, respectively. At sector I, boosting operation at the positive terminal yields

$$v_{L+} = D_+ v_{\rm uv} \tag{22}$$

$$i_{\rm u} = i_+ = D_+ i_{\rm dc}.$$

(23)

Similarly at the negative terminal, we have

$$v_{L-} = D_{-}v_{\rm vw} \tag{24}$$

$$i_{\rm w} = i_{-} = -D_{-}i_{\rm dc}.$$

(25)

Notice the negative sign in the current equation coming from the fact that  $i_{-}$  always takes negative value while  $i_{dc}$  is defined to be positive. Solving equations (21) ~ (25) yields

$$D_{+} = \frac{i_{\rm u}(V_{\rm PV} - 2v_{L})}{v_{\rm uv}i_{\rm u} - v_{\rm vw}i_{\rm w}}$$

(26)

$$D_{-} = \frac{i_{\rm w}(V_{\rm PV} - 2v_L)}{v_{\rm uv}i_{\rm v} - v_{\rm vw}i_{\rm w}}.$$

(27)

The voltage of the input inductor is determined by

$$v_L = L_{\rm dc} \frac{di_{\rm dc}}{dt}.$$

(28)

Therefore, the inductor voltage can be determined using feedback control of  $i_{\rm dc}$  as follows

$$v_L^* = K(i_{\rm dc}^* - i_{\rm dc}).$$

(29)

The proposed inverter can be operated following the relations expressed by (26), (27), and (29). The control method for sector I is summarized in Fig. 8 where active damping expressed by (20) is also included.

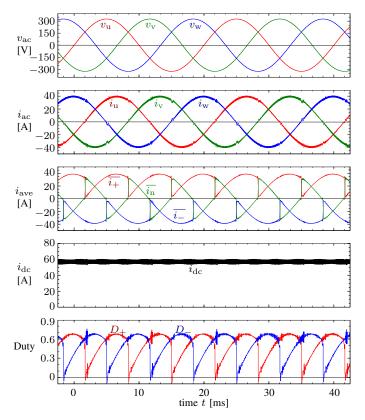

Fig. 9. Simulation waveforms of the proposed three-phase inverter under unitary power factor.

TABLE II CIRCUIT PARAMETERS USED IN SIMULATION

| Symbol           | Meaning                         | Value            |

|------------------|---------------------------------|------------------|

| $V_{\rm o}$      | output phase rms voltage        | 220 V            |

| $I_{\rm o}$      | output rms current              | 28.3 A           |

| $V_{\rm PV}$     | MPPT voltage of PV              | 300 V            |

| f                | line frequency                  | $50~\mathrm{Hz}$ |

| $f_{\rm sw}$     | switching frequency             | 20 kHz           |

| $L_{\rm dc}$     | dc inductor                     | 0.5  mH          |

| $L_{\rm f}$      | ac filter inductor              | 0.2 mH           |

| $C_{\mathrm{f}}$ | ac filter capacitor             | $10 \ \mu F$     |

| $t_{ m c}$       | commutation transition duration | $100 \ \mu s$    |

### **IV. SIMULATION RESULTS**

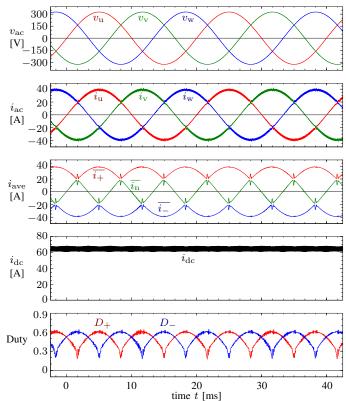

Circuit simulation was carried out to test the performance of the proposed inverter. The simulated circuit parameters are shown in Table II. The system is designed to operate at 20 kVA where the MPPT voltage of PV reaches around 300 V. The line frequency is set at 50 Hz, while the switching frequency of  $S_1$ ,  $S_2$  is set at 20 kHz to avoid acoustic noise. The dc inductors are chosen as 0.5 mH to limit the ripple at the PV input to less than 10% at rated power. The output filters suppress the output current THD to less than 5% at rated condition. The overlap time for commutation in low-frequency switching operation is set to be 100  $\mu$ s in the simulation to demonstrate the effectiveness of the proposed damping method.

Fig. 10. Simulation waveforms of the proposed three-phase inverter under 0.866 power factor lagging.

Fig. 9 show the simulated operation of the inverter under unitary power factor. The dc input current  $I_{dc}$  is controlled to be constant at 66.6 A when the MPPT voltage is  $V_{PV} = 300$  V so that the output power reaches 20 kW. The output voltages and currents have a peak of 310 V and 40 A, respectively. It can be seen that the average currents in  $i_+$ ,  $i_n$ , and  $i_-$  are not ideal due to overlapping time implementation in switches  $S_3 \sim S_{14}$ . Due to the glitches, the output currents  $i_u$ ,  $i_v$ ,  $i_w$  contains oscillating component that comes from resonance between the output filter capacitors and equivalent circuit inductors. To deal with this oscillation, the duty cycles  $D_+$  and  $D_-$  are adjusted with the proposed active damping method. As a result, the distortion caused by the overlapping time is minimized. This proves the effectiveness of the proposed active damping control.

Fig. 10 show the simulated operation of the inverter under 0.866 power factor lagging, where the phase currents lag the corresponding voltages by 30°. The phase currents are controlled to maintain the 40-A peak and keep the apparent power constant at 20-kVA. Consequently, the dc input current  $I_{dc}$  is adjusted lower to 57.7 A because the active power is reduced. The limit of controllable power factor can be seen in the average currents of  $i_+$  and  $i_-$  where their minimal values reach 0 at times. Consequently, the duty cycles  $D_+$  and  $D_-$  are adjusted to be around 0 to output zero currents. Since duty cycles cannot be negative, the power factor reaches its limitation here at 0.866.

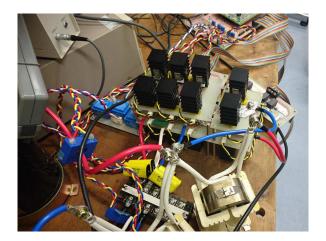

Fig. 11. Experiment set up of the proposed inverter.

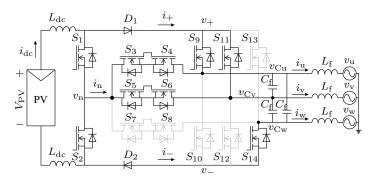

Fig. 12. Circuit diagram used in the experiment for feasibility testing of the proposed three-phase inverter.

#### V. EXPERIMENTAL RESULTS

A mini laboratory prototype was set up to demonstrate the proposed inverter. Fig. 11 shows a picture of the experiment set up. The PV panel was replaced with a voltage source. Its input voltage was set to 140V dc and the output currents were controlled to have 1.77 A rms. For the sake of simplicity in the feasibility test, the grid was replaced by a balanced star-connected load  $Z_{\rm L}$ . The off-grid circuit diagram is shown in Fig. 12. The load  $Z_{\rm L}$  can be chosen as resistive load  $R_{\rm L}$  or inductive load which consists of a resistor  $R_{\rm L}$  and an inductor  $L_{\rm L}$  in series. Because the circuit is now operating in off-grid mode, the output filters  $C_{\rm f}$  and  $L_{\rm f}$  are removed. The pulsating output currents are filtered by dc decoupling capacitors  $C_1$  and  $C_2$  instead. The circuit parameters used in the experiment is shown in Table III.

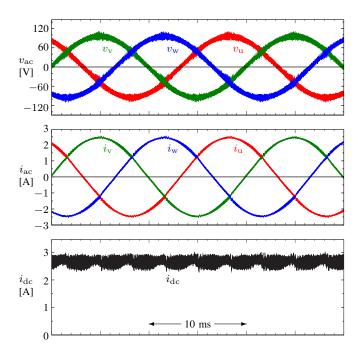

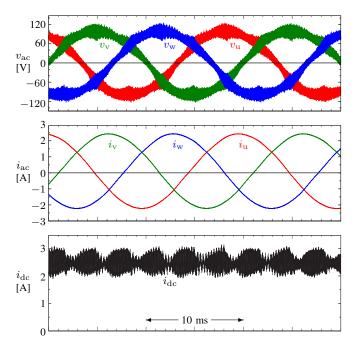

Fig. 13 shows the measured steady-state waveforms when providing power to a balanced star-connected resistive load  $Z_{\rm L} = R_{\rm L}$ . The output voltages contains switching ripples due to operation of the boost converters. The dc decoupling capacitors filtered most of the ripples and thus the output currents became sinusoidal. It is noticed that the ripple in the currents were much smaller than those in the voltages despite the fact that the loads were only resistors. This was due to

TABLE III Circuit Parameters used in Experiment

| Symbol       | Meaning                         | Value         |

|--------------|---------------------------------|---------------|

| Vo           | phase rms voltage               | 70.7 V        |

| Io           | phase rms current               | 1.77 A        |

| $V_{\rm in}$ | input voltage                   | 140 V         |

| f            | line frequency                  | 50 Hz         |

| $f_{\rm sw}$ | switching frequency             | 20 kHz        |

| $L_{\rm dc}$ | dc inductors                    | 0.5  mH       |

| $C_1, C_2$   | dc decoupling capacitors        | $1 \ \mu F$   |

| $R_{\rm L}$  | load resistors                  | $40 \ \Omega$ |

| $L_{\rm L}$  | load inductors                  | 50  mH        |

| $t_{\rm c}$  | commutation transition duration | 2 µs          |

| Symbols           | Device        |

|-------------------|---------------|

| $S_1, S_2$        | STW58N60DM2AG |

| $D_1, D_2$        | RFN30TS6N     |

| $S_3 \sim S_{14}$ | SCT3040KL     |

the parasitic inductance in the loads. It can be seen that the output voltages are in phase with the currents, and thus the power factor is unity in this case. The input dc current was constant but contained switching ripples. Its average value was controlled to be 2.7 A, which was a little above the peak output current of 2.5 A. It was the requirement for operating the boost converters.

Fig. 14 shows the measured steady-state waveforms when providing power to a balanced star-connected inductive load  $Z_{\rm L} = R_{\rm L} + j\omega L_{\rm L}$ . The output currents lagged the voltages by 21°, and the power factor was 0.93. It can be seen that the output voltages in case of non-unitary power factor operation contains higher switching ripples compared to that in unitary power factor operation. On the other hand, the output currents contained almost no ripple due to the nature filtering capability of the series inductor in the load. The input dc current and the output currents were controlled to remain constant at 2.7 A and 2.5 A peak, respectively. It can be seen that ripple in the input dc current in this case was also higher compared to that case of unitary power factor.

### VI. CONCLUSION

This paper discussed a boost integrated three-phase solar inverter using current unfolding method. The proposed circuit acts as a current-source inverter and can provide non-unity power factor with a lower limit of 0.866. The proposed topology needs only two high-frequency switches while it does not require large output ac inductors. It employs another 12 low-frequency switches for unfolding operation, but the conduction loss can be optimized thanks to their negligible switching losses. As a result, high efficiency and/or size reduction in passive components could be achieved.

This paper also revealed that the commutation time in switching transition of the unfolding operation can cause unwanted oscillation at the output. The authors proposed

Fig. 13. Experimental waveforms of the proposed three-phase inverter under unity power factor, supplying a balanced star-connected resistive load of 40  $\Omega$ .

Fig. 14. Experimental waveforms of the proposed three-phase inverter under 0.93 power factor, supplying a balanced star-connected inductive load which consists of  $40-\Omega$  resistor and 50-mH inductor in series.

an active damping method to suppress the oscillation and overcome the difficulty. Simulation study presented stable operation of the proposed inverter and proved the effectiveness of the proposed active damping method in grid-connected mode. Finally, an experimental verification in off-grid mode was successfully carried out to confirm the feasibility of the proposed inverter.

### REFERENCES

- M. de Brito, L. Sampaio, G. Melo and C. A. Canesin, "Three-phase tristate buck-boost integrated inverter for solar applications," *IET Renewable Power Generation*, vol. 9, no. 6, pp. 557–565, Aug. 2015.

- [2] C. Jain and B. Singh, "A Three-Phase Grid Tied SPV System With Adaptive DC Link Voltage for CPI Voltage Variations," *in IEEE Transactions* on Sustainable Energy, vol. 7, no. 1, pp. 337–344, Jan. 2016.

- [3] E. Serban, F. Paz and M. Ordonez, "Improved PV Inverter Operating Range Using a Miniboost," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8470–8485, Nov. 2017.

- [4] D. Yamaguchi and H. Fujita, "A new PV converter for grid connection through a high-leg delta transformer using cooperative control of boost converters and inverters," 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017 - ECCE Asia), pp. 911–916, 2017.

- [5] U. R. Prasanna and A. K. Rathore, "Dual Three-Pulse Modulation-Based High-Frequency Pulsating DC Link Two-Stage Three-Phase Inverter for Electric/Hybrid/Fuel Cell Vehicles Applications," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 477–486, Sept. 2014.

- [6] H. Yoo and S. K. Sul, "A new circuit design and control to reduce input harmonic current for a three-phase ac machine drive system having a very small dc-link capacitor," 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 611–618, 2010.

- [7] T. B. Soeiro, T. Friedli and J. W. Kolar, "Swiss rectifier A novel threephase buck-type PFC topology for Electric Vehicle battery charging," 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 2617–2624, 2012.

- [8] M. R. Islam, A. M. Mahfuz-Ur-Rahman, M. M. Islam, Y. G. Guo and J. G. Zhu, "Modular Medium-Voltage Grid-Connected Converter With Improved Switching Techniques for Solar Photovoltaic Systems," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 11, pp. 8887–8896, Nov. 2017.

- [9] Y. Wang, F. Wang, "Novel Three-Phase Three-Level-Stacked Neutral Point Clamped Grid-Tied Solar Inverter With a Split Phase Controller," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2856–2866, Jun. 2013.

- [10] L. B. G. Campanhol, S. A. O. da Silva, A. A. de Oliveira and V. D. Bacon, "Dynamic Performance Improvement of a Grid-Tied PV System Using a Feed-Forward Control Loop Acting on the NPC Inverter Currents," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 3, pp. 2092–2101, Mar. 2017.

- [11] S. K. Chattopadhyay and C. Chakraborty, "A New Asymmetric Multilevel Inverter Topology Suitable for Solar PV Applications With Varying Irradiance," *IEEE Transactions on Sustainable Energy*, vol. 8, no. 4, pp. 1496–1506, Oct. 2017.

- [12] A. M. Rahimi and A. Emadi, "Active Damping in DC/DC Power Electronic Converters: A Novel Method to Overcome the Problems of Constant Power Loads," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 5, pp. 1428–1439, May 2009.