# Active Gate Drive to Increase the Power Capacity of Hard-Switched IGBTs

Gwilym T. Jones, *Student Member, IEEE*, Yam P. Siwakoti, *Senior Member, IEEE*, and Daniel J. Rogers, *Senior Member, IEEE*,

Abstract—The effect of the gate drive on the power-processing capacity of a hard-switched Insulated Gate Bipolar Transistor (IGBT) in a bridge leg is investigated in this paper. The performance of two Active Gate Drive (AGD) techniques (Variable Ramp (VR) and Push-Pull (PP)) is compared against a conventional two-level (Fast Gate Drive (FGD)) gate drive method. The two proposed techniques reduce the voltage overshoot, which allows the dc-bus voltage to be increased closer to the IGBT voltage rating, improving the utilization of the device's blocking voltage. Consequently, the safe operating area of the IGBT is extended without exceeding the thermal limit of the device (limited by maximum junction temperature). An experimental method, the first of its kind in the literature, is developed to determine whether using these active gate drives can lead to an increase in the power that the IGBT can process. The study reveals that the PP-AGD technique can increase the IGBT power throughput by approximately 5%-8% across a range of switching frequencies. This better IGBT utilization allows a given device to process more power or may allow the designer to choose lowerpower rated devices potentially leading to higher converter power density.

# I. INTRODUCTION

S power electronic converters become pervasive in consumer, industrial, and grid applications, the need for greater efficiency, power density, and reliability drives innovation across all aspects of system design. Power density is determined by several components, including the semicondutor devices, passive components, and heatsinks. [1]. Maximum power density is achieved through operating each component at its full capacity, i.e. under-utilized components should either be resized or the power throughput should be increased [2]. The focus of this paper is on maximising the utilization of the semiconductor switch by using an Active Gate Drive (AGD) technique.

The switching behaviour of power transistors such as Metal-Oxide-Semiconductor Field-Effect Transistors (MOS-FETs) and Insulated Gate Bipolar Transistors (IGBTs) can be controlled, to an extent, by the gate drive circuit. Conventionally, such control has been limited to selection of the resistors in the gate current path, for example in [3] an analytical model is used to evaluate IGBT switching performance for different turn-on and turn-off gate resistances. Such added resistance acts to limit the charge/discharge rate of the capacitive gate of the device and control the switching speed. Since the gate resistance is fixed, at the design or commissioning stage it must be chosen to ensure that criteria relating to the switching

This work was funded by the Engineering and Physical Sciences Research Council under studentship award 1798093 and project EP/L019469/1.

behaviour, such as slew rates and peak voltage limits, are satisfied across the full operating range of the converter. For instance, the highly non-linear Miller capacitance between gate and drain/collector leads to the  $\mathrm{d}v/\mathrm{d}t$  being largest when operating at the maximum dc-bus voltage, and a gate resistor conservatively sized to satisfy a  $\mathrm{d}v/\mathrm{d}t$  limit at this operating point will lead to slower slew rates at lower dc-bus voltages, leading to unnecessary additional switching loss [4].

Over the last twenty years, several AGD concepts have been proposed to improve power transistor switching behaviour. Early research in the 1990s enabled current balancing of paralleled IGBT modules through the use of closed-loop control of gate voltage [5], [6], a concept which was later developed in [7]. Similarly, control of  $\mathrm{d}v/\mathrm{d}t$  using feedback of IGBT collector voltage [8]–[11] has been developed to obtain desired collector-emitter voltage slew-rates, which allows series connection of IGBTs through voltage-balancing without the use of external snubber circuits.

More generally, the AGDs proposed in the literature address the challenging task of controlling the switching trajectory to reduce the switching energy loss, while at the same time managing electromagnetic interference (EMI) issues and reducing the stress applied to the semiconductor devices (such as peak voltage stress induced by  $\mathrm{d}i/\mathrm{d}t$  across parasitic inductance in the commutation current path). Additionally, overcurrent and overvoltage protection can be implemented in the gate drive. The research can be divided into open-loop methods [12]–[20] which operate without feedback of the switching behaviour, and closed-loop methods where measurements are fed back to modify the control signal [21]–[27].

A high-speed open-loop active gate drive in [12] uses a selectable number of drive transistors to shape the switching trajectory of a GaN FET to reduce overshoot and EMI. Another open-loop approach limits the maximum  $\mathrm{d}v/\mathrm{d}t$  of a SiC MOSFET [13], while in [14] a Laplace-domain switching model of a SiC MOSFET is used to derive gate drive parameters (resistance, drive voltage levels, external gate-source capacitance). In several studies the switching transient is divided into four periods, and different gate drive strengths are applied during each period. The duration of each period is either manually set [15] or dynamically updated based on stage-detection circuitry [16]–[19]. Open-loop control is shown to be effective for some changes in operating conditions through the use of a look-up table that contains pre-determined information about the gate control for each operating condition [20].

A closed-loop approach is required to closely track the

desired switching behaviour without using a look-up table as the operating conditions change. Analogue feedback of  $\mathrm{d}v/\mathrm{d}t$  and  $\mathrm{d}i/\mathrm{d}t$  with P or PI control has been used to obtain particular slew rates across a range of load currents for several IGBT modules [21]–[26]. Independent control of  $\mathrm{d}v/\mathrm{d}t$  and  $\mathrm{d}i/\mathrm{d}t$  is demonstrated with optically-triggered MOSFETs in [27]. Gate-assist circuits are connected based on the voltage drop across the Kelvin inductance in [28] to increase the  $\mathrm{d}v/\mathrm{d}t$  and reduce delay time, while the current slew rate is unaffected and is still controlled by the gate resistor.

Closed-loop control in fast switching transients requires high control loop bandwidth. This is a particular challenge for digital implementations where ADC and DAC latency may combine to produce input-to-output delay in the control loop of approximately 30 ns, even with fast  $\sim 1$  GS/s ADC/DACs [29]. In the case of SiC devices, where the switching times are in the order of tens of nanoseconds [15], this latency makes the digital closed-loop control extremely challenging. An alternative is the 'iterative control' or 'sequential optimization' that has been widely investigated [29]–[38]. In this scheme, measurements of the previous switching edge are used to modify the gate control of subsequent switching transitions. In [32]-[35] an IC with multiple drive current strengths is used to improve the trade-off between voltage overshoot and switching energy loss. The gate current profile is iteratively adapted in [37] to constrain the maximum dv/dt and  $d^2v/dt^2$  to reduce EMI, while gate current profile adaptation can also be applied to reduce EMI in low-voltage contexts such as the 1.2 V 1.8 MHz converter in [39].

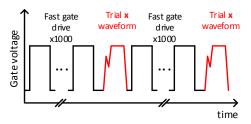

An intriguing possibility raised by these technologies is an increase in the capacity of the semiconductor switch by managing the voltage overshoot, and therefore allowing the dc-bus voltage to be increased closer to the rated maximum voltage of the switch. Due to the inherent trade-off between switching loss and voltage overshoot, it does not automatically follow that a reduction in voltage overshoot will lead to increased switch power capacity. Figure 1 illustrates three gate drive waveforms which are compared in this paper: (a) a conventional two-level (Fast Gate Drive (FGD)) waveform, (b) a Variable Ramp (VR) AGD waveform, and (c) a Push-Pull (PP) AGD waveform. More detail about the design of the gate drive waveforms is given in Section III-B. To compare these gate drive waveforms, it is necessary to develop a framework to evaluate their impact on switch capacity. This paper presents such a framework, and is to the authors' best knowledge the first to develop this method. It is shown by experiment that the PP waveform increases IGBT capacity by 5%-8% compared to the FGD and VR waveforms. It should be emphasized that this paper does not present control of switching behaviour beyond what is already published in the literature cited above. Rather, the contribution is to demonstrate that such control can increase the maximum amount of power that a switch can process.

Section II introduces the analysis which leads to the hypothesis that switch capacity can be increased by using AGDs under certain conditions. Section III presents the experimental methodology, followed by the results in Section IV. The significance of the findings is discussed in Section V.

Fig. 1. Example AGD gate voltage references for turn-on with (a) FGD, (b) VR-AGD, and (c) PP-AGD. Parameter  $\mathbf{x}$  is defined in Section III-B.

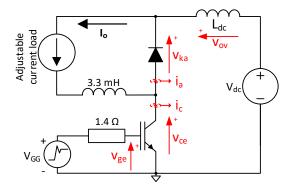

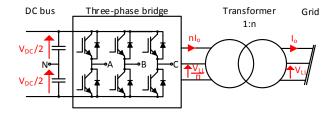

Fig. 2. Converter used in this study, with independent control of load current and dc-bus voltage.

#### II. DEFINITION OF SWITCH CAPACITY

The capacity of a switch is defined here as the maximum apparent power S it can process, i.e. the product of the voltage it can block when turned off and the conducted current when turned on. Considering a bridge-leg consisting of two devices in a totem-pole, for example in the buck converter shown in Fig. 2, the blocked voltage is the dc-bus voltage and the conducted current equals the output current, giving

$$S = V_{dc}I_{o}. (1)$$

Here,  $L_{\rm dc}$  is a lumped representation of parasitic inductances in the power loop which cause the voltage overshoot during switching due to  ${\rm d}i/{\rm d}t$ . The dc-bus voltage plus this transient voltage overshoot must be less than or equal to the rated blocking voltage of the switch:

$$V_{\rm dc} + V_{\rm ov} \le V_{\rm CE(max)}.$$

(2)

where  $V_{\text{ov}}$  is the maximum transient voltage overshoot and  $V_{\text{CE}(\text{max})}$  is the rated voltage of the switch.

The conducted current is limited by the allowable power loss of the switch, which can be expressed as the sum of conduction and switching loss for an IGBT as

$$P_{loss} = P_{c} + P_{sw}$$

$$= DI_{o}V_{CE(on)}(T, I_{o})$$

$$+ f_{sw}F(I_{o}, V_{dc}, T, \text{ gate drive}, ...)$$

(3)

where

$V_{\mathrm{CE(on)}}$  on-state collector-emitter voltage of the IGBT

T junction temperature of the switch

D duty cycle of the switch

$f_{\rm sw}$  switching frequency

F() an unknown function mapping switching energy loss to load current, dc-bus voltage, and other factors such as device physics, circuit layout, gate drive etc.

The form of the function F() is unknown, but the value of F() can be obtained during switching operation as the switching energy loss, calculated from the measured collector current and collector-emitter voltage waveforms as:

$$F() = E_{\text{sw}} = E_{\text{on}} + E_{\text{off}}$$

$$= \int_{t_1}^{t_2} v_{ce} i_c. dt + \int_{t_2}^{t_4} v_{ce} i_c. dt$$

(4)

where  $t_1, t_2$  and  $t_3, t_4$  are respectively the start and end times of the turn-on and turn-off switching event, and  $v_{ce}$  and  $i_c$  are respectively the switch's collector-emitter voltage and collector current [40].

The form of F() in (3) is presented in this section to highlight the dependence of switching energy loss on load current, dc-bus voltage, and gate drive. Later in the work, the form of (4) is used when measurable values of  $E_{\rm sw}$  are being discussed.

The maximum power loss is set by the junction temperature limit of the device

$$P_{\rm loss}^{\rm max} = \frac{T_j^{\rm limit} - T_a}{R_{ja}} \,. \tag{5}$$

where

$T_i^{\text{max}}$  junction temperature limit

$T_a$  ambient temperature

$R_{ja}$  junction-ambient thermal resistance.

Rearranging (1)-(3), the maximum switch apparent power can be expressed as

$$S^{\text{max}} = \frac{(V_{\text{CE(max)}} - V_{\text{ov}})(P_{\text{loss}}^{\text{max}} - f_{\text{sw}}F(I_o, V_{\text{dc}}, \text{gate drive}, \dots))}{DV_{(\text{CE,on})}(T, I_o)}$$

(6)

From (6), the switch apparent power can be increased by:

- 1) Using devices with a higher voltage rating *allows* higher dc-bus voltage

- 2) Reducing the voltage overshoot occurring during switching allows higher dc-bus voltage

- 3) Using devices with a smaller on-state voltage drop increases device current carrying capacity

- 4) Reducing the junction to ambient thermal resistance *increases device current carrying capacity*

5) Reducing the switching losses (e.g. by reducing the switching frequency or using lower gate resistance) - increases device current carrying capacity

However, each action has a penalty: 1) higher voltage devices have larger channel resistance or on-state voltage drop (per unit area), 3) lower conduction loss devices have higher switching loss due to higher output capacitance [2], 4) the size of the heatsink may be restricted, 5) lower switching frequency increases the size of passive components. There is a direct trade-off between 2) and 5) since lower gate resistance reduces switching loss but increases the voltage overshoot. This paper considers what could be gained from implementing point 2 by using an AGD, i.e. effectively increasing the switch capacity, without changing the switching device itself or other characteristics of the power converter.

The AGDs presented in the literature are able to reduce the voltage overshoot occurring during switching, however it is shown that this leads to increased switching loss [41]. Therefore, for a given switch rating in a power converter, it is expected that the use of AGDs would enable a higher output voltage due to reduced voltage overshoot, but also that the thermally-limited maximum output current would reduce as a result of increased switching losses.

There are two factors that contribute to the increase of switching loss at higher dc-bus voltages:

- Simply increasing the dc-bus voltage causes switching losses to increase, since the product of drain current and drain-source voltage at any instant during switching is larger. This is the case even if the gate drive remains unchanged.

- 2) If the gate drive is an AGD which slows down the switching as the dc-bus voltage approaches the device voltage limit (in order to reduce the voltage overshoot), then the drain current and drain-source voltage overlap for longer, leading to a further increase in the switching energy loss.

Equation (6) shows that an AGD has potential to increase utilization of the switch if it enables an increase in dc-bus voltage great enough to counteract the increase in switching energy loss. In other words, the trade-off between the increased dc-bus voltage and the higher switching loss is investigated in terms of the switch capacity. Since F() is a complicated function dependent on many variables, an experimental approach is used here to investigate the impact of AGD on switch capacity across a range of switching frequencies. As switching loss is proportional to switching frequency, the hypothesis is that there will be a critical switching frequency below which the AGD will increase the capacity of the switch compared to a conventional gate drive.

#### III. EXPERIMENTAL METHODOLOGY

# A. Power circuit topology and hardware

Switch capacity is investigated using the diode-clamped IGBT switching circuit shown in Fig. 2. Independent control of dc-bus voltage and load current is achieved by using an adjustable power supply to support the dc-bus and an electronic load in constant-current mode as the load. A 600 V, 25 A IGBT

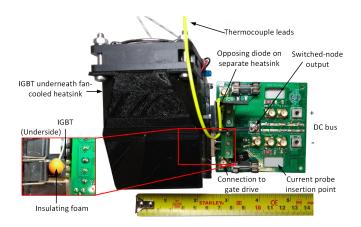

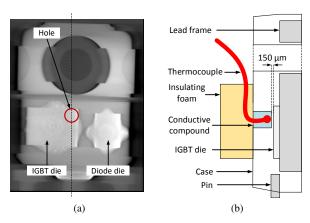

Fig. 3. Half-bridge circuit board, with separate heat-sinks for IGBT and opposing diode. Inset shows back-view of IGBT with thermocouple and insulating foam (explanation in Section III-E). Not shown are 2x 330 nF polypropylene capacitors on board underside.

(IRG4PC40KDPbF) and freewheeling diode ISL9R3060G2 are used for verification. Both are discrete devices in the TO247 package. The converter is run at a constant duty cycle of 0.3 throughout the experiment. The 0.3 ratio is selected because it corresponds to the maximum power capability  $(3\,\mathrm{kW})$  of the external power supply which is delivering power to the dc-bus, when the converter is operating at the highest voltage ( $\approx 400\,\mathrm{V}$ ) and load current (25 A).

During a switching event, the collector-emitter voltage of the IGBT,  $v_{ce}$ , and the cathode-anode voltage of the diode,  $v_{ka}$ , are measured with  $300\,\mathrm{MHz}$  100:1 passive voltage probes. A  $100\,\mathrm{MHz}$  N2783A Keysight current probe measures the IGBT collector current,  $i_c$ , and the diode current  $i_a$  is inferred from Kirchoff's current law:

$$i_a(t) = I_o - i_c(t) \tag{7}$$

The gate-emitter voltage of the IGBT,  $v_{ge}$ , is measured with a  $350\,\mathrm{MHz}$  10:1 passive probe, and all signals are sampled at  $1.25\,\mathrm{GS/s}$  using a  $250\,\mathrm{MHz}$ -bandwidth oscilloscope (PicoScope PS6402C). All measurement devices are de-skewed before running the experiment. The implementation of the converter is shown in Fig. 3.

#### B. Gate drive methods

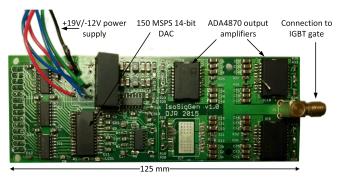

The gate drive unit used in this study is a custom-designed high-bandwidth voltage waveform generator. It allows a variety of drive voltage waveforms to be used to effect turn-on and turn-off of the IGBT. The gate drive is on a standalone circuit board, shown in Fig. 4, and connects to the half-bridge board via a 150 mm coaxial cable. Ideally, the gate drive voltage source would be connected to the IGBT gate through zero impedance to obtain direct control of the internal gate voltage. This would allow the gate voltage to be ramped at a controllable rate to tune the switching speed. However, because the gate is capacitive and the gate loop has parasitic inductance, a small series resistance is required to

Fig. 4. Gate drive printed circuit board providing digital to analogue conversion and amplification. This same hardware is used to produce all the waveforms in Fig. 1.

damp this LC oscillator. The gate resistor can be selected to achieve critical damping [42], i.e.

$$R_{g,\text{crit}} = 2\sqrt{\frac{L_g}{C_{\text{iss}}}} \tag{8}$$

where

$L_g$  parasitic inductance of the gate loop  $C_{\rm iss}$  input capacitance of IGBT gate.

The resistance of the gate mesh inside the IGBT also contributes to the damping, allowing the external resistor to have a value smaller than that given by (8). Here,  $1.4\,\Omega$  is added between the gate drive output and IGBT gate, which is found to obtain a good trade-off between switching speed and ringing. Smaller resistance would allow faster charging of the gate at the expense of increased overshoot and ringing at the gate.

Three gate drive waveforms are studied, as illustrated in Fig. 1. They are produced using the same gate drive hardware, depicted in Fig. 4, operating in different modes. The first gate drive mode (Fig. 1a) switches the IGBT as quickly as possible (so is referred to as the *Fast Gate Drive* or FGD, here). For the FGD, the voltage waveform undergoes a step change between the hold-off level of  $-3\,\mathrm{V}$  and the hold-on level of  $18\,\mathrm{V}$ , and relatively rapid switching results.

The other two modes are AGDs. The AGD gate voltage waveform is represented as a sequence of voltage points generated by MATLAB on a desktop PC. This sequence is defined by a vector  $\mathbf{x}$ , where Figs. 1b and 1c show the role that each element of  $\mathbf{x}$  has in defining the voltage waveform for each AGD case. In both cases, the reference is brought to a plateau below the IGBT threshold before switching in order to pre-charge the gate and make the IGBT sensitive to the upcoming AGD control.

In the first case, Fig. 1b, x has only one element, which defines the ramp time of the reference signal from pre-charge to hold-on/off level. Hence this case is termed the *Variable-Ramp AGD* or *VR-AGD*. The second case, termed the *Push-Pull AGD* or *PP-AGD* (Fig. 1c), introduces additional degrees of freedom to allow the driver to inject and extract charge from the gate during the switching event. Three variables make up x

Fig. 5. The method flow for determining the maximum apparent power obtainable using the PP-AGD. All combinations of load current, dc-bus voltage and gate parameters are tested. The methods for the FGD and VR-AGD are identical, except that the VR-AGD only has one gate parameter, and the FGD has no gate parameters.

in this case: the first two variables are times, the third variable is a voltage.

The resulting piecewise linear reference signal is sampled at 256 points, and stored on an FPGA. To initiate switching, the FPGA clocks out the sequence of points to a 14-bit DAC at  $150\,\mathrm{MS/s}$ , and the output from the DAC is amplified and level-shifted. The output amplifiers (three ADA4870) together provide current buffering up to  $3\,\mathrm{A}$  with an output swing of  $-10\,\mathrm{V}$  to  $18\,\mathrm{V}$ . More information about the gate drive hardware is provided in [41].

# C. Overview of method

Maximum IGBT capacity is found for each type of gate drive (FGD, VR-AGD and PP-AGD) by taking measurements of switching behaviour across a range of load currents and dcbus voltages. The load currents tested are  $18\,\mathrm{A}$ ,  $19\,\mathrm{A}$  ...  $25\,\mathrm{A}$ , and the dc-bus voltages tested are  $300\,\mathrm{V}$ ,  $310\,\mathrm{V}$  ...  $400\,\mathrm{V}$ . Every combination of load current and dc-bus voltage is tested.

Figure 5 illustrates the method for the PP-AGD case. Subscript i refers to the load current, subscript k refers to the dc-bus voltage, and  $x_{1,m}$ ,  $x_{2,n}$  and  $x_{3,p}$  refer to the gate drive parameters of the PP-AGD. Switching waveforms are captured for every combination of  $I_i$ ,  $V_k$ ,  $x_{1,m}$ ,  $x_{2,n}$ , and  $x_{3,p}$ , and these waveforms are processed to calculate the switching energy loss (from (4)) and peak voltage, denoted  $E(I_i, V_k, x_{1,m}, x_{2,n}, x_{3,p})$  respectively. Switching loss is converted into the resultant

steady-state IGBT junction temperature using (10) as explained later in Section III-E.

For each load current and dc-bus voltage, the best waveform of the AGD is selected by choosing the gate parameters  $x_{1,m}$ ,  $x_{2,n}$ , and  $x_{3,p}$  that minimise the resultant IGBT temperature while also not causing peak voltages to exceed the device limit, i.e.

$$\mathbf{x}^*(I_i, V_k) = [x_1^*, x_2^*, x_3^*]^{\mathsf{T}}$$

$$= \arg \min_{x_{1,m}, x_{2,n}, x_{3,p}} T(I_i, V_k, x_{1,m}, x_{2,n}, x_{3,p})$$

(9a)

$$T^*(I_i, V_k) = T(I_i, V_k, x_1^*, x_2^*, x_3^*)$$

(9b)

such that

$$\hat{v}(I_i, V_k, x_1^*, x_2^*, x_3^*) \le V^{\text{limit}}$$

(9c)

This leaves, for each  $I_i$ ,  $V_k$  combination, only a single temperature  $T^*(I_i,V_k)$  which is the lowest feasible IGBT temperature that the gate drive can obtain. If this temperature is less than the device limit, then the  $I_i$ ,  $V_k$  combination of load current and dc-bus voltage is acceptable. Therefore the combination  $I_i$ ,  $V_k$  is added to the set of acceptable operating points, which is called the *safe operating region* or *SOR* in this paper. However if  $T^*(I_i,V_k)$  is above the device limit this means that the gate drive has been unable to produce acceptable switching behaviour at the load current and dc-bus voltage, therefore the  $I_i$ ,  $V_k$  combination is not added to the SOR.

The maximum apparent power  $S^{\max}$  is obtained at the point in the SOR whose product of load current and dc-bus voltage is larger than at any other point in the SOR.  $S^{\max}$  and the load current and dc-bus voltage combination at which it occurs is saved for the PP-AGD.

The procedure is analogous for the FGD and the VR-AGD, the only difference being that there is only one gate drive parameter for the VR-AGD, and no gate parameters for the FGD. For the FGD,  $T(I_i,V_k)=T^*(I_i,V_k)$ , and only  $I_i,V_k$  combinations that result in both  $T(I_i,V_k)\leq T^{\text{limit}}$  and  $\hat{v}(I_i,V_k)\leq V^{\text{limit}}$  get added to the SOR.

At high dc-bus voltages, the SOR is dictated by the devices' rated blocking voltage limit, while at higher load currents the IGBT junction temperature constrains the SOR. The maximum IGBT capacities obtained using the different gate driving methods indicate the potential to increase IGBT capacity by expanding the SOR to higher voltages. It is reasonable to expect that the AGD SOR will be bounded by a higher dc-bus voltage (since AGDs reduce transient voltage overshoot) while the maximum load current boundary will be reduced (since using anything other than the fastest gate drive increases switching energy loss).

The IGBT and diode used in the experiment have a rated blocking voltage of  $600\,\mathrm{V}$  and maximum rated junction temperature of  $150\,^\circ\mathrm{C}$ . To allow the SOR to be determined using this procedure, without destroying the devices when the limits are exceeded, the peak diode/IGBT voltage  $V^{\mathrm{limit}}$  is taken as  $430\,\mathrm{V}$  and the maximum junction temperature limit  $T^{\mathrm{limit}}$  as  $100\,^\circ\mathrm{C}$  (a  $75\,^\circ\mathrm{C}$  rise above the ambient of  $25\,^\circ\mathrm{C}$ ). Because the switching loss of the IGBT is greater than that of the diode [43], only the thermal constraint on the IGBT is considered in this work.

TABLE I Approximate overshoot on a dc-bus of  $400\,\mathrm{V}$  for turn-on and turn-off with the FGD. Turn-on overshoot dominates in all

|      |      | Junction temperature |         |  |

|------|------|----------------------|---------|--|

|      |      | 75 °C                | 100 °C  |  |

| Load | 18 A | On 36 %              | On 32 % |  |

|      |      | Off 10 %             | Off 6 % |  |

|      | 24 A | On 30 %              | On 28 % |  |

|      |      | Off 12 %             | Off 8 % |  |

## D. Focus on turn-on control

Voltage overshoot during turn-on has been observed to exceed turn-off overshoot across the range of load currents investigated. Table I displays measured overshoot as a percentage of the 400 V dc-bus for two load currents and junction temperatures, when using FGD. Turn-on behaviour, therefore, has the greater impact on IGBT capacity, and for this reason both PP-AGD and VR-AGD approaches are investigated for turn-on. However experiments indicate that the PP-AGD has limited influence on turn-off behaviour [41], therefore only the VR-AGD is applied to turn-off. It is noted that even though turn-on creates the higher voltage overshoot during FGD switching, it is still useful to apply the VR-AGD to turn-off, since the FGD turn-off can produce a voltage overshoot greater than an optimised PP-AGD turn-on.

# E. Electrical measurement of switching loss used as proxy for junction temperature

Each AGD method requires the evaluation (by switching) of many different gate drive waveform shapes in order to find the optimal  $\mathbf{x}^*$ , as described above, each of which causes a different switching energy loss. Since the thermal time constant of the system is of the order of tens of seconds and several thousand  $\mathbf{x}$  need to be evaluated, it is not feasible to directly measure the resulting steady-state junction temperature of the IGBT by allowing the system to reach thermal steady-state for each  $\mathbf{x}$ . Therefore, the steady-state junction temperature rise that would result from continuous operation at a given  $\mathbf{x}$  is instead calculated from the device power loss and the junction-to-ambient thermal resistance as

$$\Delta T_j = P_{\text{loss}} R_{ja} = (P_c + P_{\text{sw}}) R_{ja} \tag{10}$$

where  $3.00\,^{\circ}\text{C/W}$  is taken for thermal resistance  $R_{ja}$ .

Device conduction loss is calculated (using a similar method as found in [44]) as

$$P_c = DI_o V_{\text{CE(on)}}. \tag{11}$$

On-state voltage, a function of junction temperature and load current, is found by quadratic interpolation of the datasheet values. Device switching loss  $P_{\rm sw}$  equals  $f_{\rm sw}E_{\rm sw}$  where the switching energy  $E_{\rm sw}$  is calculated using (4).

# F. Regulation of device temperature at $100\,^{\circ}\mathrm{C}$

As switching loss is strongly temperature dependent (increasing with temperature) [4], the IGBT must be kept at  $100\,^{\circ}\mathrm{C}$  for all trial x to allow the boundary of the SOR to

Fig. 6. IGBT temperature under closed-loop control during experiments.  $T_{\rm ref}$  is held at temperature limit of  $100\,{}^{\circ}{\rm C}$ .

Fig. 7. IGBT gate voltage pulse-train when performing AGD search. Temperature fluctuations are reduced by keeping the majority of switching events constant.

be determined. Device power loss varies with  $V_{\rm dc}$ ,  $I_o$  and  ${\bf x}$ , therefore the die temperature is held at  $100\,^{\circ}{\rm C}$  by varying the switching frequency as illustrated in Fig. 6. A PI controller compensates for changes in temperature that would otherwise occur when  $V_{\rm dc}$  or  $I_o$  change.

During the AGD grid search of  ${\bf x}$  at a given  $V_{\rm dc}$  and  $I_o$ , the average power dissipation is kept almost constant by only having a changing gate parameter vector  ${\bf x}$  for 1 out of 1000 switching transitions; the remaining switching edges use the constant fast gate drive shape (see Fig. 7). Therefore the actual die temperature is not significantly affected by the rapidly changing trial  ${\bf x}$ , and can be maintained at  $100\,{}^{\circ}{\rm C}$ .

To obtain accurate die temperature measurements, a type-T thermocouple is placed  $150\,\mu\mathrm{m}$  from the IGBT die. The package has been imaged using x-ray tomography (Fig. 8a) to locate the dies and bond-wires, a  $2.2\,\mathrm{mm}$  deep,  $2\,\mathrm{mm}$  diameter hole has been milled above the die, and the thermocouple is fixed in this hole with thermally conductive compound (schematically illustrated in Fig. 8b). Thermally insulating foam is fixed on the case above and around the hole.

Fig. 8. (a) Slice from an x-ray tomogram showing the silicon dies and the position of the milled hole. (b) Schematic side-view of TO-247 package showing thermocouple position relative to IGBT die.

## IV. RESULTS

# A. Safe operating regions at 7 kHz

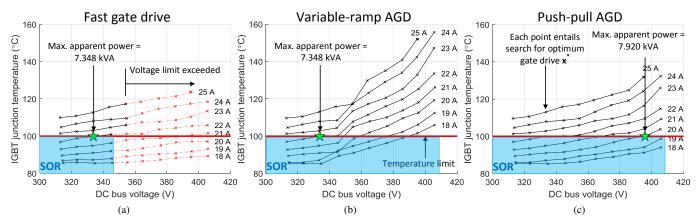

The IGBT steady-state junction temperature across a range of dc-bus voltages and load currents is presented in this section when using the three gate drive techniques. Temperatures are inferred using the  $\Delta T_i$  from (10) and (4) based on a switching frequency of 7 kHz and the ambient temperature of 25 °C. Fig. 9 shows the resulting IGBT temperatures plotted against dc-bus voltage, one plot for each type of gate drive. Each load current is plotted as a curve; the temperature limit of 100 °C is marked with a solid red line. Points with transient voltage overshoot above the limit of 430 V are joined with a dashed red line, whereas black solid lines connect points with overshoot below 430 V. Note that Fig. 9 contains information about the IGBT power loss (conduction plus switching loss) but loss measurements are transformed into resulting junction temperatures using (10) and (4) since it is the maximum temperature that limits the IGBT power capacity. In other words, the red line marking the limit of 100 °C indicates a constant IGBT power loss - in this case

$$\frac{100 \,^{\circ}\text{C} - 25 \,^{\circ}\text{C}}{3.00 \,^{\circ}\text{C/W}} = 25 \,\text{W}$$

(12)

The SOR for the FGD, Fig. 9a, is constrained by the voltage limit and the temperature limit. Large voltage peaks during switching limit the dc-bus voltage to less than  $350\,\mathrm{V}$ , while the maximum load current is  $22\,\mathrm{A}$ . The switch capacity in this case, obtained by operating at the maximum apparent power point marked by the green star, is  $S = V_{dc}I_o = (334\,\mathrm{V})\,(22\,\mathrm{A}) = 7.35\,\mathrm{kVA}$ .

For the VR-AGD, Fig. 9b, the voltage limit is respected at all points by slowing down the switching events. However, the penalty is larger switching loss leading to higher calculated steady-state die temperature. As a result, the point of maximum power is the same as for the FGD.

Fig. 9c reveals that the PP-AGD can, like the VR-AGD, respect the voltage limit all the way up to a 410 V dc-bus. However, the PP-AGD does this with less of an increase in switching loss, compared to the VR-AGD. This means the point of maximum apparent power is shifted to 396 V, 20 A, giving  $S=7.92~\rm kVA$ , an 8% increase in switch capacity compared to the other gate drives. This is due to the shape of the gate control reference allowing relatively fast switching without creating high transient voltages. The comparative performance of the gate drives at  $7~\rm kHz$  and  $T_j=100~\rm ^{\circ}C$  is summarised in Table II. The measured switching loss during turn-on is higher for the PP-AGD than for the FGD or VR-AGD since the *total* power loss is the same in all cases (25 W) and the conduction losses are lower for the PP-AGD maximum power point since it is at 20 A as opposed to 22 A.

# B. Switch capacity at different switching frequencies

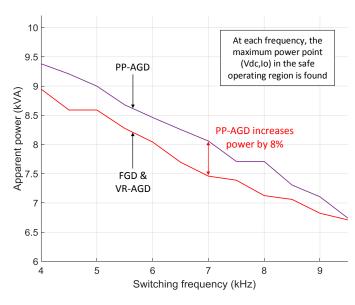

The results can be generalised over a range of switching frequencies. At each frequency, the SOR is calculated using (10) and (4) in the same way as in Section IV-A, and the maximum apparent power is found. The switch capacity across a range of frequencies is shown in Fig. 10 for the three gate

drive cases. The power drops as switching frequency increases due to the IGBT junction temperature limit.

In the 4-8 kHz range, the PP-AGD enables higher power for the reasons discussed above. At higher switching frequencies the increased losses from the AGD become more significant and the apparent powers begin to converge, as predicted by (6). The AGDs always perform at least as well as the FGD: at frequencies above 10 kHz the AGD waveforms resemble the FGD waveform, resulting in the same switching behaviour the AGDs never perform worse than the FGD.

It should be noted that the range of frequencies for which the PP-AGD outperforms the FGD depends on the thermal resistance between device and ambient, since it is the device temperature rise that limits the maximum load current when using PP-AGD at higher switching frequencies. Therefore, with lower thermal resistance the increased loss of the PP-AGD begins to dominate only at higher switching frequencies. For example, if the temperature rises are calculated using (10) with a thermal resistance of 2.00 °C/W instead of 3.00 °C/W the PP-AGD and FGD apparent powers converge at a switching frequency of approximately 19 kHz.

There is no switch capacity increase from using the VR-AGD: the peak apparent power from using it is never greater than that of the FGD. This is because, at the maximum-power point, the VR-AGD always ramps the gate reference as rapidly as the FGD, and therefore produces the same switching behaviour as the FGD. In other words, the FGD can be thought of as a special (fastest) case of the VR-AGD.

# C. Switching waveforms

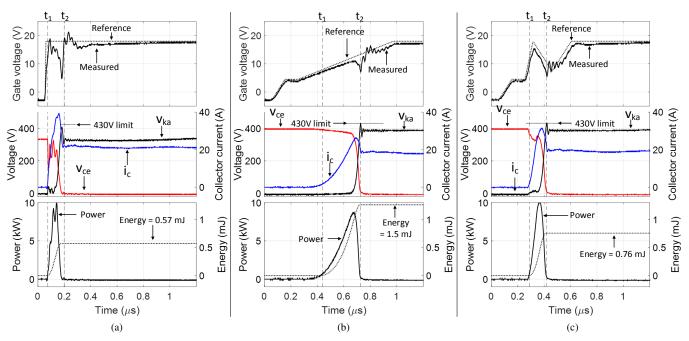

This section presents waveforms captured during switching events to illustrate the action of the three gate drives. Fig. 11a shows the turn-on behaviour of the circuit when operating with the FGD at the maximum power point identified from Fig. 9a (334 V, 22 A). IGBT gate voltage (reference and measured), measured collector-emitter voltage, and measured collector current are shown. In addition, the opposing diode cathode-anode voltage is shown, since the diode experiences the transient voltage peak during turn-on. It can be seen that the voltage peak across the diode is within the 430 V limit, since the dc-bus voltage is relatively low. The lowest plot in Fig. 11a shows the instantaneous power dissipation and cumulative energy dissipation in the IGBT. The turn-on loss is low at 0.57 mJ.

The corresponding switching waveforms for the VR-AGD at its maximum power operating point are the same as for the FGD, as discussed above, so are not shown. Instead, the the VR-AGD turn-on waveforms (Fig. 11b) are shown at the maximum power point of the PP-AGD (396 V, 20 A), for comparison against the PP-AGD waveforms (Fig. 11c). This is *not* the VR-AGD's maximum power operating point: it is outside its SOR. The rate of collector current increase is slower for the VR-AGD than for the PP-AGD. This has a two-fold effect on the switching loss: it takes longer for the diode to become reverse biased and allow the collector-emitter voltage to fall (longer switching time); and the collector-emitter voltage is depressed less by the voltage drop across the parasitic

Fig. 9. IGBT junction temperature rise across operating point range, when switching with (a) FGD, (b) VR-AGD, and (c) PP-AGD. Solid lines join points with voltage peaks less than the limit of 430 V, dashed lines indicate unsafe area with voltage overshoot greater than the limit. The green star marks the point in the SOR at which the apparent power is maximised.

|              | E <sub>on</sub> (mJ) | V <sub>dc</sub> (V) | I <sub>o</sub> (A) | P <sub>A</sub> (kVA) | P <sub>A</sub> (%) | x <sub>1</sub> (ns) | x <sub>2</sub> (ns) | x <sub>3</sub> (V) |

|--------------|----------------------|---------------------|--------------------|----------------------|--------------------|---------------------|---------------------|--------------------|

| FGD & VR-AGD | 0.57                 | 334                 | 22                 | 7.35                 | 100 %              | 1 (min. limit)      | -                   | _                  |

| PP-AGD       | 0.76                 | 396                 | 20                 | 7.92                 | 108 %              | 61                  | 290                 | 7.4                |

Fig. 10. Maximum apparent power for the three gate drive cases across a range of frequencies. At each frequency, the dc-bus voltage / load current combination that leads to the highest apparent power is chosen from the SOR.

inductance of the commutation path. Both factors lead to  $1.5\,\mathrm{mJ}$  of switching loss, which causes the unacceptably high calculated junction temperature for the VR-AGD. The PP-AGD, in contrast, reduces voltage overshoot while achieving a lower switching loss of  $0.76\,\mathrm{mJ}$ . The PP-AGD's extra degrees of freedom allow independent control of the collector current rise and the decay of the diode reverse recovery current. This means that the collector current can increase rapidly at first (reducing switching loss) and the peak  $\mathrm{d}i/\mathrm{d}t$  when the reverse recovery current decays can be reduced (creating smaller voltage overshoot).

# V. DISCUSSION

The AGD techniques investigated in this paper, compared with gate drives that switch as fast as possible, can reduce the peak voltage across the power devices and allow the converter to be operated at higher dc-bus voltages. However, only the more advanced AGD, the PP-AGD, is found to increase the switch power handling capability. On the other hand, the simpler VR-AGD results in higher switching losses which limit the switch power capacity. The VR-AGD is similar to a gate drive where the rate of gate charge/discharge is controlled by a series gate resistance that is varied between, but not during, the switching events. These results indicate that a variable gate resistance alone has limited utility, and cannot increase switch capacity. The better performance of the PP-AGD suggests that there is merit in a more advanced gate drive compared to the simpler option of implementing an adjustable gate resistance.

It should be recognized that the PP-AGD formulation of the gate drive is not necessarily the best possible, and there may be more complex gate waveforms that achieve greater performance improvements. The PP-AGD as presented here was chosen as a good trade-off between complexity (number of parameters to tune, i.e. experiment run-time) and control over switching behaviour. The theory here has been validated for a single device in a particular converter layout. It is expected that the benefits of AGD will be greater for layouts with large parasitic inductance between dc-link capacitors and the power switches. Conversely, careful power circuit layout may be sufficient to reduce the problem of overshoot without using AGD.

The procedure for finding the best reference waveform during operation is not considered in this paper. The exhaustive search for  $\mathbf{x}^*$  conducted here results in switching voltage

Fig. 11. Turn-on waveforms when switching with the three gate drives. (a) FGD at 334 V 22 A, (b) VR-AGD at 396 V 20 A, and (c) PP-AGD at 396 V 20 A. Plots (a) and (c) are at the respective maximum apparent power operating points for those gate drives, and illustrate acceptable switching behaviour. Plot (b) illustrates the VR-AGD keeping voltage overshoot below the 430 V limit but incurring a high switching loss.

overshoot that sometimes exceeds the device limit, and it is only the choice of a conservative limit that makes this approach possible. It is necessary in practical systems to search in a way that does not violate the peak voltage constraint.

The exact moment when the load current commutates between the switching devices depends on the variable  $\mathbf{x}$ . Therefore, for synchronous switching the deadtime between the 'on' PWM signals for two devices in a leg may need to be increased to guarantee the absence of shoot-through for all  $\mathbf{x}$ . Use of an adaptive deadtime mechanism such as that proposed in [36] could address this. Similarly, the duty cycle of the switched device will vary slightly with  $\mathbf{x}$  as the instant of switching changes. However, the effect of this is small: the maximum variation in on-time observed during experiments is less than  $1\,\mu\text{s}$ , causing duty cycle to vary by less than  $1\,\%$  when switching at  $10\,\text{kHz}$ .

The advantage of the improved switch capacity becomes apparent when considering converters with a transformer at the output, for example the three-phase grid-tied inverter depicted in Fig. 12. The transformer provides a degree of freedom to optimally match  $V_{\rm dc}$  to grid voltage  $V_{\rm LL}$  at the design stage by selecting the appropriate turns ratio n. AGD allows higher  $V_{\rm dc}$  and therefore lower n, reducing  $nI_o$  and allowing higher output power for a given three-phase bridge.

Therefore, the AGD can be thought of as providing 'free silicon' by increasing the capacity of a given switch, meaning either more power can be processed by the same device, or a smaller device can be chosen to process a particular power level. The better switch utilization may imply higher converter power density if the power semiconductor devices and their heatsinks significantly contribute to the overall volume of the converter. This would have to be factored against the additional

Fig. 12. A grid-tied three-phase inverter, where turns ratio n allows matching of dc-bus voltage to grid voltage.

volume and weight of the AGD hardware compared to a conventional gate drive.

# VI. CONCLUSION

This paper proposes the first framework for evaluating the impact of an active gate drive on the power processing capability of an IGBT. The power capacity of the device is experimentally shown to increase by up to 8% at frequencies between 4 and 8 kHz (Fig. 10) when using the PP-AGD in a buck converter. The AGD method enables operation of a given converter at maximal dc-link voltages by limiting the voltage overshoot and enlarging the safe operating area of the device (Figs. 9 and 11). Consequently, the application of AGD may result in increased power density of power electronic systems.

# ACKNOWLEDGMENT

The authors are grateful to Dr Andrew Lui of the Oxford Materials Characterisation Service for producing the x-ray tomogram presented in this work.

#### REFERENCES

- J. W. Kolar, U. Drofenik, J. Biela, M. L. Heldwein, H. Ertl, T. Friedli, and S. D. Round, "PWM Converter Power Density Barriers," in 2007 Power Conversion Conference - Nagoya. IEEE, Apr 2007, pp. P–9– P–29.

- [2] I. Laird, X. Yuan, J. Scoltock, and A. J. Forsyth, "A Design Optimization Tool for Maximizing the Power Density of 3-Phase DCAC Converters Using Silicon Carbide (SiC) Devices," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 2913–2932, Apr 2018.

- [3] A. Hefner, "An investigation of the drive circuit requirements for the power insulated gate bipolar transistor (IGBT)," *IEEE Transactions on Power Electronics*, vol. 6, no. 2, pp. 208–219, Apr 1991.

- [4] D. A. Neamen, Semiconductor Physics and Devices: Basic Principles, 2nd ed. Chicago/London: Irwin, 1997.

- [5] P. Hofer-Noser and N. Karrer, "Monitoring of paralleled IGBT/diode modules," *IEEE Transactions on Power Electronics*, vol. 14, no. 3, pp. 438–444, May 1999.

- [6] P. Hofer, N. Karrer, and C. Gerster, "Paralleling intelligent IGBT power modules with active gate-controlled current balancing," in *PESC Record.* 27th Annual IEEE Power Electronics Specialists Conference, vol. 2. IEEE, 1996, pp. 1312–1316.

- [7] D. Bortis, J. Biela, and J. Kolar, "Active Gate Control for Current Balancing of Parallel-Connected IGBT Modules in Solid-State Modulators," *IEEE Transactions on Plasma Science*, vol. 36, no. 5, pp. 2632–2637, Oct 2008.

- [8] P. Palmer and H. Rajamani, "Active Voltage Control of IGBTs for High Power Applications," *IEEE Transactions on Power Electronics*, vol. 19, no. 4, pp. 894–901, Jul 2004.

- [9] Y. Wang, P. Palmer, T. Lim, S. Finney, and A. Bryant, "Real-time Optimization of IGBT/Diode Cell Switching under Active Voltage Control," in *Conference Record of the 2006 IEEE Industry Applications Conference Forty-First IAS Annual Meeting*, vol. 5. IEEE, Oct 2006, pp. 2262–2268.

- [10] A. T. Bryant, Y. Wang, S. J. Finney, T. C. Lim, and P. R. Palmer, "Numerical Optimization of an Active Voltage Controller for High-Power IGBT Converters," *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 374–383, Mar 2007.

- [11] T. C. Lim, B. W. Williams, S. J. Finney, and P. R. Palmer, "Series-Connected IGBTs Using Active Voltage Control Technique," *IEEE Transactions on Power Electronics*, vol. 28, no. 8, pp. 4083–4103, Aug 2013.

- [12] H. C. P. Dymond, J. Wang, D. Liu, J. J. O. Dalton, N. McNeill, D. Pamunuwa, S. J. Hollis, and B. H. Stark, "A 6.7-GHz Active Gate Driver for GaN FETs to Combat Overshoot, Ringing, and EMI," *IEEE Transactions on Power Electronics*, vol. 33, no. 1, pp. 581–594, Jan 2018.

- [13] A. Tripathi, K. Mainali, S. Madhusoodhanan, A. Yadav, K. Vechalapu, and S. Bhattacharya, "A MV intelligent gate driver for 15kV SiC IGBT and 10kV SiC MOSFET," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC). IEEE, Mar 2016, pp. 2076–2082.

- [14] Z. Zeng and X. Li, "Comparative Study on Multiple Degrees of Freedom of Gate Drivers for Transient Behavior Regulation of SiC MOSFET," *IEEE Transactions on Power Electronics*, vol. 33, no. 10, 2018.

- [15] Z. Zhang, J. Dix, F. F. Wang, B. J. Blalock, D. Costinett, and L. M. Tolbert, "Intelligent Gate Drive for Fast Switching and Crosstalk Suppression of SiC Devices," *IEEE Transactions on Power Electronics*, vol. 32, no. 12, pp. 9319–9332, Dec 2017.

- [16] A. P. Camacho, V. Sala, H. Ghorbani, and J. L. R. Martinez, "A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 11, pp. 9032– 9042, Nov 2017.

- [17] P. Nayak and K. Hatua, "Parasitic Inductance and Capacitance-Assisted Active Gate Driving Technique to Minimize Switching Loss of SiC MOSFET," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 10, pp. 8288–8298, Oct 2017.

- [18] ——, "Active Gate Driving Technique for a 1200 V SiC MOSFET to Minimize Detrimental Effects of Parasitic Inductance in the Converter Layout," *IEEE Transactions on Industry Applications*, vol. 54, no. 2, pp. 1622–1633, Mar 2018.

- [19] F. Zhang, X. Yang, Y. Ren, L. Feng, W. Chen, and Y. Pei, "A Hybrid Active Gate Drive for Switching Loss Reduction and Voltage Balancing of Series-Connected IGBTs," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7469–7481, Oct 2017.

- [20] E. Velander, L. Kruse, T. L. Wiik, A. Wiberg, J. Colmenares, and H.-P. Nee, "An IGBT Turn-ON Concept Offering Low Losses Under Motor Drive dv/dt Constraints Based on Diode Current Adaption," *IEEE*

- Transactions on Power Electronics, vol. 33, no. 2, pp. 1143–1153, Feb 2018

- [21] Y. Lobsiger and J. W. Kolar, "Closed-Loop di/dt and dv/dt IGBT Gate Driver," *IEEE Transactions on Power Electronics*, vol. 30, no. 6, pp. 3402–3417, Jun 2015.

- [22] —, "Stability and Robustness Analysis of d/dt-Closed-Loop IGBT Gate Drive," in Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, Mar 2013, pp. 2682–2689.

- [23] —, "Closed-Loop di/dt & dv/dt Control and Dead Time Minimization of IGBTs in Bridge Leg Configuration," in Control and Modeling for Power Electronics (COMPEL), Long Beach, CA, Jun 2013, pp. 1–7.

- [24] ——, "Closed-Loop IGBT Gate Drive Featuring Highly Dynamic d i / d t and d v / d t Control," 2012 IEEE Energy Conversion Congress and Exposition, ECCE 2012, no. 5, pp. 4754–4761, Sep 2012.

- [25] L. Shu, J. Zhang, F. Peng, and Z. Chen, "Active Current Source IGBT Gate Drive with Closed-Loop di/dt and dv/dt Control," *IEEE Transactions on Power Electronics*, vol. 32, no. 5, pp. 3787–3796, May 2017.

- [26] L. Chen and F. Z. Peng, "Closed-Loop Gate Drive for High Power IG-BTs," in *Applied Power Electronics Conference and Exposition (APEC)*. Washington, DC: IEEE, Feb 2009, pp. 1331–1337.

- [27] H. Riazmontazer and S. K. Mazumder, "Optically switched-drive-based unified independent dv/dt and di/dt control for turn-off transition of power MOSFETs," *IEEE Transactions on Power Electronics*, vol. 30, no. 4, pp. 2338–2349, 2015.

- [28] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, and B. J. Blalock, "A di/dt Feedback-Based Active Gate Driver for Smart Switching and Fast Overcurrent Protection of IGBT Modules," *IEEE Transactions on Power Electronics*, vol. 29, no. 7, pp. 3720–3732, Jul 2014.

- [29] D. J. Rogers and B. Murmann, "Digital active gate drives using sequential optimization," in *Applied Power Electronics Conference and Exposition (APEC)*. IEEE, Mar 2016, pp. 1650–1656.

- [30] T. Gluck, M. Blank, D. Buchl, and A. Kugi, "Convex Constrained Iterative Learning Control Using Projection: Application to a Smart Power Switch," *IEEE Transactions on Control Systems Technology*, vol. 26, no. 5, pp. 1818–1825, Sep 2018.

- [31] Y. Yang, Y. Wen, and Y. Gao, "A Novel Active Gate Driver for Improving Switching Performance of High-Power SiC MOSFET Modules," IEEE Transactions on Power Electronics, pp. 1–1, 2018.

- [32] K. Miyazaki, M. Takamiya, and T. Sakurai, "Automatic Optimization of IGBT Gate Driving Waveform Using Simulated Annealing for Programmable Gate Driver IC," in *Energy Conversion Congress and Exposition (ECCE)*. Milwaukee, WI: IEEE, Sep 2016, pp. 1–6.

- [33] K. Miyazaki, S. Abe, M. Tsukuda, I. Omura, K. Wada, M. Takamiya, and T. Sakurai, "General-Purpose Clocked Gate Driver IC With Programmable 63-Level Drivability to Optimize Overshoot and Energy Loss in Switching by a Simulated Annealing Algorithm," *IEEE Transactions on Industry Applications*, vol. 53, no. 3, pp. 2350–2357, May 2017.

- [34] Y. Shan Cheng, T. Mannen, K. Wada, K. Miyazaki, M. Takamiya, and T. Sakurai, "Optimization Platform to Find a Switching Pattern of Digital Active Gate Drive for Full-Bridge Inverter Circuit," in 2018 IEEE Energy Conversion Congress and Exposition (ECCE). IEEE, Sep 2018, pp. 6441–6447.

- [35] H. Obara, K. Wada, K. Miyazaki, M. Takamiya, and T. Sakurai, "Active Gate Control in Half-Bridge Inverters Using Programmable Gate Driver ICs to Improve Both Surge Voltage and Converter Efficiency," *IEEE Transactions on Industry Applications*, vol. 54, no. 5, pp. 4603–4611, Sep 2018.

- [36] Z. Zhang, H. Lu, D. J. Costinett, F. Wang, L. M. Tolbert, and B. J. Blalock, "Model-Based Dead Time Optimization for Voltage-Source Converters Utilizing Silicon Carbide Semiconductors," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8833–8844, Nov 2017.

- [37] M. Blank, T. Gluck, A. Kugi, and H.-P. Kreuter, "Digital slew rate and s-shape control for smart power switches to reduce EMI generation," *IEEE Transactions on Power Electronics*, vol. 30, pp. 5170–5180, Sep 2015.

- [38] L. Dang, H. Kuhn, and A. Mertens, "Digital Adaptive Driving Strategies for High-Voltage IGBTs," *IEEE Transactions on Industry Applications*, vol. 49, no. 4, pp. 1628–1636, Jul 2013.

- [39] V. Subotskaya, V. Mihal, M. Tulupov, and B. Deutschmann, "Optimized gate driver for high-frequency buck converter," e & i Elektrotechnik und Informationstechnik, vol. 135, no. 1, pp. 40–47, Feb 2018.

- [40] C. Xiao, G. Chen, and W. G. H. Odendaal, "Overview of Power Loss Measurement Techniques in Power Electronics Systems," *IEEE Transactions on Industry Applications*, vol. 43, no. 3, pp. 657–664, 2007.

- [41] G. Jones and D. Rogers, "Investigation of IGBT switching energy loss and peak overvoltage using digital active gate drives," in 2017 IEEE 18th

- Workshop on Control and Modeling for Power Electronics, COMPEL 2017. Stanford, CA: IEEE, Jul 2017, pp. 1–8.

- [42] L. Balogh, "Fundamentals of MOSFET and IGBT Gate Driver Circuits Texas Instruments," no. April 2002, pp. 1–48, 2017.

- [43] A. Bryant, D. Jaeggi, G. Parks, and P. Palmer, "The influence of operating conditions on multi-objective optimization of power electronic devices and circuits," in *Fourtieth IAS Annual Meeting. Conference Record of the 2005 Industry Applications Conference*, 2005., vol. 2. IEEE, 2005, pp. 1449–1456.

- [44] P. Anthony, N. McNeill, and D. Holliday, "High-speed resonant gate driver with controlled peak gate voltage for silicon carbide MOSFETs," *IEEE Transactions on Industry Applications*, 2014.

Gwilym T. Jones (S17) received the M.Eng. degree in Integrated Engineering from Cardiff University, UK, in 2016. He is currently studying for the D.Phil. degree in engineering science at the University of Oxford, UK. From 2013 to 2015, he was an IET Power Academy placement student at the Culham Centre for Fusion Energy. His research interests include enhanced control of transistor switching behaviour, power electronics for modular battery energy storage, and pulsed-power electronics for nuclear fusion applications. Gwilym was a recipient

of the Best Paper Prize at the 2017 IEEE COMPEL conference.

Yam P. Siwakoti (S10M14SM18) received the B.Tech. degree in electrical engineering from the National Institute of Technology, Hamirpur, India, in 2005, the M.E. degree in electrical power engineering from the Norwegian University of Science and Technology, Trondheim, Norway, and Kathmandu University, Dhulikhel, Nepal, in 2010, and the Ph.D. degree in Electronic Engineering from Macquarie University, Sydney, Australia, in 2014. He was a postdoctoral fellow at the Department of Energy Technology, Aalborg University, Denmark (2014-

2016). He was a visiting scientist at the Fraunhofer Institute for Solar Energy Systems, Freiburg, Germany (2017/2018). He is also a recipient of the prestigious Green Talent Award from the Federal Ministry of Education and Research, Germany in 2016. Currently he is a Senior Lecturer in the Faculty of Engineering and Information Technology, University of Technology Sydney, Australia. He serves as an Associate Editor of three major journals of IEEE (IEEE Transactions on Power Electronics, IEEE Transactions on Industrial Electronics and IEEE Journal of Emerging and Selected Topics in Power Electronics) and the IET Power Electronics. He is also a peer review college member of Engineering and Physical Science Research Council (EPSRC), UK.

Daniel J. Rogers (M09, SM19) is an Associate Professor in the Department of Engineering Science at the University of Oxford, UK. He received the M.Eng. and Ph.D. degrees in Electrical and Electronic Engineering from Imperial College London, UK, in 2007 and 2011 respectively. He conducts research in collaboration with industry and is an investigator on UK EPSRC research projects in the areas of power electronics, grid-scale energy storage and microgrids. Dans research interests in power electronic range from active control of transistor

switching, to circuit and control system design, through to novel applications enabled by wide-bandgap devices.