UNIVERSITY OF TECHNOLOGY SYDNEY Faculty of Engineering and Information Technology

# LOW-COMPLEXITY DIGITAL MODEM DESIGN AND IMPLEMENTATION FOR HIGH-SPEED AERIAL BACKBONES

by

Hao Zhang

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

Doctor of Philosophy

Sydney, Australia

2019

### Certificate of Authorship/Originality

I, Hao Zhang, declare that this thesis is submitted in fulfilment of the requirements for the award of PhD, in the School of Electrical and Data Engineering, Faculty of Engineering and Information Technology at the University of Technology Sydney.

This thesis is wholly my own work unless otherwise reference or acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis.

This document has not been submitted for qualifications at any other academic institution.

This research is supported by the Australian Government Research Training Program.

Production Note: Signature: Signature removed prior to publication.

Date:

10/02/2020

#### ABSTRACT

Wireless communication technology is moving towards the integration of terrestrial networks with space networks. However, a number of grand technological challenges have to be overcome for such integration. This thesis addresses some of these challenges and develops efficient and effective solutions to successfully achieve a high-speed aerial backbone link.

The first challenge is the signal synchronization in presence of large carrier frequency offset (CFO). In this thesis, new methods for preamble-aided coarse timing estimation are investigated. Integrated with simple auto-correlation operation, CFO can be estimated and compensated for better frame synchronization in high-speed aerial backbone links. Moreover, the optimized algorithms can be implemented with low-complexity. Simulation result shows that the proposed method can capture tens of Mega Hertz CFO with rapid convergence.

The In-phase and Quadrature-phase (I/Q) imbalance is another significant factor which impacts on practical wideband wireless backbone systems. An effective algorithm is proposed to estimate I/Q imbalance with specially designed training sequence. After I/Q imbalance estimation, I/Q imbalance compensation is combined with channel equalization as well as sampling rate conversion to form the receiver filters of the system. Simulation result shows that the estimated receiver and transmitter imbalance coefficients are quite close to the true values and the joint algorithm can achieve the desired performance.

Analog-to-digital and digital-to-analog conversion devices for signals with very large bandwidth are not always available due to technical or cost issues. In this thesis, a dual pulse shaping (DPS) transmission scheme is proposed, which can achieve full Nyquist rate transmission with only a half of the sampling rate for each of the two data streams. The condition for cross-symbol interference free transmission is derived and validated for two classes of ideal complementary Nyquist pulses. Structures of the DPS transmitter and receiver are described and low-complexity equalization techniques tailored to DPS are provided as well. The simulation results with two sets of practical dual spectral shaping pulses verify the effectiveness of the proposed scheme.

Finally, the design and implementation of a high-speed low-complexity digital modem for wireless communications at 0.325 terahertz (THz) are presented. The requirements, architecture and signal processing modules of the system are described. Some key strategies are applied to ensure the proposed low complexity algorithms can be implemented in real-time field-programmable gate array (FPGA) platform. The digital modem implementation and the integrations with IF modules and RF frontend are described and the experimental results of them are provided.

### Acknowledgements

First of all, I would like to express my gratitude to my supervisor Prof. Xiaojing Huang for his continual support and encouragement of my study and PhD research. From employment as a casual staff member in 2015 to undertaking a PhD under him in 2016, I have been grateful for his patient guidance during my journey.

I would also like to thank my co-supervisor Prof. Jay Guo for sharing his valuable experience in support of my research, and I also want to thank A/Prof. Jian Andrew Zhang for his guidance and practical advice in my study period.

Keith Bengston, David Humphrey and Joseph Pathikulangara taught me the finer points of software and firmware design during my time at CSIRO. I am grateful for their advice with difficult technical problems.

Along my path I had many excellent mentors: Dr. Peiyuan Qin, Dr. Can Ding, Dr. Ting Zhang, Dr. Shenghong Li, Dr. Wei Lin, Dr. He Zhu, Dr. Hang Li and Dr. Tom Wang. Collaborating with them has broadened my horizons.

The example of my colleagues Anh Tuyen Le, Yijiang Nan, Shulin Chen, Haihan Sun and Hongyang Zhang provided inspiration that helped me to overcome many difficulties.

Last but not least, I would like to express my gratitude to my family: my father Sumin Zhang, my mother Meiying Guo and my older brother Fei Zhang for their love and wholehearted encouragement. To my loving, encouraging and patient wife Jieqiong Zhang, without whom none of this would have happened: your faithful support during the long process of undertaking a PhD has made all this possible.

> Hao Zhang August, 2019

### List of Publications

#### **Journal Papers**

J-1. Hao Zhang, Xiaojing Huang, Jian Andrew Zhang and Y. Jay Guo, "Dual Pulse Shaping Transmission and Equalization for High-Speed Wideband Wireless Communication Systems", submitted to IEEE Transactions on Circuits and Systems I: Regular Papers.

#### Patent

P-1. Xiaojing Huang, Y. Jay Guo, Jian (Andrew) Zhang and Hao Zhang, "Dual Pulse Shaping Transmission System and Method," AU2018900096, filed on 12 January 2018.

#### **Conference** Papers

- C-1. Hao Zhang, Xiaojing Huang, and Y. Jay Guo, "A 20 Gbps Digital Modem for High-Speed Wireless Backhaul Applications," presented at the 2017 IEEE 85th Vehicular Technology Conference (VTC2017-Spring), Sydney, Australia, 4 - 7 June 2017.

- C-2. Hao Zhang, Xiaojing Huang, and Y. Jay Guo, "Low-Complexity Digital Modem Implementation for High-Speed Point-to-Point Wireless Communication," presented at the 18th International Symposium on Communications and Information Technologies (ISCIT2018), Bangkok, Thailand, 26 - 29 September 2018.

- C-3. Hao Zhang, Xiaojing Huang, Jian Andrew Zhang and Y. Jay Guo, et al, "A High-Speed Low-Cost Millimeter Wave System with Dual Pulse Shaping Transmission and Symbol Rate Equalization Techniques," presented at the IEEE International Symposium on Circuits and Systems (ISCAS2019), Sapporo, Japan, 26-29 May 2019.

- C-4. Hao Zhang, Xiaojing Huang, Ting Zhang, Jian Andrew Zhang and Y. Jay Guo, "A 30 Gbps Low Complexity and Real-Time Digital Modem for Wireless Communications at 0.325 THz," presented at the 19th International Symposium on Communications and Information Technologies (ISCIT2019), Ho Chi Minh City, Vietnam, 25 - 27 September 2019.

- C-5. Xiaojing Huang, Hao Zhang, Jian Andrew Zhang and Y. Jay Guo, et al, "Dual Pulse Shaping Transmission with complementary Nyquist Pulses," presented at the 2019 IEEE 90th Vehicular Technology Conference (VTC2019-Fall), Honolulu, Hawaii, USA, 22-25 September, 2019.

# Contents

|   | Certificate                                        | ii  |

|---|----------------------------------------------------|-----|

|   | Abstract                                           | iii |

|   | Acknowledgments                                    | V   |

|   | List of Publications                               | vi  |

|   | List of Figures                                    | xii |

|   | Abbreviation                                       | xvi |

|   | Notation                                           | xx  |

| 1 | Introduction                                       | 1   |

|   | 1.1 Background                                     | . 1 |

|   | 1.2 Challenges for ISTN System                     | 3   |

|   | 1.3 Thesis Organization                            | 6   |

| 2 | Synchronization in Presence of Large CFO           | 9   |

|   | 2.1 Introduction and Literature Review             | 9   |

|   | 2.2 Training Sequence Design                       | 11  |

|   | 2.3 Autocorrelation Implementation                 | 13  |

|   | 2.4 Simulation Results                             | 16  |

|   | 2.5 Conclusions                                    | 18  |

| 3 | Joint I/Q Imbalance Compensation and Channel Equal | -   |

|   | ization in SRC Receiver Filters                    | 20  |

|          | 3.1 | Introdu | action and Literature Review                  | 20 |

|----------|-----|---------|-----------------------------------------------|----|

|          | 3.2 | System  | and Signal Models                             | 23 |

|          | 3.3 | I/Q Im  | balance Compensation and Channel Equalization | 25 |

|          | 3.4 | Simulat | tion Results                                  | 31 |

|          | 3.5 | Conclus | sions                                         | 34 |

| 4        | Du  | ual Pu  | lse Shaping Transmission System and Method    | 36 |

|          | 4.1 | Introdu | action and Literature Review                  | 36 |

|          | 4.2 | DPS wi  | ith Complementary Nyquist Pulses              | 39 |

|          |     | 4.2.1   | Nyquist Theorem                               | 39 |

|          |     | 4.2.2   | Complementary Nyquist Pulses                  | 39 |

|          |     | 4.2.3   | CSI-Free Conditions for DPS Transmission      | 41 |

|          |     | 4.2.4   | Ideal DPS Pulses                              | 43 |

|          | 4.3 | Equaliz | ation with Non-Ideal Pulses                   | 47 |

|          |     | 4.3.1   | System and Signal Models                      | 48 |

|          |     | 4.3.2   | Received and Equalized Signal Models          | 49 |

|          |     | 4.3.3   | ZF Equalization                               | 52 |

|          |     | 4.3.4   | MMSE Equalization                             | 55 |

|          | 4.4 | Simulat | tion Results                                  | 56 |

|          | 4.5 | Conclus | sion                                          | 59 |

| <b>5</b> | Hi  | gh-Sp   | eed Digital Modem Implementation for Wire-    |    |

|          | les | s Com   | nmunications at 0.325 THz                     | 61 |

|          | 5.1 | Introdu | action and Literature Review                  | 61 |

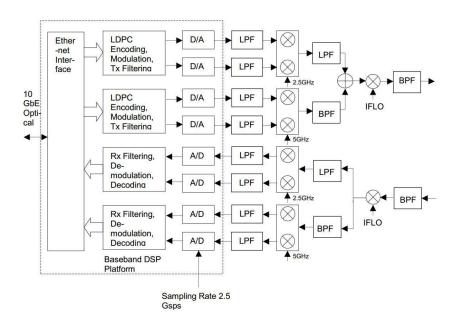

|          | 5.2 | System  | Description                                   | 63 |

|          |     | 5.2.1   | System Requirements                           | 63 |

|                   | 5.2.2    | System Architecture                          | 64 |

|-------------------|----------|----------------------------------------------|----|

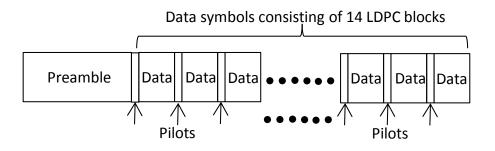

|                   | 5.2.3    | Physical Layer Protocol                      | 65 |

| 5.3 S             | Signal I | Processing Modules                           | 67 |

|                   | 5.3.1    | Transmitter Signal Processing                | 67 |

|                   | 5.3.2    | Receiver Signal Processing                   | 67 |

| 5.4 E             | Etherne  | et Interface                                 | 68 |

|                   | 5.4.1    | Functional Overview                          | 68 |

|                   | 5.4.2    | Interfacing Radio PCS                        | 69 |

|                   | 5.4.3    | Ethernet Interface Architecture              | 70 |

| 5.5 I             | mplem    | entation of Transmitter and Receiver Filters | 71 |

|                   | 5.5.1    | Transmitter Filter                           | 71 |

|                   | 5.5.2    | Receiver Filter                              | 73 |

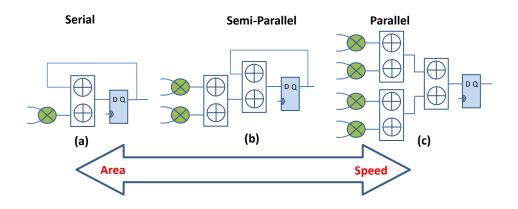

| 5.6 F             | Key Str  | rategies for Implementation on FPGA          | 74 |

|                   | 5.6.1    | FPGA                                         | 74 |

|                   | 5.6.2    | Key Strategies                               | 78 |

| 5.7 I             | mplem    | entation Results                             | 82 |

| 5.8 E             | Experin  | nental Results of Digital Modem              | 84 |

| 5.9 I             | ntegrat  | tion with IF Module                          | 85 |

|                   | 5.9.1    | Test Setup                                   | 85 |

|                   | 5.9.2    | Experimental Results                         | 87 |

|                   | 5.9.3    | Channel Pre-equalization                     | 89 |

|                   | 5.9.4    | BER Test with Real-Time Ethernet Traffic     | 92 |

| $5.10\mathrm{Iz}$ | ntegrat  | tion with RF Frontend                        | 98 |

|                   | 5.10.1   | Architectures of THz RF Frontend             | 98 |

|   | 5.10.2 Test Setup and Experimental Results                              | 99  |

|---|-------------------------------------------------------------------------|-----|

|   | 5.11 Conclusion                                                         | 101 |

| 6 | Conclusions and Future Work                                             | 103 |

|   | 6.1 Summary of Contributions                                            | 103 |

|   | 6.2 Future Work                                                         | 105 |

|   | 6.2.1 Dealing with Nonlinear Channels                                   | 105 |

|   | $6.2.2$ Achieving Higher-Speed Wireless Communication Systems $\ . \ .$ | 106 |

|   | 6.2.3 Reducing System Complexity                                        | 106 |

|   | Bibliography 1                                                          | 108 |

xi

# List of Figures

| 2.1 | Training sequence design                                                                                                                               | 13 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Using autocorrelation for coarse timing                                                                                                                | 13 |

| 2.3 | CFO=30 MHz estimation under 8 dB SNR                                                                                                                   | 16 |

| 2.4 | CFO=10 MHz estimation under 8 dB SNR                                                                                                                   | 17 |

| 2.5 | BER performance (uncoded) with and without 10 MHz CFO. $\ . \ . \ .$                                                                                   | 17 |

| 2.6 | Coarse timing detection probability and missed detection<br>probability versus SNRs (CFO = 0). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 18 |

| 2.7 | Coarse timing detection probability and missed detection<br>probability versus SNRs (CFO = $10 \text{ MHz}$ )                                          | 19 |

| 3.1 | Baseband block diagram of a point-to-point wireless communication<br>system with the disclosed successive I/Q imbalance estimation and<br>compensation | 23 |

| 3.2 | Transmitter frame structure                                                                                                                            | 26 |

| 3.3 | Flow graph of Rx I/Q imbalance estimation                                                                                                              | 27 |

| 3.4 | Linear filter structure for Rx I/Q imbalance compensation                                                                                              | 28 |

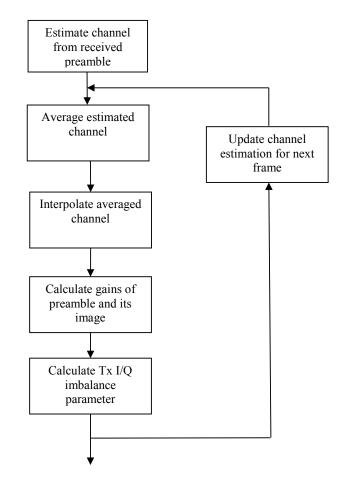

| 3.5 | Flow graph of Tx I/Q imbalance estimation                                                                                                              | 29 |

| 3.6 |                                                                                                                                                        |    |

| 0.0 | Receiver filter bank (upper) and polyphase filter (lower) structures                                                                                   | 31 |

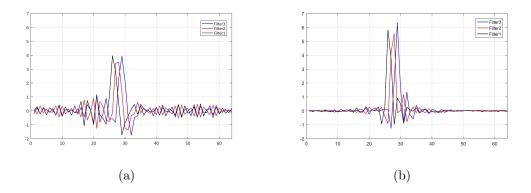

| 3.8  | Real (a) and image (b) parts of estimated and true Tx I/Q $$        |    |

|------|---------------------------------------------------------------------|----|

|      | imbalance coefficients.                                             | 33 |

| 3.9  | Real (a) and image (b) parts of estimated and true coefficients for |    |

|      | Rx I/Q imbalance compensation filter                                | 33 |

| 3.10 | BER performance (uncoded) with and without Tx or Rx I/Q             |    |

|      | imbalance compensation                                              | 34 |

|      |                                                                     |    |

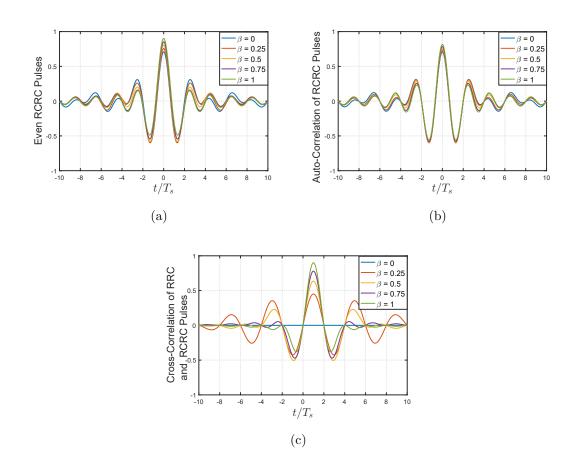

| 4.1  | Waveforms of (a) RCRC pulses, (b) auto-correlation of RCRC          |    |

|      | pulses, and (c) cross-correlation of RRC and RCRC pulses            | 45 |

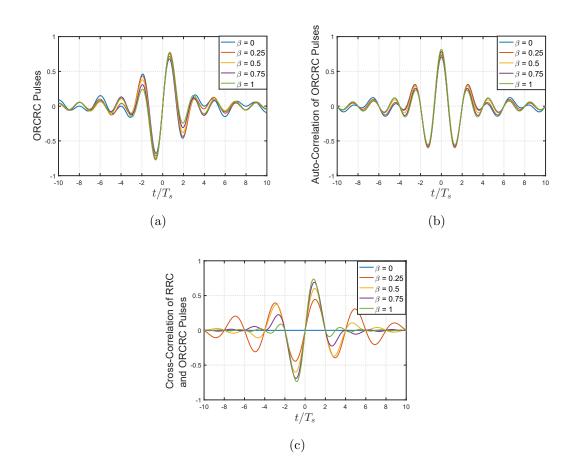

| 4.2  | Waveforms of (a) ORCRC pulses, (b) auto-correlation of ORCRC        |    |

|      | pulses, and (c) cross-correlation of RRC and ORCRC pulses           | 47 |

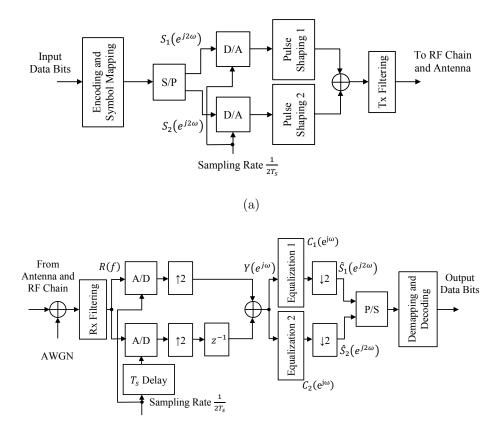

| 4.3  | Dual pulse shaping transmitter (a) and receiver (b)                 | 48 |

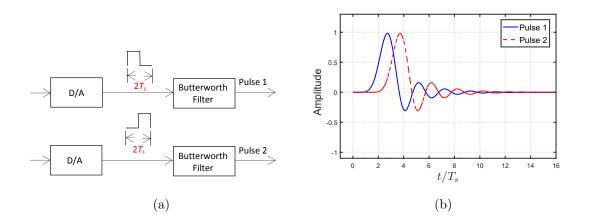

| 4.4  | Dual pulse shaping scheme 1                                         | 57 |

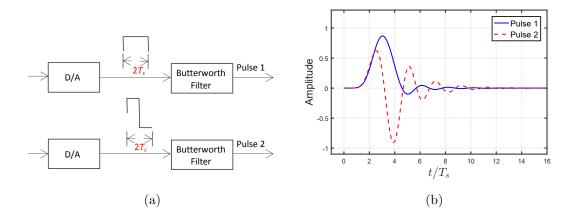

| 4.5  | Dual pulse shaping scheme 2                                         | 58 |

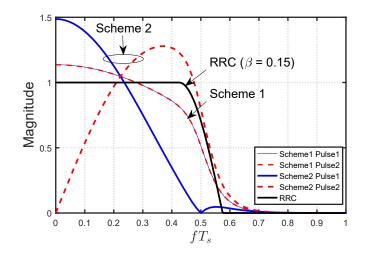

| 4.6  | Dual pulse shaping and RRC spectra                                  | 58 |

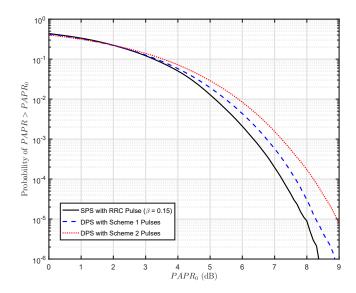

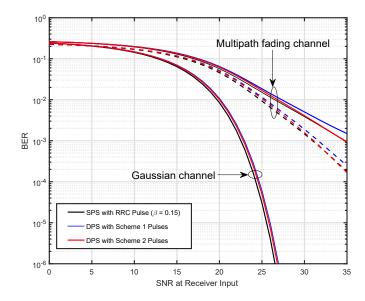

| 4.7  | PAPR comparison.                                                    | 59 |

| 4.8  | BER comparison (solid and dashed lines for ZF and MMSE              |    |

|      | equalization, respectively)                                         | 60 |

|      |                                                                     |    |

| 5.1  | The backhaul system architecture with only half of the proposed 20  |    |

|      | Gbps digital modem.                                                 | 64 |

| 5.2  | The frame structure of the physical layer protocol                  | 65 |

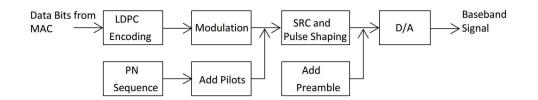

| 5.3  | Transmitter signal processing diagram.                              | 67 |

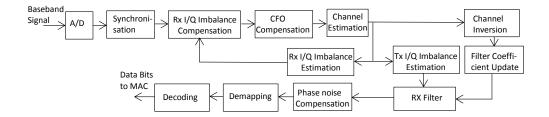

| 5.4  | Receiver signal processing diagram                                  | 68 |

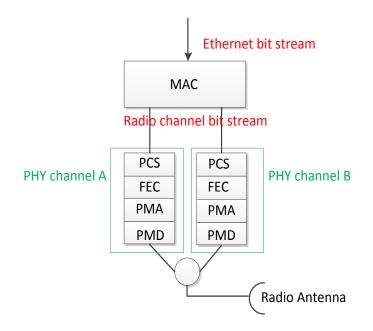

| 5.5  | MAC with two PHY channels                                           | 69 |

| 5.6  | The 66B bridge architecture                                         | 70 |

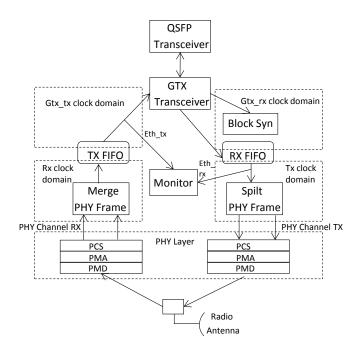

| 5.7  | The Ethernet interface architecture                                       | 71 |

|------|---------------------------------------------------------------------------|----|

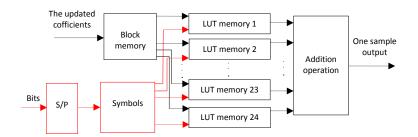

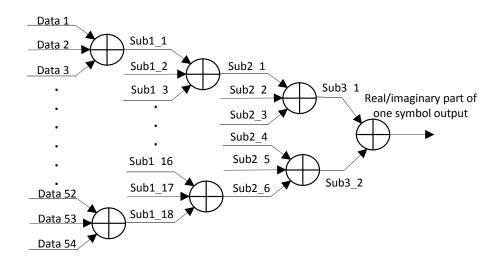

| 5.8  | Structure of Tx filter for one sample                                     | 72 |

| 5.9  | Structure of addition tree for the real/imaginary part of one symbol      | 73 |

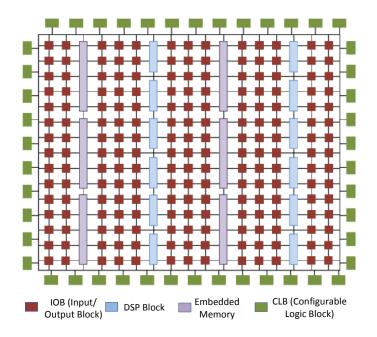

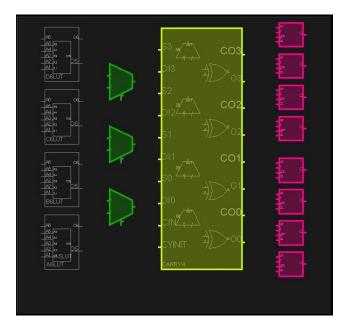

| 5.10 | FPGA structure.                                                           | 75 |

| 5.11 | A slice of Virtex 7 FPGA                                                  | 76 |

| 5.12 | Flexibility feature of FPGA                                               | 78 |

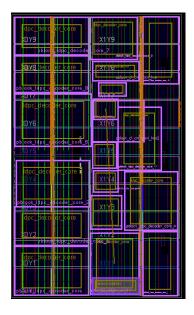

| 5.13 | Essential constraints applied to FPGA device                              | 82 |

| 5.14 | Route result for the whole system                                         | 84 |

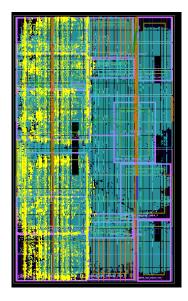

| 5.15 | Frequency tones used to check I/Q imbalance: tones at input to            |    |

|      | $D/A$ (a) and tones at output from A/D (b). $\hdots$                      | 85 |

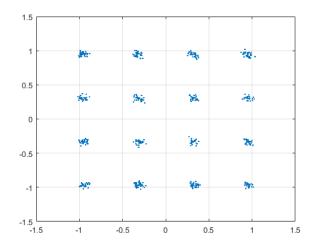

| 5.16 | 16-QAM constellation obtained through external baseband loopback.         | 86 |

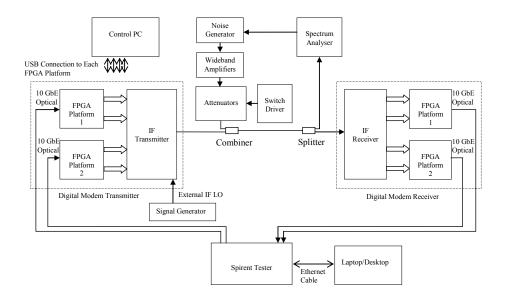

| 5.17 | Structure of test setup                                                   | 86 |

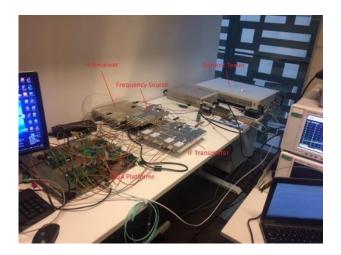

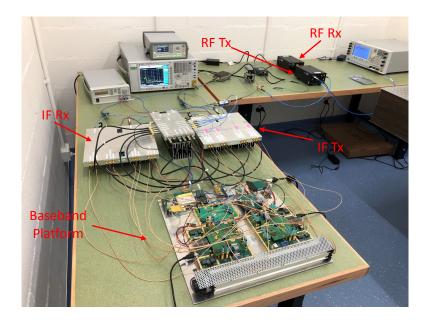

| 5.18 | A picture of 20 Gbps digital modem and test setup                         | 87 |

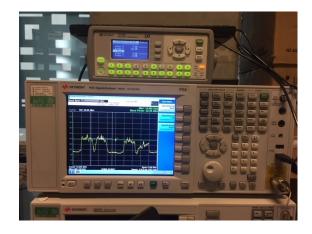

| 5.19 | A picture of IF link with additive noise.                                 | 88 |

| 5.20 | A picture of spectrum analyzer and switch driver                          | 88 |

| 5.21 | Four channels of IF signal                                                | 89 |

| 5.22 | Frequency response of LSB2 (a), LSB1 (b), USB1 (c) and USB2 (d) $$        |    |

|      | channels                                                                  | 90 |

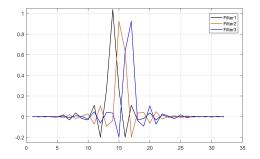

| 5.23 | Tx filters without pre-equalization.                                      | 91 |

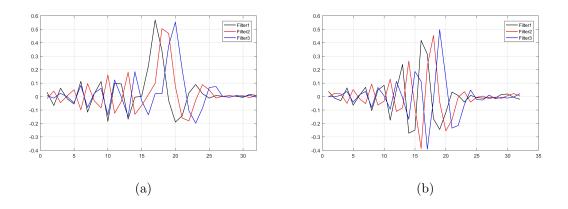

| 5.24 | Tx filters with pre-equalization of (a) real part and (b) imaginary part. | 91 |

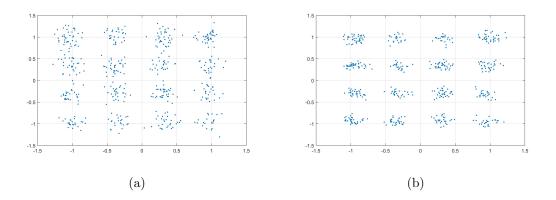

| 5.25 | Real parts of Rx filters (a) without pre-equalization and (b) with        |    |

5.26 Constellations (a) without pre-equalization and (b) with pre-equalization.

5.27 Spirent TestCenter user interface.

95

pre-equalization.

92

| 5.28 | BER test results for individual channels with adjacent channel                                               |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------|--|--|--|

|      | interference                                                                                                 |  |  |  |

| 5.29 | BER test results for all four channels                                                                       |  |  |  |

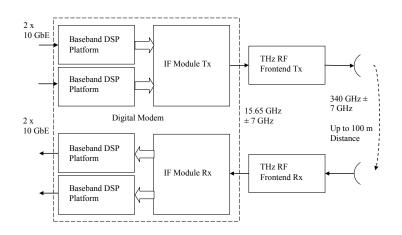

| 5.30 | Block diagram of THz communication system                                                                    |  |  |  |

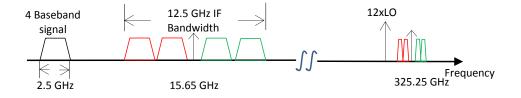

| 5.31 | Frequency conversion from baseband to RF                                                                     |  |  |  |

| 5.32 | THz system and test setup                                                                                    |  |  |  |

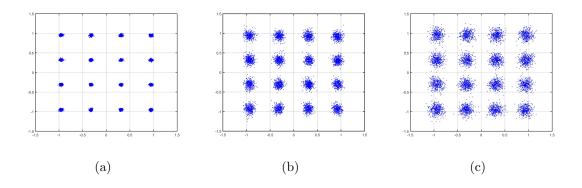

| 5.33 | Measured constellations under various loopback tests: Baseband (a),                                          |  |  |  |

|      | IF (b) and RF (c). $\ldots$ |  |  |  |

### Abbreviation

- 3GPP Third generation partnership project

- A/D Analog-to-digital conversion

- AWGN Additive white Gaussian noise

- ASIC Application specific integrated circuit

- BER Bit error rate

- BRAM Block random-access memory

- CLB Configurable logic block

- CFO Carrier frequency offset

- CP Cyclic prefix

- CSI Cross-symbol interference

- CRC Complementary raised-cosine

- D/A Digital-to-analog conversion

- DFTs Discrete Fourier transforms

- DPS Dual pulse shaping

- DSP Digital signal processing

- EVM Error vector magnitude

- FDM Frequency domain multiplexing

- FEC Forward error coded

- FF Flip-flop

- FFT Fast Fourier transform

- FPGA Field-programmable gate arrays

- FTN Faster-than-Nyquist

- GbE Gigabit Ethernet

- Gbps Gigabit per second

- GEO Geostationary Earth orbit

- Gsps Giga samples per second

- HDL Hardware description language

- HTS High-throughput satellite

IDFT - Inverse discrete Fourier transform

- I/Q In-phase and quadrature-phase

- IP Intellectual property

- IoT Internet of thing

- ISI Inter-symbol interference

- ISTN Integrated space and terrestrial network

- LDPC Low density parity check

- LEO Low Earth orbit

- LO Local oscillator

- LOS Line-of-sight

- LS Least square

- LNA Low noise amplifier

- LSB Lower signal band

- LTE Long term evolution

- LUT Look-up table

- MAC Medium access control

- MEO Medium Earth orbit

- MHz Mega Hertz

- ML Maximum likelihood

- MMSE Minimum mean square error

- mm-wave Millimetre wave

- NRZ Non-return-to-zero

- OFDM Orthogonal frequency-division multiplexing

- ORCRC Odd root complementary raised-cosine

- PAPR Peak-to-average power ratio

- PCS Physical coding sub-layer

- PHY Physical layer

- PMA Physical medium attachment

- PMD Physical medium dependent

- PN Pseudo noise

- QAM Quadrature amplitude modulation

- RAM Random-access memory

- RC Raised-cosine

- RCRC Root complementary raised-cosine

- RF Radio frequency

- ROM Read-only memory

- Rx Receiver

- RRC Root raised-cosine

- RZ Return-to-zero

- SC Single carrier

- SC-FDE Single carrier frequency domain equalization

- SPS Single pulse shaping

- SRC Sampling rate conversion

- SNR Signal to noise ratio

- THz Terahertz

- Tx Transmitter

- UAS Unmanned aircraft system

- UAVs Unmanned aerial vehicle

- USB Upper signal band

### ZF - Zero forcing

## Nomenclature and Notation

Bold capital letters denotes matricess.

- $(.)^H$  denotes matrix conjugate and transpose.

- $tr\left\{ .\right\}$  denotes the trace of a matrix.

- $\left\|.\right\|^2$  stands for the squared Frobenius norm of a matrix.

- $E\{.\}$  denotes expectation.

### Chapter 1

### Introduction

#### 1.1 Background

In the past several decades, the field of telecommunications has witnessed explosive growth in terms of technological advancement, which has a deep impact on many aspects of the human society [1-3]. There are three major types of telecommunication infrastructures: the Internet, mobile wireless systems and satellite systems. Since 1969, the Internet has grown into a global network with worldwide coverage and is the main force that revolutionized the information technologies. For mobile wireless systems, from the first-generation analog systems to the current fourthgeneration and the future fifth-generation systems, mobile wireless communication networks have been through a series of major development involving upgrading and redesigning of system architectures, network protocols and transmission technologies [4]. Since the launch of the first artificial satellite in 1957, the number of satellites orbiting the Earth has been rapidly increasing. One or several of these satellites form an autonomous system [5] to provide some specific services, such as telecommunications, surveillance, remote sensing, positioning, navigation, and so on. Across different satellite systems, however, real-time resource and information sharing is typically very difficult because many satellite systems cannot provide consistent coverage in large areas due to limited illumination [6, 7].

The unmanned aircraft system (UAS) has attracted much attention recently, and various applications such as infrastructure inspection and environmental investigation are being studied [8–10]. However, a unmanned aircraft does not necessarily fly within the radio wave coverage of a terrestrial network. Not only do the data acquired by the aircraft need to be collected, but also controlling an unmanned aerial vehicle is important. Therefore, high-speed wireless communication with a UAS is necessary [11].

With the acceleration of Internet of things (IoTs), smart home and virtual reality, the demand for anywhere and anytime broadband access capability is becoming more and more urgent [12]. At the same time, breakthroughs in machine to machine communications and sensor technology are being made [13]. In response to such communication demands, a satellite communication system called the high-throughput satellite (HTS) has been developed to further enable large-capacity communication [14–16]. The satellite-based Internet of things (S-IoT) with next generation HTS will play a vital role to address issues related to human life such as energy management, climate change, transportation, business logistics and building automation, etc [17, 18]. For HTSs currently in practical use, the allocation of communication resources is fixed, and hence cannot be efficiently performed on-demand among various users. Thus, the next generation HTSs need frequency flexibility so that they can flexibly assign communication resources according to the demands of IoT [18].

As one of the most important mobile satellite communication systems, space networks have attracted significant attention recently. Due to the excellent capabilities, such as high bandwidth, global coverage, and continuous services [19, 20], space networks have been widely used in emergency assistance, navigation, positioning and so on [21, 22]. With the explosion of future satellite services, it will be barely possible to deliver a number of applications and services only by satellite communications. Thus, there is an emerging trend to integrate space networks with terrestrial networks.

Mobile satellite communication is becoming an indispensable component of the

future integrated space and terrestrial network (ISTN) which is able to support the flexibility and seamless coverage for providing broadband and broadcast services in the air, at sea and in remote rural areas [23,24]. The creation of ISTN is of critical importance for industries such as logistics, mining, agriculture, fishery and defense [25]. A high data rate space and terrestrial integrated global information and communications network is the fundamental infrastructure required to support the 21st century industry, economy and society. Currently, there are two parallel major international efforts in the field. The first one is the development of the 5G mobile communications networks that are expected to deliver up to 10 gigabit per second (Gbps) data rates and to be rolled out from 2020 [26]. The second major effort is the development of space communications networks. Based on the early geostationary Earth orbit (GEO) satellites, new space platforms include medium Earth orbit (MEO) and low Earth orbit (LEO) satellites, mini satellites known as CubeSats, and other aerial platforms including stratospheric balloons, airships and aircraft, unmanned aerial vehicles (UAVs), and high-altitude platform stations. In contrast to terrestrial networks, space networks provide communications coverage for people and vehicles. Clearly, the future information network must be one that integrates the space network with the terrestrial network seamlessly [23]. To do so, there are many grand challenges facing industry and the research community. A particularly important challenge is to provide up to hundreds of Gbps data rate wireless links between the space network and the terrestrial network which are referred to as the aerial backbones.

#### 1.2 Challenges for ISTN System

To achieve high-speed aerial backbones for an ISTN, there are some challenges that are needed to be overcome due to the characteristics of satellite communications.

#### • Challenge 1: Large Carrier Frequency Offset (CFO)

In mobile communications, the CFO is mainly caused by mismatch of the local oscillator at the receiving end. Meanwhile, the relative movement between the transmitter and receiver leads to a Doppler spread. An accurate estimation of large CFO is hard to achieve for the line-of-sight (LOS) satellite channel with low received signal to noise ratio (SNR). Hence, high performance synchronization method that operates under large CFO is required to improve the signal detection. The performance degradation resulting from synchronization errors is much more severe in low SNR scenarios. Moreover, by considering the power limitation of a satellite, a low-complexity synchronization under large CFO condition is needed to reduce the energy consumption and implementation cost.

#### • Challenge 2: Power Efficiency

A satellite relies on solar power and, consequently, its energy is limited. As such, a transmitter is better to work near the saturation point of the high power amplifier. A transmitted signal with a large peak-to-average power ratio (PAPR) will seriously reduce the energy efficiency. With increasing demands for wireless services with high data rate, low cost transceivers are attractive for the implementation of wireless communication systems. However, it is quite challenge for such implementation due to the impairments caused by imperfections of the radio frequency (RF) front-end. For instance, orthogonal frequency-division multiplexing (OFDM) suffers from the non-linearity of RF power amplifier because of its high PAPR. On the contrary, single carrier (SC) modulation uses a single carrier, instead of many subcarriers typically used in OFDM, so the peak-to-average transmitted power ratio for SC-modulated signals is smaller. This in turn means that the power amplifier of an SC transmitter requires a smaller linear range to support a given average power. As such, this enables the use of a cheaper power amplifier than a comparable OFDM system; and this is the most significant benefit for mobile satellite wireless communication systems. Hence, SC block transmission has been developed as an alternative technique for broadband wireless systems to mitigate the intersymbol interference (ISI) while achieving higher power efficiency [27] [28]. It is shown that SC transmission with frequency domain equalization has similar performance and signal processing complexity as OFDM, but avoids OFDM's drawback of high PAPR [29]. As a result, SC transmission has been adopted by many wireless standards (e.g., IEEE 802.11ad and IEEE 802.15.3c) to support low power and low complexity wireless transmission. In particular, OFDM for downlink and SC block transmission for uplink of the hybrid approach has been adopted by the Third Generation Partnership Project (3GPP) Long Term Evolution (LTE) standard [30].

#### • Challenge 3: Converter Speed

With the ever increasing demand for high data rate wireless communications, it is necessary to increase the signal bandwidth and improve the spectral efficiency at the same time. For high-speed wideband wireless applications and aerial backbone networks, millimetre wave (mm-wave) communication systems have been proven to be a viable solution since there is more bandwidth to be used for wireless transmission in mm-wave bands such as the E-band (71-76 and 81-86 GHz) with two 5 GHz contiguous bands and the D band (110-170 GHz) with several tens of GHz bandwidth [31] and [32]. A key limitation is the lack of digital-to-analog conversion (D/A) and analog-to-digital conversion (A/D) that operate a high sampling rate such as 10 Giga samples per second (Gsps) or higher sampling rate. For example, Analog Device, Inc. (ADI) recently published the first commercial A/D which can achieve 10 Gsps sampling rate with 12 bits [33]. Texas Instruments Incorporated (TI) and Teledyne e2v have the new production of A/Ds with maximum sampling rate at only 6.4 Gsps at the moment [34] [35]. In order to achieve high-speed mmwave communications with 10 GHz or wider signal bandwidth, higher than 10 Gsps sampling rate D/A and A/D devices must be used. How to adopt lower sampling rate conversion devices to implement more than 10 GHz bandwidth communication system is still a challenge.

#### • Challenge 4: System Complexity

Due to the application requirements for ISTN and the characteristics of the satellite environment, an ISTN system is expected to effectively reduce energy consumption without degradation in performance or increment in cost, while ensuring availability, reliability and robustness. Considering the sampling rate at more than tens of Gsps for each band and/or multiple simultaneously occupied bands, huge number of data should be dealt with in real-time. Future mobile broadband systems are expected to provide users with the experience of radio access with unlimited performance, i.e., instantaneous delivery of large volumes of multimedia content over a highly stable wireless connection. However, due to the characteristics of satellite communications, the limitation in system volume and power is an important issue. Therefore, low-complexity and effective algorithms are necessary to achieve the required system performance and compensate for the imperfection of wireless channels. Moreover, adopting low-complexity and effective algorithms, how to implement them using as less as possible resource in hardware to reduce the power and volume is still a challenge for researchers.

#### **1.3** Thesis Organization

The remainder of this thesis is organized as follows.

Chapter 2 presents a low-complexity synchronization design with large CFO for high-speed wireless communication. It starts with the requirements of synchronization for achieving desired performance with low system overhead. Then, the design of training sequence with desired frequency domain properties to aid the synchronization, channel estimation and in-phase and quadrature-phase (I/Q) imbalance estimation is provided. The practical implementation of autocorrelation with realtime CFO estimation is described to show the effectiveness for peak capture. Finally, simulation results are shown to demonstration the performance.

Chapter 3 presents a method of estimating and compensating for the receiver and transmitter I/Q imbalances sequentially at the receiver digital baseband for pointto-point wireless communication systems. Firstly, the system and signal models are presented for point-to-point wireless communication systems and the format of transmitter frame is described. Then, how to estimate and compensate for I/Q imbalance, how to estimate and equalize channel and how to complete sampling rate conversion (SRC) function are provided and formulated. Finally, the simulation results are shown to demonstration the performance.

Chapter 4 presents a dual pulse shaping (DPS) transmission scheme where the data symbols to be transmitted are split into two half rate data streams. Firstly, the Nyquist theorem for ISI-free transmission is revisited, and the concept of complementary Nyquist pulse is introduced. Then, the cross-symbol interference (CSI) free condition is proved and two classed of complementary Nyquist pulses satisfying this condition are formulated. Next, the DPS system with practical spectral shaping pulses is described and the zero forcing (ZF) and minimum mean square error (MMSE) equalization techniques for DPS are proposed. Finally, the simulation results are provided to show the performance of the proposed system.

Chapter 5 presents a high-speed low-complexity digital modem for wireless com-

munications at 0.325 terahertz (THz) carrier frequency. The basic system requirements, architectures and signal processing modules for transmitter and receiver sides are described. Implementations of some typical modules included Ethernet interface, transmitter filter and receiver filter are presented. Following the description of field programmable gate arrays (FPGA) structure, some key strategies are elaborated when implementing algorithms in FPGA. The implementation and experimental results for digital modem are shown. Finally, the integrations with IF modules and THz RF front-end are described and the experimental results for integrations are provided.

Chapter 6 summarizes the main contributions of this thesis and discusses some research problems for future work.

### Chapter 2

### Synchronization in Presence of Large CFO

#### 2.1 Introduction and Literature Review

The initial frequency offset is quite large in radar, mobile-satellite, global positioning system and satellite navigation applications[36]. In order to take into account an initial frequency offset, continuous wave signals are often applied in conjunction with repeated training sequences [37] [38]. In a typical arrangement, a receiver can first analyze a continuous wave signal to accurately estimate the frequency error and then compensate for the frequency error before proceeding with the subsequent pseudo noise (PN) correlation process. Conventional coarse timing, which fulfills packet detection and locates data symbol to the accuracy within the length of the training sequence, is based on autocorrelation between the received signal and its delayed version. To avoid the adverse impact of power fluctuation, the autocorrelation is usually normalized to the received signal power, and a timing metric with value between zero and one is obtained. The metric is compared to a threshold to determine the coarse timing offset. This conventional scheme has many advantages, such as low-complexity recursive computation, the use of only two repeated sequences, and the capability of fully collecting the multi-path energy. However, auto correlation is vulnerable to large CFO and requires much higher implementation complexity to compensate CFO.

In [37], a robust timing metric is designed for timing offset estimation by using the correlation properties of a periodic preamble. This timing metric has a low computational complexity, but is not sharp and has a large variance. In [39] [40], the authors change the sign of the identical parts of the preamble in [37] to make the timing metric sharper. A timing metric taking advantage of the central symmetry of a preamble is proposed in [38]. In [41], it is shown that applying the periodic parts of more than one preamble can improve the false alarm probability. The application of differential normalization making the values of the timing metric at wrong and correct timing instants more distinct is proposed in [42]. The authors in [43] demonstrate that there are no sufficient statistics for the detection of a preamble that is composed of two identical parts in the time domain, and therefore, the second order statistics used in the previous methods are not sufficient. They also propose fourth order statistics for frame detection. Fourth order differential normalization is used in [44] to improve the synchronization performance. Timing metrics using the cross-correlation of the received signal and pure preamble can be found [45] [46]. In [45], for having a sharper timing metric, the identical parts of the preamble are multiplied by a PN sequence. The authors in [46] improve the timing estimation performance by increasing the correlation length. Although the cross-correlation metrics are sharper than the autocorrelation metrics, they are not as robust as autocorrelation metrics, because they are usually sensitive to CFO, and need to know the exact preamble which may not be easily available or may suffer from considerable implementation complexity when the preamble signal is selected among lots of candidates to identify cell or sector index.

Due to the influence of CFO, it is difficult to achieve a sharp peak from autocorrelation. Therefore, the compensation of CFO is necessary to find the real peak point. However, it is complicated to obtain an accurate value of CFO in time without any delay. Considering these factors, a real-time estimation of CFO which can be used to improve the autocorrelation is necessary.

In a practical wireless communication system, preamble and user data are transmitted separately. Preamble serves as the training signal to facilitate timing and carrier frequency synchronization, channel estimation, and system parameter acquisition [37] [42]. Although a preamble is multi-functional, it is mostly designed for initial timing and frequency synchronization without a priori knowledge of frequencyselective channel impulse response because accurate channel estimation and system parameter acquisition can be achieved effectively only when timing and frequency are well synchronized. To the contrary, for satisfying the throughput requirement of the system, the preamble should not occupy a significant portion in the frame. So, it is essential to design an short enough and effective preamble for achieving these functions.

In this chapter, a low-complexity design of synchronization with large CFO for high-speed wireless communication is proposed. The estimated CFO can be compensated together with autocorrelation operation. And following CFO compensated autocorrelation operation, the accuracy of estimated CFO can be stabilized at the expected value. More importantly, the complexity of implementation is quite low and only a small percentage hardware resource is occupied in real-time FPGA

The rest of this paper is organized as follows. Firstly, one kind of training sequence with desired frequency domain properties to aid the synchronization, channel estimation and transmitter I/Q imbalance estimation is designed. And then the practical implementation of autocorrelation with real-time CFO estimation is described to show the effectiveness for capturing the segment of transmitted preamble. Finally, the simulation results is shown to demonstration the performance.

#### 2.2 Training Sequence Design

Synchronization includes coarse timing (packet acquisition) and fine timing. Coarse timing is only implemented in system power-up to acquire the data frame as following frames will be received continuously. The preamble contains two training sequences. This allows for fine timing in multi-path propagation environment and estimation of large CFO value.

Not only the preferred training sequence described below can complete the function of synchronization, but also the training sequence is specifically designed to achieve the best channel and I/Q imbalance estimation performance with low complexity. The essential properties required for such training sequences are that the real and imaginary parts of the time domain signal are orthogonal and their frequency domain representations also demonstrate some desired characteristics. The training sequence in the discrete time domain at the symbol rate is denoted as

$$x[n] = x_I[n] + jx_Q[n] \tag{2.1}$$

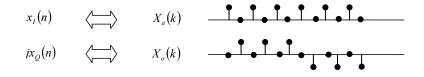

where  $j = \sqrt{-1}$  is the imaginary unit,  $x_I[n]$  and  $x_Q[n]$  are the real and imaginary parts of the training sequence x[n] respectively. The length of the training sequence at symbol rate sampling is  $N_s$ . Let X[k],  $X_e[k]$  and  $X_o[k]$  be the discrete Fourier transforms (DFTs) of x[n],  $x_I[n]$  and  $jx_Q[n]$  respectively where k is also referred to as subcarrier or frequency bin, so that  $X[k] = X_e[k] + X_o[k]$ . For simplicity, we design the sequences  $X_o(k)$  and  $X_e(k)$  to take on values of 1 or -1 only at the even and odd indices respectively and satisfy the required symmetric properties, as illustrated in Figure 2.1. The orthogonality of the real and imaginary parts  $x_I[n]$ and  $x_Q[n]$  may then be denoted as

$$X_{e}[k] X_{o}[k] = 0 (2.2)$$

with  $X_e[k]$  and  $X_o[k]$  not being zeros at the same time. In addition, to reduce the computational complexity, X[k] is preferably real with constant magnitude and satisfy the condition

$$X[k] X[-k] = (-1)^{k}$$

(2.3)

where we have assumed that X[k] is a periodic function of k with period  $N_s$ .

After the training sequence is constructed, the preamble of the transmission frame can be obtained by adding a cyclic prefix (CP) taken from the last part of

Figure 2.1 : Training sequence design.

the samples of x[n]. Preferably, the preamble at symbol rate can be converted to sampling rate after performing pulse shaping and sample rate conversion off-line so that it can be inserted to the transmission frame and directly input to D/A. After the sample rate conversion, the training sequence becomes longer since the sampling rate is normally higher than the symbol rate.

#### 2.3 Autocorrelation Implementation

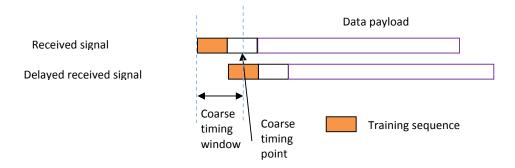

Coarse timing can be implemented with autocorrelation operation, exploiting the similarity between the two training sequences, as shown in Figure 2.2.

Figure 2.2 : Using autocorrelation for coarse timing.

The autocorrelation is represented as

$$\rho(n) = \sum_{k=n-N+1}^{n} y(k)y^*(k-N)$$

(2.4)

where  $y^*$  denotes the conjugate of y. Note that y(k) are received signal samples at 2.5 Gsps. At the same time, the noise energy of N signal samples is computed as

$$\sigma(n) = \sum_{k=n-N+1}^{n} [e^{-jarg[\rho(k)]}y(k) - y(k-N)]^2.$$

(2.5)

The estimated SNR can be calculated as  $SNR(n) = (2|\rho(n)|)/\sigma(n)$  and it is compared with a predefined threshold  $SNR_{th}$ . Once  $SNR(n_t) \ge SNR_{th}$  at  $n = n_t$ , it is assumed that the packet is acquired, and the coarse timing point is at  $n_t$ .

In practical implementation, the autocorrelation operation is implemented for coarse timing, and the accuracy requirement for this part is not very high. So, when implementing the autocorrelation, we can simplify some parts of the equation. The computation of  $\rho(n)$  and  $\sigma(n)$  can be efficiently realized by a sliding window, i.e.,

$$\rho(n+1) = \rho(n) + \phi(n+1)$$

(2.6)

and

$$\sigma(n+1) = \sigma(n) + |y(n+1)|^2 - |y(n+1-2N)|^2 - 2Re\{\phi(n+1)e^{-jarg[\rho(n+1)]}\}$$

(2.7)

where  $\phi(n+1) = y(n+1)y^*(n+1-N) - y(n+1-N)y^*(n+1-2N)].$

Considering eight complex numbers in each system clock (the information of implementation can be found in Section 5.2.3), the eight values of  $arg[\rho(n + 1)]$  in (2.7) can be approximately equivalent. That means, when calculating the value of  $arg[\rho(n + 1)]$  for each system clock, we can merge eight samples together and calculate only one angle. Due to the large number of the resource used for the intellectual property (IP) core of cordic from Xilinx [47], it is effective to save lots of resource in this simplified method. Considering the low level of accuracy in the part of coarse timing and the delay from IP core of cordic, we can simply use the look-up table (LUT) [48] with fixed angle information to replace the cordic core.

From the preamble design, the correct coarse timing will be located during the last half of the second training sequence. Due to the periodic repetition of the training sequences, we can easily find that the value of  $y(n + 1 - N)y^*(n + 1 - 2N)$  is the N-point delayed version of  $y(n + 1)y^*(n + 1 - N)$ . That means, when we calculate the value of  $\phi(n)$ , we can just calculate the front part of  $\phi(n)$ , and then store them into a buffer. After the delay of N points, the stored data can be used as the latter part of  $\phi(n)$ . In this way, half of the number of multipliers for complex numbers are saved in FPGA.

From the above optimized strategies, we can obtain the resource usage of autocorrelation after testing in real system. From Table 2.1, we can see that resource

| Cell   | Slice  | Slice     | Block |             |

|--------|--------|-----------|-------|-------------|

| Name   | LUTs   | Registers | RAMs  | Multipliers |

| Total  | 422000 | 866400    | 1470  | 2600        |

| Number | 433200 | 866400    | 1470  | 3600        |

| Used   | 1774   | 2726      | E     | 34          |

| Number | 1774   | 2720      | 5     | 34          |

| Usage  | 0.4%   | 0.2107    | 2 407 | 1 07        |

| Rate   |        | 0.31%     | 3.4%  | 1%          |

Table 2.1 : FPGA usage of autocorrelation

usage of some typical cells including LUTs, slice registers, block random-access memories (BRAMs), multipliers are reasonable for the autocorrelation compared with the total resources in this device. The module of autocorrelation only occupies a very small proportion of the total available resources. The reserved resources can be used for other modules in the whole digital modem.

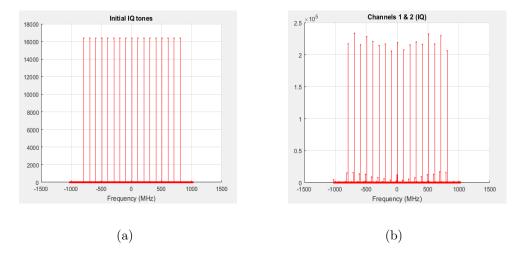

#### 2.4 Simulation Results

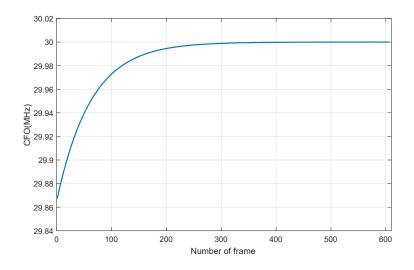

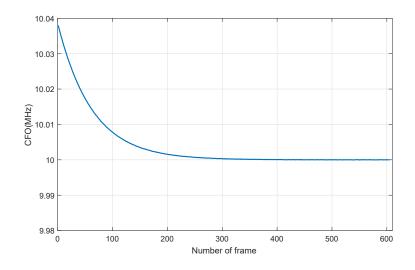

The simulation results are now described as follows. Simulations are carried out by SC signal with 5 GHz and 2.5 GHz bandwidths. The design of training sequence is described in Section 2.2 and the length of training sequence is 64. The autocorrelation is performed during the training period of each frame. That means, the estimated CFO value is updated every frame. Figure 2.3 and Figure 2.4 shows the estimation results with 30 MHz and 10 MHz CFOs under 8 dB SNR in wireless communication systems with 5 GHz and 2.5 GHz bandwidths respectively. After the duration of 300 frames which occupies around 1 ms, the estimated CFOs stabilized at the expected values. Note that the details of frame structure can be found in Section 5.2.3.

Figure 2.3 : CFO=30 MHz estimation under 8 dB SNR.

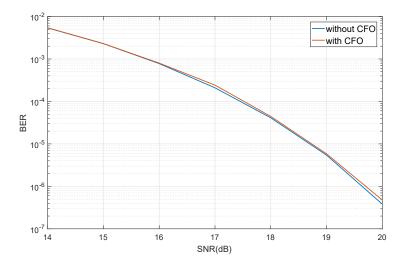

The bit error rate (BER) vs SNR performance (uncoded) is evaluated using a 2.5 GHz bandwidth 16-quadrature amplitude modulation (QAM) modulated wireless communication system with and without CFO. There are 5000 frames and each frame contains 27216 bits. The total number of bits for simulations is 136080000 and the lowest BER would be  $1/136080000 = 7.35 \times 10^{-9}$ . The results are presented

Figure 2.4 : CFO=10 MHz estimation under 8 dB SNR.

in Figure 2.5. It shows that the wideband wireless communication system with CFO estimation and compensation can achieve almost the same performance comparing with the system without CFO. The simulation results indicate that the estimation accuracy is sufficient for supporting 16-QAM without performance loss.

Figure 2.5 : BER performance (uncoded) with and without 10 MHz CFO.

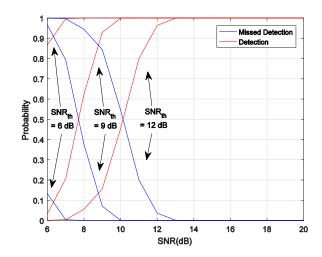

To demonstrate the performance of the above described coarse timing algorithm, simulation results in terms of detection probability and missed detection probability under various SNRs and carrier frequency offsets are provided in Figure 2.6 and Figure 2.7 respectively. Practical transmitter and receiver I/Q imbalances (with image rejection ratio of about 23 dB) are also added in the simulations.

Figure 2.6 : Coarse timing detection probability and missed detection probability versus SNRs (CFO = 0).

#### 2.5 Conclusions

An effective design and implementation of synchronization with large CFO for high-speed wireless communication is proposed and tested. The CFO can be estimated and compensated together with autocorrelation operation. The optimized algorithms are implemented with low-complexity, and the low resource usage is verified in real-time FPGA. From the simulation results, autocorrelation operation can capture tens of MHz CFO and the system has almost no performance loss comparing with the system without CFO.

Figure 2.7 : Coarse timing detection probability and missed detection probability versus SNRs (CFO = 10 MHz).

#### Chapter 3

# Joint I/Q Imbalance Compensation and Channel Equalization in SRC Receiver Filters

#### 3.1 Introduction and Literature Review

Many applications require that the I/Q imbalances for both transmitter (Tx) and receiver (Rx) can be estimated and compensated separately. I/Q imbalance is one major issue that needs to be considered in low cost architectures, such as direct conversion transmitter [49]. I/Q imbalance may accrue during up-convertor at the transmitter and down-convertor at the receiver because of the mismatch of the two branches. The distortion introduced by I/Q imbalance can be frequencyindependent (caused by the amplitude and phase difference in the non-ideal mixer) or frequency-dependent (caused by inaccuracy of the branch filters). Without proper compensation techniques, the transmission capability of wireless system under I/Q imbalance will be seriously degraded.

In general, it is very hard to compensate I/Q imbalance in analog domain due to its cost and inefficiency [50]. As mentioned in [51], many related works have focused on mitigating the effect of I/Q imbalance in digital baseband. For OFDM systems, the impact of I/Q imbalance is studied [52]. Furthermore, a closed-form BER analysis of OFDM system under I/Q imbalance is derived in [53]. These results show that the effect of I/Q imbalance produces so called mirror carrier interference causing the loss of orthogonality among the subcarriers. Various I/Q imbalance estimation and compensation schemes have been proposed for the compensation of frequency-independent [54] and frequency-dependent I/Q imbalance [50]. Initially, most solutions use linear compensation methods, such as least square (LS) [55] and MMSE [56]. Later, nonlinear receivers like decision-directed [57], expectation methods maximization [58] and maximum likelihood (ML) [59] methods are introduced for better performance.

There are not many works on I/Q imbalance for single carrier frequency. Under frequency-independent I/Q imbalance, the training sequence design for LS channel estimation of single carrier frequency domain equalization (SC-FDE) is studied in [60]. Then an enhanced channel estimation is proposed using alternative LS (ALS) algorithm [61]. Furthermore, [62] derives the channel model of SC-FDE with independent Tx/Rx frequency I/Q imbalance, PN sequence aided channel estimation and MMSE compensation. Considering the presence of both I/Q imbalance and carrier frequency offset, a three stage compensation scheme for SC-FDE is provided in [63]. For millimeter-wave SC-FDE systems, Cheng et al. [64] propose joint channel and I/Q imbalance estimation using ML criterion and I/Q imbalance compensation using MMSE criterion. However, most existing works focus on the channel estimation under frequency-independent I/Q imbalance and use linear compensation methods to eliminate the effect of I/Q imbalance. Although linear receivers benefit from their low complexity, the BER performance is far from the match filter bound (MFB), especially in highly frequency-selective wireless channel [65]. There exist several nonlinear receivers for SC-FDE system without I/Q imbalance. Among them, one promising design is the iterative block decision feedback equalization [66], which employs feedforward and feedback filters in frequency domain and its performance is close to the MFB. Its iterative architecture has been extended to several special scenarios, such as interference channels [65] and system with imperfect channel state information [67]. Most of the conventional techniques deal with I/Q imbalance at the receiver side only [68, 69], whereas both Tx and Rx side imbalances exist at the same time in practical systems. Estimating and compensating for both Tx and Rx side imbalances are very challenging as the imbalanced signals are mixed together and the received signals only reflect the overall effect resulted from both Tx and Rx imbalances. When CFO is present in the communication system [70,71], the overall effect also changes over time. Existing approaches typically require off-line calibration to estimate and compensate for the Tx I/Q imbalance, and then estimate and compensate for the Rx I/Q imbalance using the received signal [72]. Real-time calibration is also possible to deal with time-varying Tx I/Q imbalance [73], however, this calibration will interrupt the data transmission and/or require more system overhead. A feedback channel is also necessary if the imbalance is estimated at the receiver side [74].

To achieve better equalization performance, a wireless SC system commonly uses fractionally spaced linear equalizer, which requires that the sampling rate is higher than the data symbol rate. Therefore, SRC is necessary to convert symbol rate to sampling rate before pulse shaping at the transmitter and sampling rate to symbol rate after equalization at the receiver, which generally increases the digital signal processing complexity. If the SRC can be performed jointly with other functions such as I/Q imbalance compensation and equalization, the complexity will be reduced.

I/Q compensation, channel equalization and SRC play vital roles in high-speed wireless communication systems. Any lack of such signal processing will significantly impact on the performance of the whole system. The bandwidth of our proposed system involves four channels each having 2.5 GHz spectrum. In such wide bandwidth, any imperfection in various filters of IF and/or RF as well as wireless multi-path fading channel introduces ISI at the receiver. In the meantime, existing algorithms for such signal processing are complicated and require lots of hardware resource to implement, especially for high-speed wideband wireless communication.

In this chapter, a low-complexity and an effective method for estimating Rx and

Tx I/Q imbalances and compensating for them in serial at the receiver of a communication system is proposed. The system and signal models for point-to-point wireless communication systems are first presented and the format of the transmitter frame is described. Then, how to estimate and compensate I/Q imbalance, how to estimate and equalize channel and how to complete SRC function are provided and formulated. Finally, the simulation results are shown to demonstrate the performance.

#### Input Data Bits X(f)Encoding and Pulse Shaping and Y(f)Modulation Sample Rate Conversion D/A Upconversion (b) (a) Training (c) (d) Sequence Channel (e) $e^{j2\pi\Delta ft}$ (h) (k) (m) (g) (f) (j) Rx I/Q CFO Down-Polyphase Decoding and A/D R(f)Imbalance conversion Demodulation Compensation Filters Compensation Z(f)Output Data Bits Channel and Tx CFO and Rx I/Q Imbalance I/Q Imbalance Estimation Estimation (1)(i)

#### **3.2** System and Signal Models

Figure 3.1: Baseband block diagram of a point-to-point wireless communication system with the disclosed successive I/Q imbalance estimation and compensation.

Figure 3.1 shows a baseband schematic block diagram of point-to-point wireless communication system. The system includes a transmitter which communicates via a channel with a receiver. CFO will be introduced at the receiver, which can be modelled as the multiplication of the received baseband signal by a phase rotation  $e^{j2\pi\Delta ft}$  where  $\Delta f$  is the CFO.

At the transmitter of Figure 3.1, the input data bits are forward error coded (FEC) and modulated by module (a). The resulting data symbols are then input to the pulse shaping and sample rate conversion module (b) to generate output symbols. The output symbols are next provided to a D/A before the signal is up-converted by the up-converter (d) and transmitted over the channel (e). The up-converter will introduce Tx I/Q imbalance. During a training period which starts at the beginning of every transmitter frame, a training sequence is inserted before the data payload. Preferably, the rate of training sequence is equal to data symbol rate and then converted to sampling rate so that it can be directly input to the D/A.

Mathematically, the frequency domain signal model of the transmitted signal can be expressed as

$$Y(f) = U_t(f) X(f) + V_t(f) X^*(-f)$$

(3.1)

where X(f) and Y(f) are the transmitted signals before and after up-conversion respectively,  $U_t(f)$  and  $V_t(f)$  are the frequency dependent gains of the baseband signal and its image respectively.  $U_t(f)$  can be regarded as part of the transmission channel frequency response whereas  $V_t(f)$  reflects the interference caused by the Tx I/Q imbalance.

At the receiver of Figure 3.1, the signal received from the channel (e) and distorted by the CFO is first down-converted by the down-converter (f) and passed to an A/D (e). The down-converter will introduce  $\operatorname{Rx} I/Q$  imbalance. After the CFO and  $\operatorname{Rx} I/Q$  imbalance are estimated in the module (i), they are compensated in the modules (h) and (j) sequentially. Channel and  $\operatorname{Tx} I/Q$  imbalance estimations are performed in the module (l) and the estimated channel and I/Q imbalance parameters are used to calculate the polyphase filter coefficients. The polyphase filters perform combined Tx I/Q imbalance compensation, channel equalization, and sample rate conversion to generate output symbols. The output symbols are then provided to module (m) which applies FEC decoding and demodulation to provide output data bits.

Mathematically, the received signal before down-conversion R(f) can be expressed as

$$R(f) = e^{j\varphi}Y(f - \Delta f)H(f - \Delta f)$$

(3.2)

where  $\varphi = 2\pi\Delta f t_0$  is a phase rotation caused by the CFO at the beginning of a transmission frame at time instant  $t_0$  and H(f) is the channel frequency response. After down-conversion, the received signal is

$$Z(f) = U_r(f) R(f) + V_r(f) R^*(-f)$$

(3.3)

where  $U_r(f)$  and  $V_r(f)$  are the frequency dependent gains of the received signal and its image respectively.  $U_r(f)$  can be regarded as part of the transmission channel frequency response whereas  $V_r(f)$  reflects the interference caused by the Rx I/Q imbalance.

#### 3.3 I/Q Imbalance Compensation and Channel Equalization

In order for the receiver to estimate CFO, Rx and TX I/Q imbalances, and channel frequency response, a training sequence needs to be periodically transmitted. Hence, a transmitter frame structure is proposed as shown in Figure 3.2. It consists of a preamble and a data payload. The preamble of each data frame includes the training sequence and its CP. Because all the I/Q imbalance and channel estimation is performed in the frequency domain, the CP is used to convert the linear convolution of transmitted single with the channel to a circular convolution so that fast Fourier transform (FFT) can be applied to convert a signal from time domain to frequency domain.

Figure 3.2 : Transmitter frame structure.

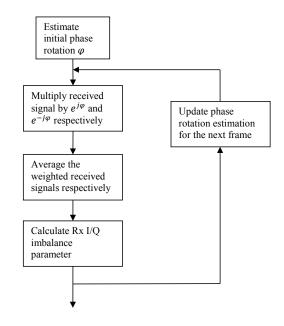

Once the training sequence is received at the receiver digital baseband after signal synchronization, Rx I/Q imbalance is estimated as follows.

Firstly, at the beginning of each received frame, the phase rotation is estimated. Then, the received signal Z(f) is weighted by the phase factors  $e^{j\varphi}$  and  $e^{-j\varphi}$  respectively to have

$$e^{j\varphi}Z(f) = e^{j2\varphi}U_r(f)Y(f - \Delta f)H(f - \Delta f) + V_r(f)Y^*(-f - \Delta f)H^*(-f - \Delta f)$$

(3.4)

and

$$e^{-j\varphi}Z(f) = U_r(f)Y(f - \Delta f)H(f - \Delta f) + e^{-j2\varphi}V_r(f)Y^*(-f - \Delta f)H^*(-f - \Delta f)$$

(3.5)

Performing the same operations as described by (3.4) and (3.5) for a number of received frames and averaging over the differently weighted received signals, we have

$$E\left\{e^{j\varphi}Z\left(f\right)\right\} = V_r\left(f\right)Y^*\left(-f - \Delta f\right)H^*\left(-f - \Delta f\right)$$

(3.6)

and

$$E\left\{e^{-j\varphi}Z\left(f\right)\right\} = U_{r}\left(f\right)Y\left(f - \Delta f\right)H\left(f - \Delta f\right)$$

$$(3.7)$$

where  $E\{.\}$  denotes expectation.

The Rx I/Q imbalance parameter is then estimated as

$$\beta_r(f) = \frac{E\{e^{j\varphi}Z(f)\}}{E\{e^{-j\varphi}Z^*(-f)\}} = \frac{V_r(f)}{U_r^*(-f)}.$$

(3.8)

A flowchart describing the above Rx I/Q imbalance estimation process is shown in Figure 3.3.

Figure 3.3: Flow graph of Rx I/Q imbalance estimation.

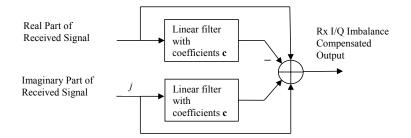

The estimated Rx I/Q imbalance parameter  $\beta_r(f)$  can be used to compensate for the Rx I/Q imbalance by the operation  $Z(f) - \beta_r(f)Z^*(-f)$  in the frequency domain. However, in practice, a linear filter in the time domain is preferable. The structure of such a linear filter is shown in Figure 3.4, where the filter coefficients are represented by a vector c which is the inverse discrete Fourier transform (IDFT) of the discrete version of the frequency domain Rx I/Q imbalance parameter  $\beta_r(f)$ .

After Rx I/Q imbalance and CFO compensation, the Tx I/Q imbalance can be further estimated and compensated from the received signal during the preamble period, which is modeled in the discrete frequency domain as

$$R[k] = U_t[k] H_1[k] X[k] + V_t[k] H_1[k] X^*[-k]$$

(3.9)

Figure 3.4 : Linear filter structure for Rx I/Q imbalance compensation.

where X[k] is the designed frequency domain training signal as described previously and  $H_1[k]$  is the equivalent channel frequency response after Rx I/Q imbalance compensation. Note that the length of R[k] is N.

The Tx I/Q imbalance estimation makes use of the properties of X[k], i.e., X[k] is real, binary, and satisfies the condition shown in (2.3). In fact, multiplying both sides of (3.9) by X[k] for  $k = 0, \dots, N/2$  and by  $X[k-N+N_s]$  for  $k = N/2+1, \dots, N-1$ , we have

$$\tilde{H}[k] = \begin{cases} R[k] X[k], \ k = 0, \cdots, \frac{N}{2} \\ R[k] X[k - N + N_s], \ k = \frac{N}{2} + 1, \cdots, N - 1 \end{cases}$$

(3.10)

$$= U_t[k] H_1[k] + (-1)^k V_t[k] H_1[k].$$

$\tilde{H}[k]$  can be interpreted as the estimated channel before Tx I/Q imbalance compensation. From  $\tilde{H}[k]$ , the Tx I/Q imbalance can be estimated as follows:

# **Step 1**. Compute instantaneous channel estimation $\widetilde{H}(k)$ from the received preamble;

**Step 2**. For every frequency bin in  $\widetilde{H}(k)$ , get an interpolated value using two adjacent bins on both sides to obtain  $\widetilde{H}'(k)$ ;

Step 3. Calculate  $U(k) = \frac{\tilde{H}(k) + \tilde{H}'(k)}{2}$  and  $V(k) = (-1)^k \left[\frac{\tilde{H}(k) - \tilde{H}'(k)}{2}\right];$ Step 4. Calculate  $H_{V/U^*}(k) = \frac{V[k]}{U^*[-k]}.$

In practice, channel estimation will average over multiple frames to improve the SNR. Therefore, no further averaging on  $H_{V/U^*}(k)$  is necessary. This can simplify the algorithm without performance loss. The flowchart describing the above Tx I/Q imbalance estimation process is shown in Figure 3.5.

Figure 3.5 : Flow graph of Tx I/Q imbalance estimation.

After estimating the I/Q imbalance, the I/Q imbalance parameter can be com-

bined to the channel estimation. The channel estimation can be defined as

$$H_{U^*}(k) = \widetilde{H}(k) - (-1)^k H_{V/U^*}(k) \widetilde{H}^*((N-k)_N).$$

(3.11)

Once the channel is estimated in the frequency domain, the inverse channel estimation can be calculated as

$$C(k) = \begin{cases} \frac{H_{U^*}(k)}{|H_{U^*}(k)|^2 + |H_{U^*}(k+N-N_s)|^2} & k = N_s - \frac{N_b}{2}, \cdots, \frac{N_b}{2} \\ \frac{1}{H_{U^*}(k)} & (k = 0, \cdots, N_s - \frac{N_b}{2} - 1) and \\ (k = N - N_s + \frac{N_b}{2} + 1, \cdots, N - 1) \\ \frac{H_{U^*}(k)}{|H_{U^*}(k)|^2 + |H_{U^*}(k-N-N_s)|^2} & k = N - \frac{N_b}{2}, \cdots, N - N_s + \frac{N_b}{2}, \end{cases}$$

(3.12)

where  $N_s$  denotes the training sequence length at symbol rate and  $N_b$  denotes the number of frequency points in established bandwidth.

The receiver filters perform all the I/Q imbalance compensation, channel equalization, and SRC functions at the same time. We can combine the coefficients of channel equalization and I/Q imbalance compensation together to simplify the process. For the real and imaginary of symbols, the base filter's frequency responses are calculated respectively as

$$A(k) = [1 - H_{V/U^*}(k)]C(k)$$

(3.13)

and

$$B(k) = [1 + H_{V/U^*}(k)]C(k).$$

(3.14)

After performing phase shift in frequency domain, we obtain

$$A_{p}(k) = \begin{cases} A(k)exp(j\frac{2\pi}{N_{s}}kp) & k = 0, 1, \cdots, \frac{N}{2} - 1\\ A(k)exp(j\frac{2\pi}{N_{s}}(k-N)p) & k = \frac{N}{2}, \frac{N}{2} + 1, \cdots, N - 1 \end{cases}$$

(3.15)

and

$$B_p(k) = \begin{cases} B(k)exp(j\frac{2\pi}{N_s}kp) & k = 0, 1, \cdots, \frac{N}{2} - 1\\ B(k)exp(j\frac{2\pi}{N_s}(k-N)p) & k = \frac{N}{2}, \frac{N}{2} + 1, \cdots, N - 1. \end{cases}$$

(3.16)

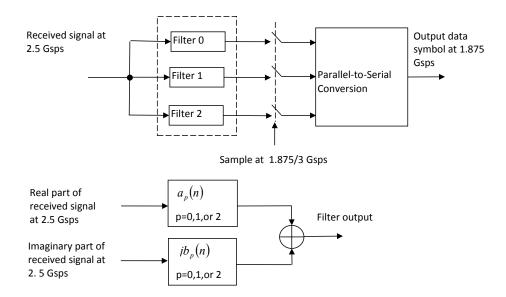

After converting  $A_p(k)$  and  $B_p(k)$  to the time domain by applying N-point IDFT, the coefficients of the receiver filters for filtering the real and imaginary parts of the received signal respectively can be obtained. The block diagram of the receiver filter bank and the structure of each polyphase filter are shown in Figure 3.6.

Figure 3.6 : Receiver filter bank (upper) and polyphase filter (lower) structures.

#### 3.4 Simulation Results

To demonstrate the performance of the proposed method for high-speed low-cost communications, the simulation results are presented by SC signal with a 2.5 GHz wideband wireless communication system. The CFO is selected as  $\Delta f = 10$  MHz and 16-QAM is used.

I/Q imbalance parameters are selected as follows. For the transmitter, the phase imbalance is -10 degree and the amplitude imbalance is 2 dB. To simulate the fre-

quency dependency, the two-order Butterworth filter with cutoff  $2\pi \times 0.3735$  radians is applied to the I channel and the three-order Butterworth filter with cutoff  $2\pi \times 0.3708$  radians is applied to the Q channel. For the receiver, the phase imbalance is 10 degree and the amplitude imbalance is -3 dB. The two-order Butterworth filter with cutoff  $2\pi \times 0.3871$  radians is applied to the I channel and the three-order Butterworth filter with cutoff  $2\pi \times 0.3826$  radians is applied to the Q channel.

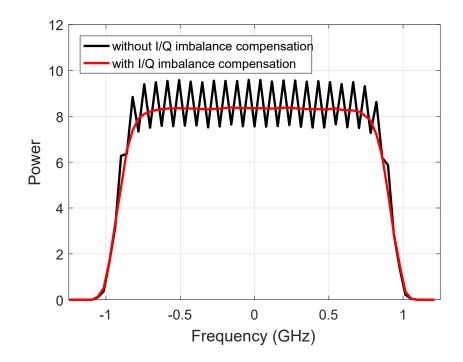

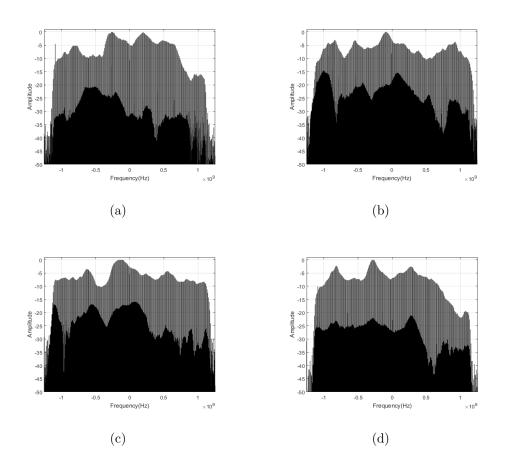

Figure 3.7 shows a simulated channel frequency response in which the I/Q imbalance is clearly seen (the saw tooth in black curve). After I/Q imbalance compensation, the refined channel frequency response is smoother (the red curve).

Figure 3.7: Estimated channel frequency response and refined channel after I/Q imbalance compensation.

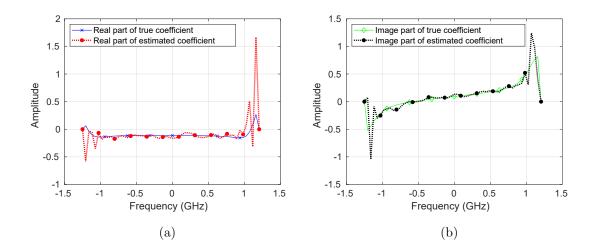

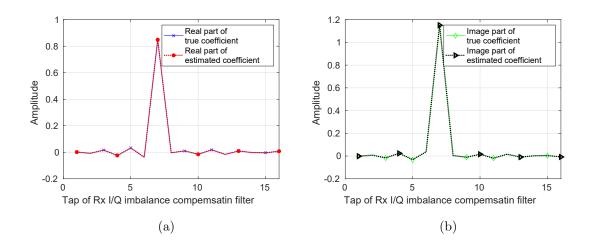

Figure 3.8 shows the real and image parts of estimated and true coefficients for Tx I/Q imbalance compensation. The estimated coefficients in the passband are quite close to the true values except for the coefficients at the edges of the bandwidth.

Figure 3.9 shows the real and image parts of estimated and true coefficients of the Rx I/Q imbalance compensation filter and the estimated coefficients are quite close to the true values.

Figure 3.8 : Real (a) and image (b) parts of estimated and true Tx I/Q imbalance coefficients.

Figure 3.9 : Real (a) and image (b) parts of estimated and true coefficients for Rx I/Q imbalance compensation filter.

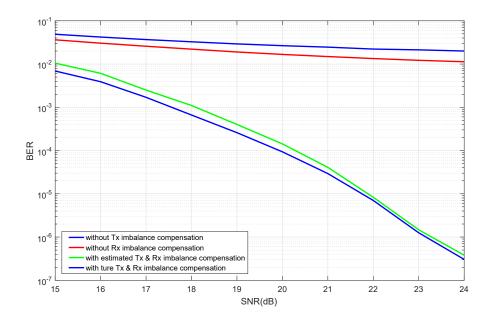

Finally, the BER performance (uncoded) is evaluated with and without Tx

or/and Rx I/Q imbalance compensation, and the results are presented in Figure 3.10. The BER curve with perfect I/Q imbalance compensation (i.e., assuming perfect knowledge of the I/Q imbalances) is also shown. It is obvious that the performance is poor without any of Tx or Rx imbalance compensation. The BER curve with I/Q imbalance compensation using the estimated I/Q imbalance parameters is very close to the one using true I/Q imbalance compensation, which indicates that the estimation accuracy is sufficient for supporting 16-QAM with negligible performance loss.

Figure 3.10 : BER performance (uncoded) with and without Tx or Rx I/Q imbalance compensation.

#### 3.5 Conclusions

We have proposed a method of estimating and compensating for the receiver and transmitter I/Q imbalances in sequential at receiver digital baseband for pointto-point wireless communication systems. The Rx I/Q imbalance is estimated by the received signal's statistical property and is compensated with a time domain linear filter. Using the received training sequence after  $\operatorname{Rx} I/Q$  imbalance and CFO compensation, the channel and  $\operatorname{Tx} I/Q$  imbalance are estimated and the compensation for the  $\operatorname{Tx} I/Q$  imbalance and channel as well as samples rate conversion are jointly performed with a time domain linear filter. From the simulation results, the estimated  $\operatorname{Rx}$  and  $\operatorname{Tx}$  imbalance coefficients are quite close to the true values and the joint algorithm can achieve the desired performance.

### Chapter 4

## Dual Pulse Shaping Transmission System and Method

#### 4.1 Introduction and Literature Review

In conventional digital single carrier communication systems, Nyquist pulse shaping at the transmitter and matched filtering at the receiver are used to achieve ISI free transmission and maximize the received SNR [75]. As one class of Nyquist pulses, raised-cosine (RC) pulses are widely used for such single pulse shaping transmission. Here, a root raised-cosine (RRC) pulse is used as the spectral shaping pulse at the transmitter and the same RRC pulse is used as the matched-filter impulse response. A roll-off factor associated with the RC pulse determines the actual transmitted signal bandwidth, which is often wider than the data symbol rate, resulting in reduced spectral efficiency.

With the ever growing demands for high data-rate wireless communications, it is necessary to increase the signal bandwidth and improve the spectral efficiency at the same time [76]. For high-speed wireless applications and aerial backbone networks, mm-wave technology has been proven to be a viable solution due to the availability of large bandwidth, e.g., 10 GHz in the E-band (71-76 and 81-86 GHz) and several tens of GHz in the D band (110-170 GHz). In order to achieve high-speed mmwave communications with 10 GHz or wider signal bandwidth, higher than 10 Gsps sampling rate D/A and A/D devices generally need to be used.

When the required high-speed data conversion devices are unattainable or costly, how to achieve high date-rate wireless communications at low cost becomes a significant challenge. There are existing techniques such as time-interleaved [77] and frequency channelized [78–80] data converters. However, for time-interleaved schemes, the resolution (the number of bits for samples) and speed can not be achieved at the same time. For frequency channelized schemes, the sample/hold circuitry is very difficult to design as it sees the uppermost frequency in the high-frequency subband channels. In addition, the sharp bandpass filters that are needed to achieve high spectrum efficiency are also difficult to realize, especially in integrated chips [81,82]. Faster-than-Nyquist (FTN) signaling [83,84] has recently attracted great attention for achieving higher spectral efficiency. However, highly complicated signal processing at receiver is needed to deal with the interference between symbols [79,80]. Such high complexity can make it unsuitable for many real-time signal processing platforms. Moreover, the PAPR of FTN signals is generally large, which limits the average transmission power.

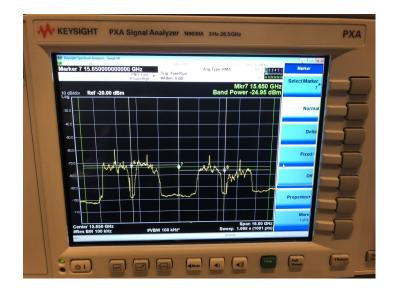

Systems with reduced sampling rate may also be realized by allowing non-ideal transmission. Non-ideal transmission channels introduce ISI at the receiver and degrade system performance, and the severity of ISI increases with the reduction of sampling rate. ISI can typically be mitigated by ZF equalization [85, 86], MMSE equalization [87, 88] that can solve the noise enhancement problem of ZF, and fractionally spaced equalization (FSE) [89, 90]. However, all these equalization techniques require signal inputs sampled at a minimum of symbol rate. Hence the reduction of sampling rate via non-ideal transmission is very limited.