"© 2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works."

# DC-Link Voltage Balancing Strategy Based on Optimal Switching Sequences Model Predictive Control for Single-Phase H-NPC Converters

Sergio Vazquez, Senior Member, IEEE, Pablo Acuna, Member, IEEE, Ricardo P. Aguilera, Member, IEEE, Jose Pou, Fellow Member, IEEE, Jose I. Leon, Fellow Member, IEEE, and Leopoldo G. Franquelo, Fellow Member, IEEE

Abstract—In this paper, a model predictive control (MPC) strategy based on the optimal switching sequence (OSS) concept for a single-phase grid-connected H-bridge neutral-point-clamped (HNPC) power converter is presented. The proposed OSS-MPC algorithm considers both the grid current tracking error and the dc-link capacitor voltage balance. Special emphasis is placed on the power converter control region in order to design suitable switching sequence candidates for this multi-objective control problem. Additionally, based on an analysis of the weighting factor effect over closed-loop performance, it is possible to demonstrate that this controller parameter is relatively easy to adjust. In fact, the weighting factor only affects the peak current during transients, with no effect over the steady-state performance. As a result, the proposed OSS-MPC provides a fast closed-loop dynamic to the H-NPC converter, which operates with a fixed switching frequency at all times. This predictive control strategy is experimentally validated in a 3.5 kVA laboratory setup.

#### I. Introduction

OWER converters are key components for the penetration of technologies such as renewable energy, energy storage, etc [1], [2]. Among these applications, low-power renewable energy generation, like rooftop photovoltaic (PV), and high-power railway traction systems use single-phase power converters as grid and catenary interface [3]–[5]. One interesting topology for these applications is the single-phase H-bridge neutral-point-clamped (H-NPC) converter. Compared to the

The authors gratefully acknowledge the financial support provided by the Spanish Science and Innovation Ministry under project TEC2016-78430-R. This work was also supported by the Chilean Government under Project CONICYT/FONDECYT 1191520.

S. Vazquez, J.I. Leon and L.G. Franquelo are with the Electronics Department, Universidad de Sevilla, Sevilla, C.P. 41092 Spain(e-mail: sergi@us.es, jileon@us.es, Igfranquelo@us.es). J.I. Leon and L.G. Franquelo are also with the School of Astronautics, Harbin Institute of Technology, Harbin 150001, P. R. China (e-mail: jileon@hit.edu.cn, Igfranquelo@hit.edu.cn).

P. Acuna is with the Department of Electrical Engineering, Universidad de Talca, Chile. (e-mail: pablo.acuna@ieee.org).

R. P. Aguilera is with the School of Electrical and Data Engineering, at the University of Technology Sydney, Broadway, NSW 2007, Australia. (email:raguilera@ieee.org).

J. Pou is with the School of Electrical and Electronic Engineering, Nanyang Technology University, 639798 Singapore (e-mail: josep.pou@ieee.org).

conventional H-Bridge converter, an H-NPC can generate up to five output voltage levels and presents high efficiency and compact design as main features.

The research community has paid special attention to develop advantageous control strategies for single-phase gridconnected power converters, including nonlinear control solutions [6], [7]. Among them, model predictive control (MPC) has emerged as an interesting alternative for power converters. This control strategy can manage multiple control targets while including system constraints in the optimal control formulation [8], [9]. In essence, an MPC strategy uses a system model to predict the future behavior of the system outputs up to a finite prediction horizon based on their present values. Then, the predicted system output behavior is evaluated in a cost function to quantify its predicted closed-loop performance. Afterwards, an optimization algorithm is used to solve the resulting optimal control problem defined by the cost function and system constraints. The solution to this optimal control problem results in the control action to be applied to the system. This process is repeated at each sampling instant using a receding horizon policy [10].

On the other hand, one of the most popular MPC control strategies for power converters is the, so-called, finite control set MPC (FCS-MPC). This control methodology considers a finite number of possible control inputs to handle the optimal control problem, e.g., the power converter output voltage vectors. The main advantage is that the optimal control problem can be easily solved, even for multi-objective optimization problems that include system constraints, by evaluating all the possible control inputs in a cost function. Despite this advantage, the main drawback of FCS-MPC is that the power converter being controlled operates with a nonconstant switching frequency [11]. As a result, the adoption of FCS-MPC for grid-connected power converter applications is discouraged due to the harmonic content limit imposed by grid codes [12]. For this reason, several modifications have been proposed for FCS-MPC to overcome this problem, which is still an ongoing research [13]–[15].

In this work, the focus is on the recently proposed approach called optimal switching sequence MPC (OSS-MPC) [16]. This consists in defining the control set by using a limited number of possible switching sequences. Then, the optimal control problem is formulated by considering the instant when

power switches change state as control input, which in a way embeds the modulator into the optimization problem. Therefore, OSS-MPC presents two main features: first, as in the conventional FCS-MPC approach, it allows one to work with a multi-objective optimization problem, including system constraints while keeping a limited computational burden; second, by contrast to the FCS-MPC method, it provides a fixed switching frequency, making the approach suitable for grid-connected power converter applications.

This paper adopts the OSS-MPC strategy presented in [17] for a single-phase grid-connected full-bridge H-NPC power converter connected to a unipolar dc-bus. Although the H-NPC can be used to obtain a bipolar dc-bus, allowing the connection of different loads at each dc-link, early studies have shown that there are some limitations in the values of the loads that can be connected to each dc-link [18]. Despite this, some works have proposed some control strategies to address the balance problem in the stable region of the converter [19]. However, to increase the operational range of the bipolar dcbus, additional circuitry should be added [20], [21]. For this reason, the most common situation is to work with the H-NPC as a unipolar dc-bus. Thus, the load is connected between the positive and negative terminals of the dc-link, while the capacitor middle point is left electrically floating. Under this situation, two main approaches have been presented in the literature to address the dc-link voltage balancing problem. A conventional solution applied to multilevel converters with a modulator stage consists of using the redundant output voltage vectors [22]. This procedure can be also adapted to work with MPC strategies [23]–[25]. Additionally, MPC allows one to formulate a multi-objective optimization problem where both the current control tracking and the dc-link voltage balance problems are included in the cost function. This approach has been extensively used since early works of FCS-MPC for NPC power converters [26] and is the most common solution to this problem when MPC is adopted as control strategy, because it provides the optimal solution for the multi-objective problem [27], [28].

In [17], the OSS-MPC was designed only to track a given current reference. Therefore, the control strategy proposed in [17] is not able to deal with the dc-link voltage unbalance problem [19]. In the paper at hand, OSS-MPC is extended to also balance the dc-link capacitor voltages in an H-NPC. As will be elucidated, incorporating the dc-link problem into the OSS-MPC is not straightforward. To do this, firstly a multi-objective optimization problem is adopted. Then, a careful analysis of the control region to evaluate the effect of the converter voltage vectors over the dc-link balance error is carried out. From this understanding, suitable switching sequence candidates (SSCs) are designed. Moreover, explicit optimal application times expressions for the multi-objective control problem considering the input constraints are obtained off-line. This reduces the computational burden since in a real-time implementation the complexity is reduced to only evaluate these expressions for each SSC. Extensive simulation and experimental results are provided to validate the closedloop performance of the proposed OSS-MPC strategy for an H-NPC converter.

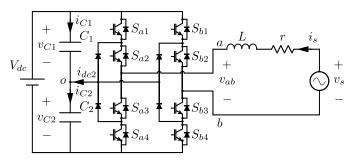

Fig. 1. Schematic circuit of a single-phase grid-connected H-NPC converter fed by a constant dc-voltage source.

#### II. SINGLE-PHASE H-NPC CONVERTER

This section briefly describes a grid-connected single-phase H-NPC converter. The schematic circuit of this converter is depicted in Fig. 1. This converter is electrically fed by a dc-source,  $V_{dc}$ , connected in parallel to two dc-link capacitors,  $C_1$  and  $C_2$ , to generate a clamping point, o. Ideally, both capacitor voltages should be balanced, i.e.,  $v_{C1} = v_{C2} = V_{dc}/2$ . If achieved, the converter can generate five distinctive voltage levels in the output voltage,  $v_{ab}$ , formed between both converter legs.

#### A. Two-Dimensional Vector Control Region

In an H-NPC converter, the combination of each individual switches,  $S_{\chi 1}, \ldots, S_{\chi 4}$ , in a leg  $\chi \in \{a,b\}$  can be represented by the following switching functions:

$$S_a, S_b \in \{-1, 0, 1\}.$$

(1)

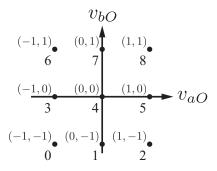

Therefore, the combination of these switching functions leads to a two-dimensional control region depicted in Fig. 2, which is formed by nine output voltage vectors,  $v_{ab\rho}$ , where  $\rho \in \{0,\ldots,8\}$ ; see Table I. Consequently, similarly to a space vector modulation strategy, the converter output voltage,  $v_{ab}$ , can be modulated by properly applying a switching sequence formed with vectors from this finite voltage vector set.

#### B. System Dynamics

Before selecting a switching sequence, it is convenient to introduce the system dynamics in terms of the output voltage vector,  $v_{ab\rho}$ . Based on [17], the continuous-time dynamic model of the grid current is given by:

$$\frac{di_s}{dt} = \frac{1}{L} \left( v_s - ri_s - v_{ab\rho} \right) \tag{2}$$

where, L and r are the inductance and resistance of the output filter, and  $v_s$  is the grid voltage. Considering that the capacitances of both capacitors are equal,  $C_1 = C_2 = C$  then, according to [29], the continuous-time dynamic model for the capacitor voltage balance,  $\Delta_v = v_{C2} - v_{C1}$ , is represented by:

$$\frac{d\Delta_v}{dt} = \frac{\Delta_i}{C} \tag{3}$$

where  $\Delta_i$  is expressed by:

$$\Delta_i = \left(S_b^2 - S_a^2\right) i_s. \tag{4}$$

Table I also presents the set of possible  $\Delta_i$  values.

Fig. 2. Finite voltage vector set for a single-phase H-NPC converter. Each vector  $\rho \in \{0,\dots,8\}$  is represented by its pair  $(S_a,S_b)$

TABLE I

VOLTAGE VECTORS FOR THE SINGLE-PHASE H-NPC CONVERTER

| Vectorρ     | 0 | 1                  | 2        | 3                   | 4 | 5                  | 6         | 7                   | 8 |

|-------------|---|--------------------|----------|---------------------|---|--------------------|-----------|---------------------|---|

| $v_{ab ho}$ | 0 | $\frac{V_{dc}}{2}$ | $V_{dc}$ | $\frac{-V_{dc}}{2}$ | 0 | $\frac{V_{dc}}{2}$ | $-V_{dc}$ | $\frac{-V_{dc}}{2}$ | 0 |

| $\Delta_i$  | 0 | $i_s$              | 0        | $-i_s$              | 0 | $-i_s$             | 0         | $i_s$               | 0 |

TABLE II VOLTAGE VECTOR EFFECT OVER  $\Delta_v$

| Voltage vector      | $i_s > 0$ | $i_s < 0$ |

|---------------------|-----------|-----------|

| $\{0, 2, 4, 6, 8\}$ | -         | -         |

| $\{1, 7\}$          | <b>↑</b>  | <b>↓</b>  |

| ${3,5}$             | <b>↓</b>  | <b>↑</b>  |

#### III. SSCs Design

As proposed in [17], an H-NPC converter can be controlled by selecting a switching sequence, Seq, composed by three voltage vectors from the finite voltage vector set, i.e.:

$$Seq = \{v_{abi,1}, v_{abk,2}, v_{abl,3}\}$$

(5a)

$$T = \{t_1, t_2, t_3\}. \tag{5b}$$

where the  $j, k, l \in \{0 \cdots 8\}$ . Moreover, T is the vector which contains the application times,  $t_n$  with  $n \in \{1, 2, 3\}$ , that each vector in Seq is applied during a sampling period  $T_s$ , i.e.,  $T_s = t_1 + t_2 + t_3$ .

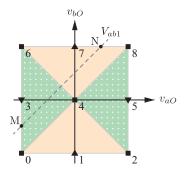

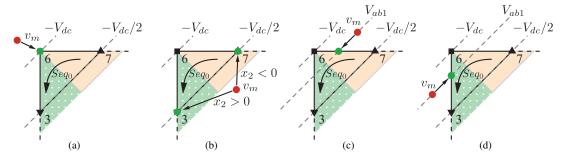

In [17], SSCs were designed with the aim of controlling the converter output current. However, the work at hand also aims to balance the dc-link capacitor voltages. Therefore, new SSCs need to be designed accordingly. To address this issue, the effect of the voltage vectors,  $v_{ab\rho}$ , over the signal  $\Delta_v$  is analyzed in Fig. 3 for  $i_s>0$ . Taking into account (4) and the fact that the current  $i_s$  is defined as being injected to the inverter in Fig. 1, the voltage vectors represented by a square ( $\blacksquare$ ) do not produce any variation on  $\Delta_v$ . The vectors represented by an upward-pointing triangle ( $\blacktriangle$ ) produce an increase on  $\Delta_v$ , whereas those represented by downward-pointing triangles ( $\blacktriangledown$ ) decrease the value of  $\Delta_v$ . An equivalent analysis can be done for  $i_s<0$ , where similar conclusions can be drawn but in this case the effect over the signal  $\Delta_v$

Fig. 3. Effect of voltage vectors over  $\Delta_v$  for  $i_s > 0$ .

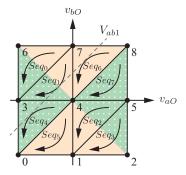

Fig. 4. Voltage vector sequences for the balancing problem.

is the opposite. Table II summarizes the voltage vector effect over  $\Delta_v$ . Hereafter, only the analysis for  $i_s>0$  is described in detail.

When  $i_s>0$ , the control region can be split into four different areas depending on how  $\Delta_v$  varies. These areas are marked in Fig. 3. Now, it is convenient to introduce an equivalent control signal,  $v_m$ , to represent the average value of these voltage vectors, i.e.:

$$v_m = \frac{1}{T_s} \left( v_{abj,1} t_1 + v_{abk,2} t_2 + v_{abl,3} t_3 \right). \tag{6}$$

Any resulting equivalent control signal,  $v_m$ , that lies in the dotted area, formed by voltage vectors  $\{0,3,4,6\}$  and  $\{2,4,5,8\}$ , decreases the value of  $\Delta_v$ . On the contrary, any  $v_m$  that lies in the solid area, constituted by  $\{0,1,2,4\}$  and  $\{4,6,7,8\}$ , increases the value of  $\Delta_v$ . Also, any  $v_m$  that belongs to a line with a slope of  $45^\circ$  provides the same average output voltage in the inverter [30]. This is illustrated in Fig. 3, where all the points located over the segment  $\overline{MN}$  generate an average output voltage equal to  $v_m = V_{ab1}$ . This implies that it is possible to control the grid current and balance the dc-link capacitor voltages independently.

Based on the above analysis, the proposed SSCs are presented in Fig. 4 and listed in Table III. These eight SSCs are designed with the aim to only switch between two adjacent voltage levels. For instance, if sequence  $Seq_0$  is finally selected then,  $v_{ab}$  will vary between  $-V_{dc}/2$  and  $-V_{dc}$ . Additionally, any equivalent control signal,  $v_m$ , can be generated using an area that increases or decreases  $\Delta_v$ . For example, in Fig. 4 the equivalent control signal  $v_m = V_{ab1}$  can be produced by the sequences  $Seq_1$ ,  $Seq_4$  and  $Seq_6$ . Note that, as shown in Table II,  $Seq_4$  tends to decrease  $\Delta_v$  because it is composed by vector 3, that decreases the value of  $\Delta_v$  for  $i_s > 0$ , and vectors

0 and 4, that do not affect  $\Delta_v$ . Therefore, any combination of these vectors will decrease  $\Delta_v$ . Similarly, any combination of voltage vectors from  $Seq_6$  leads to increase  $\Delta_v$ . Finally, since vectors 7 and 3 are inside  $Seq_1$ , then the effect of using  $Seq_1$  over  $\Delta_v$  will depend on the final application times for the voltage vectors therein. As a conclusion, the proposed set of SSCs guarantees that the dc-link capacitor voltages can always be balanced

Furthermore, the set of SSCs can be reduced as follows. If  $\Delta_v>0$  then, SSCs  $Seq_5$  and  $Seq_6$  could be not evaluated since they will further increase  $\Delta_v$ . Similarly, if  $\Delta_v<0$  then,  $Seq_4$  and  $Seq_7$  could be not considered. Under this consideration, only six SSCs have to be evaluated instead of the original eight SSCs, providing a reduction of roughly 25% in the computational cost of the algorithm compared to the original implementation, without affecting its performance. Finally, the SSCs evaluated in the algorithm are summarized in Table IV.

# IV. OSS-MPC FORMULATION FOR A SINGLE-PHASE H-NPC CONVERTER

An H-NPC converter is operated to simultaneously track a grid current reference and balance the dc-link capacitor voltages. In this work, the OSS-MPC strategy presented in [17] is adapted to achieve these control targets. Since this is a multivariable control problem, the following quadratic cost function is chosen as part of the problem formulation:

$$J = e_{i,k+1}^2 + \lambda e_{\Delta_v,k+1}^2, \tag{7}$$

where  $e_{i,k+1}=i^\star_{s,k+1}-i_{s,k+1}$  is the grid current tracking error, while  $e_{\Delta_v,k+1}=\Delta^\star_{v,k+1}-\Delta_{v,k+1}$  is the dc-link voltage balance error at the next sampling instant, k+1. Moreover, by using an  $\ell_2$ -norm, stability of OSS-MPC may be studied using approaches like the ones in [31] or [32]. The weighting factor  $\lambda \geq 0$  is a tuning parameter that adjusts the trade-off (relative importance) between both control targets. Then, the key idea in an OSS-MPC formulation is to represent these tracking errors as a function of an SSC,  $Seq_m$ , and its associated an application time vector  $T_m$ . Therefore, the OSS-MPC strategy should provide the optimal pair  $\{Seq^{\rm opt}, T^{\rm opt}\}$ .

# A. Grid Current Tracking Error

Considering (2), the rate of change of the grid current caused by each output voltage vector in an SSC,  $Seq_m$ , is given by:

$$f_{i_s n} = \frac{di_s}{dt} \Big|_{v_{ab\rho,n}} = \frac{1}{L} (v_s - ri_s - v_{ab\rho,n}), \forall \rho \in \{0 \cdots 8\}.$$

(8)

with  $n \in \{1, 2, 3\}$ . Following the steps in [17], the predicted grid current tracking error,  $e_{i,k+1}$ , can be computed as:

$$e_{i,k+1} = e_{i0} - \left( (f_{i_s1} - f_{i_s3}) t_1 + (f_{i_s2} - f_{i_s3}) t_2 + f_{i_s3} T_s \right),$$

(9)

where  $e_{i0} = i_{s,k+1}^{\star} - i_{s,k}$ , in which  $i_{s,k}$  is the measured grid current at the sampling instant k. Moreover,  $t_n$ , are the application times as per (5b).

TABLE III

VOLTAGE VECTORS SEQUENCE FOR THE BALANCING PROBLEM

| m | $Seq_m$       | m | $Seq_m$       |

|---|---------------|---|---------------|

| 0 | $\{7, 6, 3\}$ | 4 | $\{4, 3, 0\}$ |

| 1 | $\{7, 4, 3\}$ | 5 | $\{4, 1, 0\}$ |

| 2 | $\{5, 4, 1\}$ | 6 | $\{8, 7, 4\}$ |

| 3 | $\{5, 2, 1\}$ | 7 | $\{8, 5, 4\}$ |

TABLE IV

SEQUENCE CANDIDATES FOR THE BALANCING PROBLEM

|             | $\Delta_v \ge 0$                                                        | $\Delta_v < 0$                                                            |

|-------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|

| $i_s \ge 0$ | $\begin{cases} Seq_0, Seq_1, Seq_2, \\ Seq_3, Seq_4, Seq_7 \end{cases}$ | $ \begin{cases} Seq_0, Seq_1, Seq_2, \\ Seq_3, Seq_5, Seq_6 \end{cases} $ |

| $i_s < 0$   | $ \left\{ Seq_0, Seq_1, Seq_2, \\ Seq_3, Seq_5, Seq_6 \right\} $        | $ \left\{ Seq_0, Seq_1, Seq_2, \\ Seq_3, Seq_4, Seq_7 \right\} $          |

# B. DC-Link Capacitor Voltage Balance

Similarly to the grid current case and taking into account (3), the rate of change of the dc-link capacitor voltage balance,  $\Delta_v$ , caused by each output vector in an SSC,  $Seq_m$ , is represented by:

$$f_{\Delta_v n} = \frac{d\Delta_v}{dt} \bigg|_{v_{obs}, n}.$$

(10)

Then, following the OSS-MPC principle, the next step dc-link voltage balanced error,  $e_{\Delta_v,k+1}$ , generated by an SSC,  $Seq_m$ , can be predicted by calculating the following expression:

$$e_{\Delta_v,k+1} = e_{\Delta_v0} + (f_{\Delta_v1} - f_{\Delta_v3})t_1 + (f_{\Delta_v2} - f_{\Delta_v3})t_2 + f_{\Delta_v3}T_s$$

(11)

where  $e_{\Delta_v 0} = \Delta_{v,k+1}^{\star} - \Delta_{v,k}$ , in which  $\Delta_{v,k} = v_{C2,k} - v_{C1,k}$  represents the dc-link capacitor voltage difference value at the instant k and  $\Delta_{v,k+1}^{\star}$  is the desired dc-link voltage balance error at the next sampling instant k+1, which generally is 0.

#### C. OSS-MPC Problem

Considering (9) and (11), for each SSC,  $Seq_m$ , the cost function (7) can be expressed as a function of the application times,  $t_n$ , as per (5b). Consequently, both the OSS and optimal application times are obtained by solving, at each sampling instant k, the following problem:

$$\{Seq^{\rm opt}, T^{\rm opt}\} = \arg\min_{Seq_m} \left\{ \min_{T_m} \{J(Seq_m, T_m)\} \right\} \quad (12a)$$

subject to:

$$t_n \ge 0, \ \forall n \in \{1, 2, 3\}$$

(12b)

$$T_s = t_1 + t_2 + t_3.$$

(12c)

Note that the OSS-MPC problem considers two optimizations. Firstly, for each  $Seq_m$ , an optimal application time vector,  $T_m^{\rm opt}$ , is obtained (internal optimization). Then, considering these optimal times, each pair  $\{Seq_m, T_m^{\rm opt}\}$  is evaluated into the cost function. Finally, the OSS,  $Seq^{\rm opt}$ , is the  $Seq_m$  that

$$t_1 \bigg|_{Sea} = \frac{e_{i0} \left( f_{\Delta_v 3} - f_{\Delta_v 2} \right) + e_{\Delta_v 0} \left( f_{i_s 3} - f_{i_s 2} \right) + T_s \left( f_{i_s 3} f_{\Delta_v 2} - f_{i_s 2} f_{\Delta_v 3} \right)}{\left( f_{i_s 1} \left( f_{\Delta_v 3} - f_{\Delta_v 2} \right) + f_{i_s 2} \left( f_{\Delta_v 1} - f_{\Delta_v 3} \right) + f_{i_s 3} \left( f_{\Delta_v 2} - f_{\Delta_v 1} \right) \right)}$$

$$(17)$$

$$t_{1}\Big|_{Seq_{m}} = \frac{e_{i0} \left(f_{\Delta_{v}3} - f_{\Delta_{v}2}\right) + e_{\Delta_{v}0} \left(f_{i_{s}3} - f_{i_{s}2}\right) + T_{s} \left(f_{i_{s}3} f_{\Delta_{v}2} - f_{i_{s}2} f_{\Delta_{v}3}\right)}{\left(f_{i_{s}1} \left(f_{\Delta_{v}3} - f_{\Delta_{v}2}\right) + f_{i_{s}2} \left(f_{\Delta_{v}1} - f_{\Delta_{v}3}\right) + f_{i_{s}3} \left(f_{\Delta_{v}2} - f_{\Delta_{v}1}\right)\right)}$$

$$t_{2}\Big|_{Seq_{m}} = \frac{e_{i0} \left(f_{\Delta_{v}1} - f_{\Delta_{v}3}\right) + e_{\Delta_{v}0} \left(f_{i_{s}1} - f_{i_{s}3}\right) + T_{s} \left(f_{i_{s}1} f_{\Delta_{v}3} - f_{i_{s}3} f_{\Delta_{v}1}\right)}{\left(f_{i_{s}1} \left(f_{\Delta_{v}3} - f_{\Delta_{v}2}\right) + f_{i_{s}2} \left(f_{\Delta_{v}1} - f_{\Delta_{v}3}\right) + f_{i_{s}3} \left(f_{\Delta_{v}2} - f_{\Delta_{v}1}\right)\right)}$$

$$(17)$$

$$t_3 \bigg|_{Sea_m} = T_s - t_1 - t_2. \tag{19}$$

provides the minimum cost (external optimization), being its associated application times the optimal one, i.e.,  $T^{\text{opt}}$ .

#### V. SOLUTION TO THE OSS-MPC PROBLEM

#### A. Unconstrained Optimal Application Times

In OSS-MPC, it is firstly required to solve the internal optimization, i.e., to obtain the optimal applications time,  $T_m^{\mathrm{opt}}$ for each  $Seq_m$ . To do this, the constrains (12b)-(12c) can be firstly neglected, i.e.,  $t_n \in \mathbb{R}$ . Since these application times are continuous variables, one can perform a partial derivative of the cost function to obtain the unconstrained optimal times, i.e.:

$$\frac{\partial J}{\partial t_1}\Big|_{Seq_m} = 0 \; ; \; \frac{\partial J}{\partial t_2}\Big|_{Seq_m} = 0.$$

(13)

Considering (9), (11) and (7), the equation system (13) yields:

$$-2(f_{i_s1} - f_{i_s3}) A + 2\lambda (f_{\Delta_v1} - f_{\Delta_v3}) B = 0$$

(14a)

$$-2(f_{i_s2}-f_{i_s3})A + 2\lambda(f_{\Delta_v2}-f_{\Delta_v3})B = 0,$$

(14b)

where

$$A \triangleq e_{i0} - (f_{i_s1} - f_{i_s3}) t_1 - (f_{i_s2} - f_{i_s3}) t_2 - f_{i_s3} T_s$$

(15)

$$B \triangleq e_{\Delta_{v0}} + (f_{\Delta_{v1}} - f_{\Delta_{v3}}) t_1 + (f_{\Delta_{v2}} - f_{\Delta_{v3}}) t_2 + f_{\Delta_{v3}} T_s.$$

(16)

By analyzing the equation system (14a)-(14b), it is possible to observe that this system has a unique solution only if A = B = 0. Therefore, it can be concluded that the weighting factor,  $\lambda$ , does not have any effect over the unconstrained optimal solution of the problem (13). Finally, solving (15)-(16) with A = B = 0 leads to the unconstrained optimal application time vector,  $T_m = \{t_1, t_2, t_3\}$ , where each application times,  $t_n$ , is explicitly represented by (17)-(19).

# B. Constrained Application Times

If for a given  $Seq_m$ , its application time vector,  $T_m$ , computed from (17)-(19) fulfills (12b)-(12c) then, its associated equivalent control signal,  $v_m$ , calculated from (6) will be located inside its corresponding sector. On the contrary, if these constraints are not satisfied then,  $v_m$  will lie outside the sector limits. Therefore, the equivalent control signal cannot be generated by the inverter in practice. To solve this problem, a new application time vector,  $T_m$ , should be obtained taking into account system constraints and the effect of  $v_m$  over both  $i_s$  and  $\Delta_v$ . This situation is shown in Fig. 5 for an equivalent control signal generated by the voltage vectors in  $Seq_0$  and  $i_s \geq 0$ . A similar analysis can be carried out for the other

TABLE V Constrained Time Intervals for Sequence  $Seq_0$  when  $i_s \geq 0$

| Condition                   | $t_1$       | $t_2$                                    | $t_3$       |

|-----------------------------|-------------|------------------------------------------|-------------|

| $v_m < -V_{dc}$             | 0           | $T_s$                                    | 0           |

| $v_m > -V_{dc}/2$           |             |                                          |             |

| and                         | 0           | 0                                        | $T_s$       |

| $\Delta_v > 0$              |             |                                          |             |

| $v_m > -V_{dc}/2$           |             |                                          |             |

| and                         | $T_s$       | 0                                        | 0           |

| $\Delta_v < 0$              |             |                                          |             |

| $-V_{dc} < v_m < -V_{dc}/2$ |             |                                          |             |

| and                         | $T_s - t_2$ | $-\left(\frac{2v_m}{V_{dc}}+1\right)T_s$ | 0           |

| $\Delta_v < 0$              |             |                                          |             |

| $-V_{dc} < v_m < -V_{dc}/2$ |             |                                          |             |

| and                         | 0           | $-\left(\frac{2v_m}{V_{dc}}+1\right)T_s$ | $T_s - t_2$ |

| $\Delta_v > 0$              |             | ,                                        |             |

SSCs and  $i_s < 0$ . However, for the sake of brevity, the study is only presented for  $Seq_0$ .

Four different situations are highlighted in Fig. 5 for the sequence  $Seq_0$ . The first one appears when  $v_m < -V_{dc}$ . As the minimum output voltage that the inverter can produce is  $-V_{dc}$ . Then, during the whole sampling period only the output voltage vector 6 is applied (Fig. 5(a)). The second scenario arises if  $v_m > -V_{dc}/2$ . If the largest output voltage that sequence  $Seq_0$  can produce is  $-V_{dc}/2$  then, the output should be limited to this value. To produce this voltage value, output voltage vectors 3 and 7 can be used. If  $\Delta_v \geq 0$  then voltage vector 3 is used; otherwise, 7 is selected (Fig. 5(b)). Finally, when condition  $-V_{dc} < v_m < -V_{dc}/2$  holds, it is possible to generate the same average output voltage located in one of the edge of  $Seq_0$ . For this purpose, a combination of output voltage vectors in the sets  $\{7,6\}$  or  $\{6,3\}$  (Figs. 5(c) and 5(d)) can be used. The set  $\{6,3\}$  is chosen when  $\Delta_v \geq 0$ , otherwise,  $\{7,6\}$  is used. This analysis leads to the modified application times for  $Seq_0$  when  $i_s \geq 0$  presented in Table V.

Fig. 5. Computation of time intervals for sequence  $Seq_0$  according to system constraints when  $i_s \ge 0$ : (a)  $v_m < -V_{dc}$ , (b)  $v_m > -V_{dc}/2$ , (c)  $-V_{dc} < v_m < -V_{dc}/2$  and  $\Delta_v < 0$ , (d)  $-V_{dc} < v_m < -V_{dc}/2$  and  $\Delta_v > 0$ .

### C. Analysis of the Weighting Factor Effect

In general, weighting factors have an important effect over the MPC performance, specially when FCS-MPC is adopted. Although there are some proposals to design these values it is still an open issue [33], [34]. Here, to analyze the effect of the weighting factor  $\lambda$  over the optimal application times, (15) and (16) should be studied. Note that  $A = e_{i,k+1}$  and  $B = e_{\Delta_n, k+1}$ . Therefore, independently of  $\lambda$ , the cost function designed in (7) will become 0 whenever the application times computed from (17)-(19) fulfill (12b)-(12c). This is an important advantage over the FCS-MPC approach. FCS-MPC only considers a finite set of output voltage vectors applied during the whole sampling period. Thus, in general, there is no guarantee that the cost function will become zero for any of the output voltage vectors candidates. By contrast, the proposed OSS-MPC will always choose a pair  $\{Seq_m, T_m\}$ , that satisfies this condition, when available, as the optimal one, since this is the minimum possible value for the cost function. This will be the most common situation during a steady state operation of the H-NPC converter, as long as the converter actual power is equal or less than its rated power. Therefore, the steady-state performance of an H-NPC converter governed by the proposed OSS-MPC strategy is independent of the control design parameter,  $\lambda$ . In this sense, the value of  $\lambda$  may have an effect over the closed-loop performance only during transients, when the pair  $\{Seq_m, T_m\}$  may not fulfill the optimal problem constraints and the constrained application times computed in Section V-B should be used. This is an important feature of the proposed control strategy compared to other approaches. In general, for other control strategies, the weighting factor also affects to the system performance in steady state. Therefore, the proposed control strategy eases the design process of  $\lambda$ .

#### D. OSS-MPC Implementation

Once suitable application time vectors,  $T_m$ , are calculated for each  $Seq_m$  then, the second optimization stage needs to be addressed to obtain the OSS,  $Seq^{\rm opt}$ . Since the number of SSCs is finite, 8 in this case, the cost function (7) can be evaluated for each pair  $\{Seq_m, T_m\}$ , in a similar fashion than FCS-MPC. Therefore, the OSS and its associated application time vector,  $\{Seq^{\rm opt}, T^{\rm opt}\}$ , are selected as the ones that minimize J in (7). Finally, implementation of the OSS,  $Seq^{\rm opt}$ , can be performed as described in Table VI, where  $\delta_{1a}$  and  $\delta_{2a}$  stand

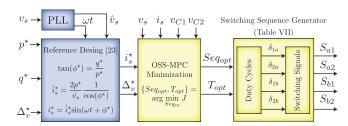

Fig. 6. Block diagram of the proposed OSS-MPC strategy.

for the duty cycles of the power switches  $S_{a1}$  and  $S_{a2}$  in the converter leg a, respectively, while  $\delta_{1b}$  and  $\delta_{2b}$  represent the duty cycles of the power switches  $S_{b1}$  and  $S_{b2}$  in the converter leg b, respectively. Fig. 6 represents the block diagram of the proposed strategy, where the reference design [35] and PLL, [36] are used to generate the reference current.

#### VI. RESULTS

#### A. Simulation Results

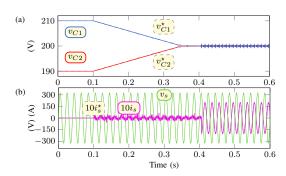

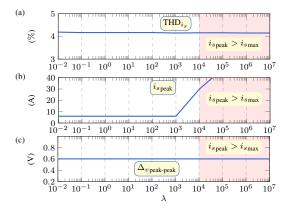

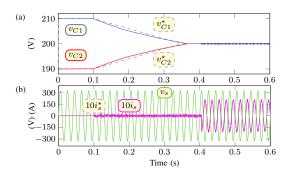

Simulation results of a single-phase grid-connected H-NPC converter using the proposed dc-link voltage balancing OSS-MPC strategy are presented to analyze the weighting factor effect over the closed-loop response. The following results are obtained to match the parameters shown in Table VII of the experimental setup. All the results reported are designed to obtain a converter output voltage with dominant harmonic components fixed around 5 kHz, while the switching frequency  $(f_{sw})$  is 2.5 kHz. Figure 7 shows results for the OSS-MPC using  $\lambda = 1$ . The weighting factor  $\lambda$  can be used for defining the time needed to achieve the capacitor voltage balance. However, large values of  $\lambda$  will increase the peak current during the transient. In addition, the settling time will depend on the system parameters. To avoid this situation, it is proposed to define a dynamic reference for the dc-link unbalance reference  $\Delta_{v,k+1}^{\star}$ . The approach defines a ramp that decays from its initial value  $\Delta_{v,k+1}^\star = v_{C2,k+1}^\star - v_{C1,k+1}^\star$  to  $\Delta_{v,k+1}^\star = 0$  in a given time. The main advantage with this approach is that the settling time is independent of  $\lambda$ . In that case,  $\lambda$  will only have an affect over the peak current value during the transient. Here, the ramp slope is set to achieve the balanced condition in 250 ms starting from an arbitrary unbalanced voltage difference equal to 20 V. Smaller values for the settling time can be used but there is a limit for which the dc-link voltage balancing performance is affected by the

TABLE VI SWITCHING DUTY CYCLES FOR THE BALANCING PROBLEM

| Sequence | $v_{ab\rho}$ | $S_a$ $S_b$                                                   | $S_{a1}$ $S_{a2}$ | $S_{b1}$ $S_{b2}$ | Duty                                                                                                      |

|----------|--------------|---------------------------------------------------------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------|

| 0        | 7<br>6<br>3  | $ \begin{array}{cccc} 0 & 1 \\ -1 & 1 \\ -1 & 0 \end{array} $ | 0 1<br>0 0<br>0 0 | 1 1<br>1 1<br>0 1 | $\delta_{1a} = 0$ $\delta_{2a} = \frac{t_1}{T_s}$ $\delta_{1b} = \frac{t_1 + t_2}{T_s}$ $\delta_{2b} = 1$ |

| 1        | 7<br>4<br>3  | $ \begin{array}{ccc} 0 & 1 \\ 0 & 0 \\ -1 & 0 \end{array} $   | 0 1<br>0 1<br>0 0 | 1 1<br>0 1<br>0 1 | $\delta_{1a} = 0$ $\delta_{2a} = \frac{t_1 + t_2}{T_s}$ $\delta_{1b} = \frac{t_1}{T_s}$ $\delta_{2b} = 1$ |

| 2        | 5<br>4<br>1  | $ \begin{array}{ccc} 1 & 0 \\ 0 & 0 \\ 0 & -1 \end{array} $   | 1 1<br>0 1<br>0 1 | 0 1<br>0 1<br>0 0 | $\delta_{1a} = \frac{t_1}{T_s}$ $\delta_{2a} = 1$ $\delta_{1b} = 0$ $\delta_{2b} = \frac{t_1 + t_2}{T_s}$ |

| 3        | 5<br>2<br>1  | $ \begin{array}{ccc} 1 & 0 \\ 1 & -1 \\ 0 & -1 \end{array} $  | 1 1<br>1 1<br>0 1 | 0 1<br>0 0<br>0 0 | $\delta_{1a} = \frac{t_1 + t_2}{T_s}$ $\delta_{2a} = 1$ $\delta_{1b} = 0$ $\delta_{2b} = \frac{t_1}{T_s}$ |

| 4        | 4<br>3<br>0  | $ \begin{array}{ccc} 0 & 0 \\ -1 & 0 \\ -1 & -1 \end{array} $ | 0 1<br>0 0<br>0 0 | 0 1<br>0 1<br>0 0 | $\delta_{1a} = 0$ $\delta_{2a} = \frac{t_1}{T_s}$ $\delta_{1b} = 0$ $\delta_{2b} = \frac{t_1 + t_2}{T_s}$ |

| 5        | 4<br>1<br>0  | $ \begin{array}{ccc} 0 & 0 \\ 0 & -1 \\ -1 & -1 \end{array} $ | 0 1<br>0 1<br>0 0 | 0 1<br>0 0<br>0 0 | $\delta_{1a} = 0$ $\delta_{2a} = \frac{t_1 + t_2}{T_s}$ $\delta_{1b} = 0$ $\delta_{2b} = \frac{t_1}{T_s}$ |

| 6        | 8<br>7<br>4  | 1 1<br>0 1<br>0 0                                             | 1 1<br>0 1<br>0 1 | 1 1<br>1 1<br>0 1 | $\delta_{1a} = \frac{t_1}{T_s}$ $\delta_{2a} = 1$ $\delta_{1b} = \frac{t_1 + t_2}{T_s}$ $\delta_{2b} = 1$ |

| 7        | 8<br>5<br>4  | 1 1<br>1 0<br>0 0                                             | 1 1<br>1 1<br>0 1 | 1 1<br>0 1<br>0 1 | $\delta_{1a} = \frac{t_1 + t_2}{T_s}$ $\delta_{2a} = 1$ $\delta_{1b} = \frac{t_1}{T_s}$ $\delta_{2b} = 1$ |

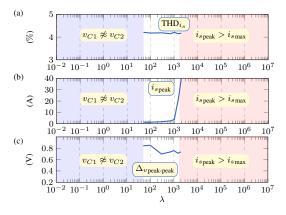

system parameters. Therefore, from the practical point of view, it is recommended to define the settling time in the range from 60 ms to 300 ms. Note that this ramp resembles a standard start-up procedure for grid-connected inverters, so  $i_s^{\star}$  is set to zero. This is an extreme condition for the controller because it has to balance  $v_{C1}$  and  $v_{C2}$  without loosing the tracking of  $i_s \approx 0$ . In addition, the trade-off between the THD of  $i_s$ , its peak value during the balancing transient and the steady-state  $\Delta_v$  ripple for different values of  $\lambda$  is analyzed in Fig. 8. This figure shows that the range of possible values for  $\lambda$  is only limited by the current peak value during the balancing transient. Therefore,  $\lambda$  must be chosen to keep  $i_{speak}$  below the maximum converter current  $i_{smax}$ .

#### TABLE VII SYSTEM PARAMETERS

| Variable   | Description                | Value                 | p.u.        |

|------------|----------------------------|-----------------------|-------------|

| $S_r$      | Total rated apparent power | 3.5 kVA               | 1           |

| $v_s$      | Grid voltage               | 230 V                 | 1           |

| $V_{dc}$   | DC-link voltage            | 400 V                 | 1           |

| $C_1, C_2$ | DC-link capacitors         | 2475 $\mu \mathrm{F}$ | 0.085       |

| L          | Filter inductor            | 10 mH                 | 0.20        |

| r          | Filter resistance          | $2.01~\text{m}\Omega$ | 0.013       |

| $f_s$      | Sampling frequency         | 5 kHz                 | 1           |

| $f_{sw}$   | Switching frequency        | 2.5 kHz               | 0.5         |

| $T_e$      | Execution time             | $26.2~\mu \mathrm{s}$ | $0.13T_{s}$ |

Fig. 7. Capacitor voltage balancing (OSS-MPC): (a) capacitor voltages and (b) grid voltage and grid current.

Fig. 8. Weighting factor effect over (OSS-MPC): (a) THD of  $i_s$ , (b) peak value of  $i_s$  during the balancing transient, and (c) steady-state  $\Delta_v$  ripple.

For comparison purposes, same results and analysis for FCS-MPC [35] considering the cost function in (7) are shown in Fig. 9 and Fig. 10 respectively. Here, the sampling frequency  $f_s=1/T_s=12~\mathrm{kHz}$  and  $\lambda=700~\mathrm{are}$  set to achieve a similar steady-state performance compared to OSS-MPC, i.e.,  $\mathrm{THD}_{i_s}=4.20\%$ . The axes limits in Fig. 10 are intentionally set as per Fig. 8 in order to demonstrate that FCS-MPC achieves similar results. However, there is a lower limit for  $\lambda$  in which the steady-state  $\Delta_v$  ripple is increased. Below this limit, FCS-MPC is not able to balance i.e.  $v_{C1}\not\approx v_{C2}$ . Note that OSS-MPC also extends the upper limit for  $\lambda$  for the same  $i_{smax}$ . As a result, the OSS-MPC performance is almost

Fig. 9. Capacitor voltage balance (FCS-MPC): (a) capacitor voltages and (b) grid voltage and grid current.

Fig. 10. Weighting factor effect over (FCS-MPC): (a) THD of  $i_s$ , (b) peak value of  $i_s$  during the balancing transient, and (c) steady-state  $\Delta_v$  ripple.

independent of  $\lambda$  in a larger range of values. Therefore, the tuning process of the OSS-MPS is easier compared with the FCS-MPC approach.

So far, the inductance and capacitance have been assumed to be fixed and known values. However, in most applications these values typically vary in an unknown manner, resulting in parameters uncertainty. To study this situation, it has been carried out a sensibility analysis of the controller against errors of inductance and capacitance values used in the prediction model compared to the actual ones in the circuit. In general, the results from this study pointed out that the proposed control algorithm can be considered robust against variations on these parameters. In fact, only large deviations on the values used in the prediction model produce a noticeable degradation on the control performance. From a practical point of view, it can be stated that errors on these parameters in the range of -20% to +20% do not produce a significant variation of the OSS-MPC performance. This result is similar when compared against conventional FCS-MPC under this kind of situation [23], [35].

#### B. Experimental Results

The proposed control algorithm was implemented in a dSPACE DS1106 with  $f_s$  equal to 5 kHz. Although the formulation of the proposed control strategy was done in k+1, the implementation considers delay compensation using estimated values for k+1 and predictions in k+2. A double updated symmetrical PWM method was used for implementing the

modulation stage on the dSPACE's DS5203 FPGA board. A bidirectional controlled dc-voltage source (REGATRON TC.4.1200.80.Q14), governed by its internal controller and connected to the dc-link of the H-NPC, is used to generate  $V_{dc}$ .

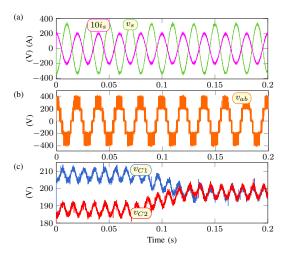

### C. DC-Link Voltage Balancing Dynamic Performance

To verify the balancing capability of the proposed controller, the dc-link capacitor voltages are forced to present an initial unbalance. To do so, it is taken into account that the term  $e_{\Delta_v,k+1}$  in (7) regulates the actual unbalance value  $\Delta_{v,k+1}$ to a predetermined reference  $\Delta_{v,k+1}^{\star}$ . In general,  $\Delta_{v,k+1}^{\star}$  is set to zero to balance the dc-link capacitor voltage values. However, one can set a different value to this reference. As an initial test, a change in the value of the capacitor voltage difference reference  $\Delta_{v,k+1}^{\star}$  from 20 V to 0 V at  $t=0.07~\mathrm{s}$ is introduced as depicted in Fig. 11. At this moment, the actual value of  $\Delta_{v,k+1}^{\star}$  start to decay with a ramp slope of 166.6 V/s. Thus, a settling time of 60 ms is expected. For the sake of clarity in the scopes, in this test, the settling time has been set to 60 ms compared to the 250 ms from the simulation results, while  $p^*$  and  $q^*$  equal to -3.25 kW  $(i_s^\star = 20 \text{ A} \text{ and } \phi^\star = \pi) \text{ and } 0 \text{ VAr, respectively. Note}$ that the grid-voltage,  $v_s$ , is affected by the grid-current ripple due to the fact that  $v_s$  was generated using a controlled acvoltage source (REGATRON TC.ACS.50) in series with a 10 kVA isolation transformer. The effect of these harmonic components is mitigated by implementing a reconstructed version of  $v_{s,k}$  and their estimated values from a PLL as described in detail in [17]. Since the proposed dc-link voltage balancing algorithm is based on  $V_{dc}$  as a constant or slowly variant value, both capacitor voltages were filtered using a first order discrete low-pass filter with a cut-off frequency of 25 Hz. The capacitor voltages from Fig. 11(c) reach the balanced condition after three grid voltage cycles as expected, where no undesired spikes in the grid-current are observed. Note that the dc source power supply generates a low frequency dc voltage ripple which depends on its the internal controller performance and not on the H-NPC controller itself. This situation forces the proposed controller to deal with a nonconstant  $V_{dc}$ . The experimental results show that the proposed OSS-MPC is robust against this disturbance and is able to work properly under such situation.

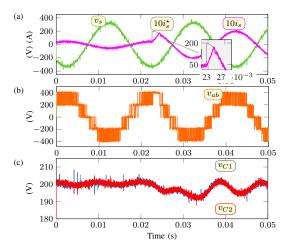

# D. Grid-Current Tracking Dynamic Performance

A step change in the active power reference  $p^*$  from -0.81 to -3.25 kW, equivalent to  $\hat{i}_s^*$  from -5 to -20 A and  $\phi^* = \pi$  was introduced as depicted in Fig. 12. Fig. 12(a) includes a zoom view of the results showing the grid-current tracking performance. Note that the current slope is limited by L and the maximum converter output voltage during the transient operation, which in this case is  $V_{dc}$ . The proposed controller is able to quickly provide this voltage. The dclink voltage balancing dynamic performance remains constant  $(\Delta_v \approx 0)$  despite the low-frequency transient oscillation due to the internal dc-link voltage controller, as shown in Fig. 12(c). This test resembles the operation of a back-to-back converter

Fig. 11. Capacitor voltage balance: (a) grid voltage and grid current, (b) converter output voltage, and (c) capacitor voltages.

Fig. 12. Current reference step change from 5 to 20 A: (a) grid voltage and current, (b) converter output voltage, and (c) capacitor voltages.

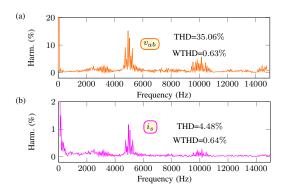

Fig. 13. Steady state spectrum analysis of: (a)  $v_{ab}$ , and (b)  $i_s$ .

where the dc-link inverter voltage is provided by an ac-dc rectifier stage, which in this case the dc-voltage source is set at 400 V.

# E. Steady-State Performance

Finally, Fig. 13 shows the steady-state spectrum of  $v_{ab}$  and  $i_s$ . Each associated spectrum presents dominant harmonic components around 5 kHz. The low-frequency harmonic con-

tent in the grid current is characterized by a magnitude less than 0.5 % of the fundamental component, which is in concordance with the recommendations of the IEEE Std. 519, [12].

#### VII. CONCLUSION

In this work, an OSS-MPC for a single-phase gridconnected H-NPC power converter was presented. Besides the control of the grid current, the proposed multi-objective OSS-MPC also considers the dc-link capacitor voltage balancing problem. To do this, the control region of the power converter was carefully analyzed. From this study, suitable SSCs were designed by considering the effect of each converter voltage vector over the dc-link balance error. A simulation study of the weighting factor effect over the closed-loop performance was provided, showing that this only has an impact over the peak current during transients, with no effect over the steady-state performance. This is a major advantage when compared to FCS-MPC. The proposed strategy was experimentally validated in a 3.5 kVA laboratory setup. The control strategy was able to effectively track the desired grid current reference and balance the dc-link capacitor voltages. Despite the benefits of the proposed control strategy, future work can be carried out to develop a theoretical stability analysis for OSS-MPC strategies and to improve its performance. Two main characteristics can be study. On one hand, if one can find first the optimal switching sequence, then the computational burden of the algorithm could be reduced. On the other hand, output constraints could be considered to solve the optimal control problem with constraints and compute the application times expressions off-line. This will allow the converter to work closer to its operational limits. Both are open research issues that will improve the features of the proposed OSS-MPC.

#### REFERENCES

- J. I. Leon, S. Vazquez, and L. G. Franquelo, "Multilevel converters: Control and modulation techniques for their operation and industrial applications," *Proc. IEEE*, vol. 105, DOI 10.1109/JPROC.2017.2726583, no. 11, pp. 2066–2081, Nov. 2017.

- [2] G. Wang, G. Konstantinou, C. D. Townsend, J. Pou, S. Vazquez, G. D. Demetriades, and V. G. Agelidis, "A review of power electronics for grid connection of utility-scale battery energy storage systems," *IEEE Trans. Sustain. Energy*, vol. 7, DOI 10.1109/TSTE.2016.2586941, no. 4, pp. 1778–1790, Oct. 2016.

- [3] M. Malinowski, J. I. Leon, and H. Abu-Rub, "Solar photovoltaic and thermal energy systems: Current technology and future trends," *Proc. IEEE*, vol. 105, DOI 10.1109/JPROC.2017.2690343, no. 11, pp. 2132–2146, Nov. 2017.

- [4] A. Steimel, "Electric railway traction in europe," *IEEE Ind. Appl. Mag.*, vol. 2, DOI 10.1109/2943.541241, no. 6, pp. 6–17, Nov. 1996.

- [5] K. Song, G. Konstantinou, W. Mingli, P. Acuna, R. P. Aguilera, and V. G. Agelidis, "Windowed she-pwm of interleaved four-quadrant converters for resonance suppression in traction power supply systems," *IEEE Trans. Power Electron.*, vol. 32, DOI 10.1109/TPEL.2016.2636882, no. 10, pp. 7870–7881, Oct. 2017.

- [6] P. Lezana, C. A. Silva, J. Rodriguez, and M. A. Perez, "Zero-steady-state-error input-current controller for regenerative multilevel converters based on single-phase cells," *IEEE Trans. Ind. Electron.*, vol. 54, DOI 10.1109/TIE.2007.891994, no. 2, pp. 733–740, Apr. 2007.

- [7] D. Karagiannis, E. Mendes, A. Astolfi, and R. Ortega, "An experimental comparison of several pwm controllers for a single-phase ac-dc converter," *IEEE Trans. Control Syst. Technol.*, vol. 11, DOI 10.1109/TCST.2003.815549, no. 6, pp. 940–947, Nov. 2003.

- [8] S. Vazquez, J. I. Leon, L. G. Franquelo, J. Rodriguez, H. A. Young, A. Marquez, and P. Zanchetta, "Model predictive control: A review of its applications in power electronics," *IEEE Ind. Electron. Mag.*, vol. 8, DOI 10.1109/MIE.2013.2290138, no. 1, pp. 16–31, Mar. 2014.

- [9] S. Vazquez, J. Rodriguez, M. Rivera, L. G. Franquelo, and M. Norambuena, "Model predictive control for power converters and drives: Advances and trends," *IEEE Trans. Ind. Electron.*, vol. 64, DOI 10.1109/TIE.2016.2625238, no. 2, pp. 935–947, Feb. 2017.

- [10] P. Cortes, M. P. Kazmierkowski, R. M. Kennel, D. E. Quevedo, and J. Rodriguez, "Predictive control in power electronics and drives," *IEEE Trans. Ind. Electron.*, vol. 55, DOI 10.1109/TIE.2008.2007480, no. 12, pp. 4312–4324, Dec. 2008.

- [11] J. Rodriguez, M. P. Kazmierkowski, J. R. Espinoza, P. Zanchetta, H. Abu-Rub, H. A. Young, and C. A. Rojas, "State of the art of finite control set model predictive control in power electronics," *IEEE Trans. Ind. Informat.*, vol. 9, DOI 10.1109/TII.2012.2221469, no. 2, pp. 1003– 1016, May. 2013.

- [12] "IEEE recommended practice and requirements for harmonic control in electric power systems," *IEEE Std 519-2014 (Revision of IEEE Std 519-1992)*, DOI 10.1109/IEEESTD.2014.6826459, pp. 1–29, Jun. 2014.

- [13] P. Cortes, J. Rodriguez, D. Quevedo, and C. Silva, "Predictive current control strategy with imposed load current spectrum," *IEEE Trans. Power Electron.*, vol. 23, DOI 10.1109/TPEL.2007.915605, no. 2, pp. 612–618, Mar. 2008.

- [14] R. O. Ramirez, J. R. Espinoza, F. Villarroel, E. Maurelia, and M. E. Reyes, "A novel hybrid finite control set model predictive control scheme with reduced switching," *IEEE Trans. Ind. Electron.*, vol. 61, DOI 10.1109/TIE.2014.2308137, no. 11, pp. 5912–5920, Nov. 2014.

- [15] M. Aguirre, S. Kouro, C. A. Rojas, J. Rodriguez, and J. I. Leon, "Switching frequency regulation for fcs-mpc based on a period control approach," *IEEE Trans. Ind. Electron.*, vol. 65, DOI 10.1109/TIE.2017.2777385, no. 7, pp. 5764–5773, Jul. 2018.

- [16] S. Vazquez, A. Marquez, R. Aguilera, D. Quevedo, J. I. Leon, and L. G. Franquelo, "Predictive optimal switching sequence direct power control for grid-connected power converters," *IEEE Trans. Ind. Electron.*, vol. 62, DOI 10.1109/TIE.2014.2351378, no. 4, pp. 2010–2020, Apr. 2015.

- [17] S. Vazquez, R. P. Aguilera, P. Acuna, J. Pou, J. I. Leon, L. G. Franquelo, and V. G. Agelidis, "Model predictive control for single-phase npc converters based on optimal switching sequences," *IEEE Trans. Ind. Electron.*, vol. 63, DOI 10.1109/TIE.2016.2594227, no. 12, pp. 7533–7541, Dec. 2016.

- [18] E. Christopher and M. Sumner, "The control of npc grid connected converter for interfacing to unbalanced dc link loads," in 2009 13th European Conference on Power Electronics and Applications, pp. 1–10, Sep. 2009.

- [19] J. Ma, W. Song, X. Wang, F. Blaabjerg, and X. Feng, "Low-complexity model predictive control of single-phase three-level rectifiers with unbalanced load," *IEEE Trans. Power Electron.*, vol. 33, DOI 10.1109/TPEL.2017.2780160, no. 10, pp. 8936–8947, Oct. 2018.

- [20] S. Rivera, B. Wu, S. Kouro, V. Yaramasu, and J. Wang, "Electric vehicle charging station using a neutral point clamped converter with bipolar dc bus," *IEEE Trans. Ind. Electron.*, vol. 62, DOI 10.1109/TIE.2014.2348937, no. 4, pp. 1999–2009, Apr. 2015.

- [21] S. Rivera and B. Wu, "Electric vehicle charging station with an energy storage stage for split-dc bus voltage balancing," *IEEE Trans. Power Electron.*, vol. 32, DOI 10.1109/TPEL.2016.2568039, no. 3, pp. 2376–2386, Mar. 2017.

- [22] J. I. Leon, S. Kouro, L. G. Franquelo, J. Rodriguez, and B. Wu, "The essential role and the continuous evolution of modulation techniques for voltage-source inverters in the past, present, and future power electronics," *IEEE Trans. Ind. Electron.*, vol. 63, DOI 10.1109/TIE.2016.2519321, no. 5, pp. 2688–2701, May. 2016.

- [23] P. Acuña, L. Morán, M. Rivera, R. Aguilera, R. Burgos, and V. G. Agelidis, "A single-objective predictive control method for a multivariable single-phase three-level npc converter-based active power filter," *IEEE Trans. Ind. Electron.*, vol. 62, DOI 10.1109/TIE.2015.2393556, no. 7, pp. 4598–4607, Jul. 2015.

- [24] F. Sebaaly, H. Vahedi, H. Y. Kanaan, and K. Al-Haddad, "Novel current controller based on mpc with fixed switching frequency operation for a grid-tied inverter," *IEEE Trans. Ind. Electron.*, vol. 65, DOI 10.1109/TIE.2017.2784400, no. 8, pp. 6198–6205, Aug. 2018.

- [25] Y. Yang, H. Wen, M. Fan, M. Xie, R. Chen, and Y. Wang, "A constant switching frequency model predictive control without weighting factors for t-type single-phase three-level inverters," *IEEE Trans. Ind. Electron.*, vol. 66, DOI 10.1109/TIE.2018.2868290, no. 7, pp. 5153–5164, Jul. 2019.

- [26] R. Vargas, P. Cortes, U. Ammann, J. Rodriguez, and J. Pontt, "Predictive control of a three-phase neutral-point-clamped inverter," *IEEE Trans. Ind. Electron.*, vol. 54, DOI 10.1109/TIE.2007.899854, no. 5, pp. 2697– 2705, Oct. 2007.

- [27] C. A. Rojas, M. Aguirre, S. Kouro, T. Geyer, and E. Gutierrez, "Leakage current mitigation in photovoltaic string inverter using predictive control with fixed average switching frequency," *IEEE Trans. Ind. Electron.*, vol. 64, DOI 10.1109/TIE.2017.2708003, no. 12, pp. 9344–9354, Dec. 2017.

- [28] O. Machado, P. Martín, F. J. Rodríguez, and E. J. Bueno, "A neural network-based dynamic cost function for the implementation of a predictive current controller," *IEEE Trans. Ind. Informat.*, vol. 13, DOI 10.1109/TII.2017.2691461, no. 6, pp. 2946–2955, Dec. 2017.

- [29] R. C. Portillo, M. M. Prats, J. I. Leon, J. A. Sanchez, J. M. Carrasco, E. Galvan, and L. G. Franquelo, "Modeling strategy for back-to-back three-level converters applied to high-power wind turbines," *IEEE Trans. Ind. Electron.*, vol. 53, DOI 10.1109/TIE.2006.882025, no. 5, pp. 1483– 1491, Oct. 2006.

- [30] J. I. Leon, S. Kouro, S. Vazquez, R. Portillo, L. G. Franquelo, J. M. Carrasco, and J. Rodriguez, "Multidimensional modulation technique for cascaded multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 58, DOI 10.1109/TIE.2010.2048833, no. 2, pp. 412–420, Feb. 2011.

- [31] P. Karamanakos, T. Geyer, and R. Kennel, "On the choice of norm in finite control set model predictive control," *IEEE Trans. Power Electron.*, vol. 33, DOI 10.1109/TPEL.2017.2756092, no. 8, pp. 7105–7117, Aug. 2018.

- [32] T. Dragicevic, C. Zheng, J. Rodriguez, and F. Blaabjerg, "Robust quasipredictive control of lcl-filtered grid converters," *IEEE Transactions on Power Electronics*, DOI 10.1109/TPEL.2019.2916604, pp. 1–1, 2019.

- [33] P. Cortes, S. Kouro, B. La Rocca, R. Vargas, J. Rodriguez, J. I. Leon, S. Vazquez, and L. G. Franquelo, "Guidelines for weighting factors design in model predictive control of power converters and drives," in 2009 IEEE International Conference on Industrial Technology, DOI 10.1109/ICIT.2009.4939742, pp. 1–7, Feb. 2009.

- [34] T. Dragičević and M. Novak, "Weighting factor design in model predictive control of power electronic converters: An artificial neural network approach," *IEEE Trans. Ind. Electron.*, vol. 66, DOI 10.1109/TIE.2018.2875660, no. 11, pp. 8870–8880, Nov. 2019.

- [35] P. Acuna, R. P. Aguilera, A. M. Y. M. Ghias, M. Rivera, C. R. Baier, and V. G. Agelidis, "Cascade-free model predictive control for single-phase grid-connected power converters," *IEEE Trans. Ind. Electron.*, vol. 64, DOI 10.1109/TIE.2016.2599478, no. 1, pp. 285–294, Jan. 2017.

- [36] S. Vazquez, J. A. Sanchez, M. R. Reyes, J. I. Leon, and J. M. Carrasco, "Adaptive vectorial filter for grid synchronization of power converters under unbalanced and/or distorted grid conditions," *IEEE Trans. Ind. Electron.*, vol. 61, DOI 10.1109/TIE.2013.2258302, no. 3, pp. 1355– 1367, Mar. 2014.

**Sergio Vazquez** (S'04-M'08-SM'14) was born in Seville, Spain, in 1974. He received the M.S. and PhD degrees in industrial engineering from the University of Seville (US) in 2006, and 2010, respectively.

Since 2002, he is with the Power Electronics Group working in R&D projects. He is an Associate Professor with the Department of Electronic Engineering, US. His research interests include power electronics systems, modeling, modulation and control of power electronics con-

verters applied to renewable energy technologies.

Dr. Vazquez was recipient as coauthor of the 2012 Best Paper Award of the IEEE Transactions on Industrial Electronics and 2015 Best Paper Award of the IEEE Industrial Electronics Magazine. He is involved in the Energy Storage Technical Committee of the IEEE industrial electronics society and is currently serving as an Associate Editor of the IEEE Transactions on Industrial Electronics.

Pablo Acuna (M'12) received the B.Sc. degree in electronics engineering, the B.Eng. degree in electronics engineering, and the Ph.D. degree in electrical engineering from the University of Concepción, Concepción, Chile, in 2004, 2007, and 2013, respectively.

From 2014 to 2017, he was a Research Associate in the University of New South Wales, Australia. From 2018 to 2019, he was Lecturer in the School of Engineering, RMIT University, Melbourne, Australia.

He is currently a Lecturer in the Department of Electrical Engineering, Universidad de Talca, Chile. His research interests include electrical power conversion systems and their applications in industry, transportation, and utility.

Ricardo P. Aguilera (S'01-M'12) received the B.Sc. degree in electrical engineering from the Universidad de Antofagasta, Antofagasta, Chile; the M.Sc. degree in electronics engineering from the Universidad Tecnica Federico Santa Maria, Valparaíso, Chile; and the Ph.D. degree in electrical engineering from The University of Newcastle (UoN), Newcastle, NSW, Australia, in 2003, 2007, and 2012, respectively.

From 2012 to 2013, he was a Research Academic at UoN, where he was part of the Centre

for Complex Dynamic Systems and Control. From 2014 to 2016, he was a Senior Research Associate at The University of New South Wales, Australia, where he was part of the Australian Energy Research Institute. Since September 2016, he has been with the School of Electrical and Data Engineering, at the University of Technology Sydney, Australia, where he currently holds a Senior Lecturer position. His main research interests include theoretical and practical aspects on model predictive control with application to power electronics, renewable energy integration, and microgrids.

**Josep Pou** (S'97-M'03-SM'13-F'17) received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Technical University of Catalonia (UPC), in 1989, 1996, and 2002, respectively.

In 1990, he joined the faculty of UPC as an Assistant Professor, where he became an Associate Professor in 1993. From February 2013 to August 2016, he was a Professor with the University of New South Wales (UNSW), Sydney, Australia. He is currently a Professor with

the Nanyang Technological University (NTU), Singapore, where he is Program Director of Power Electronics at the Energy Research Institute at NTU (ERI@N) and co-Director of the Rolls-Royce at NTU Corporate Lab. From February 2001 to January 2002, and February 2005 to January 2006, he was a Researcher at the Center for Power Electronics Systems, Virginia Tech, Blacksburg. From January 2012 to January 2013, he was a Visiting Professor at the Australian Energy Research Institute, UNSW, Sydney. He has authored more than 300 published technical papers and has been involved in several industrial projects and educational programs in the fields of power electronics and systems. His research interests include modulation and control of power converters, multilevel converters, renewable energy, energy storage, power quality, HVDC transmission systems, and more-electrical aircraft and vessels.

He is co-Editor-in-Chief of the IEEE Transactions on Industrial Electronics and Associate Editor of the IEEE Journal of Emerging and Selected Topics in Power Electronics. He received the 2018 IEEE Bimal Bose Award for Industrial Electronics Applications in Energy Systems.

Jose I. Leon (S'04-M'07-SM'14-F'17) was born in Cadiz, Spain. He received the B.S. and M.S. and PhD degrees in telecommunications engineering from Universidad de Sevilla (US), Spain, in 1999, 2001 and 2006 respectively.

Currently, he is an Associate Professor at University of Seville (Spain) and a Visiting Professor at Harbin Institute of Technology (China) as part of the short term 1000 talents program. His research interests include modulation and control of power converters for high-power applications

and renewable energy systems.

Dr. Leon was recipient as co-author of the 2008 Best Paper Award of the IEEE Industrial Electronics Magazine, the 2012 Best Paper Award of the IEEE Transactions on Industrial Electronics, and the 2015 Best Paper Award of the IEEE Industrial Electronics Magazine. He was the recipient of the 2014 IEEE J. David Irwin Industrial Electronics Society Early Career Award and the 2017 IEEE Bimal K. Bose Energy Systems Award. He is currently serving as an Associate Editor of the IEEE Transactions on Industrial Electronics.

**Leopoldo G. Franquelo** (M'84-SM'96-F'05) received the M.Sc. and Ph.D. degrees in electrical engineering from the Universidad de Sevilla, Spain, in 1977 and 1980,

He was associate professor at Universidad de Sevilla from 1982-86 and is full professor since 1986. Also, he is a 1000 Talent Professor at the Department of Control Science and Engineering in Harbin Institute of Technology (China) since 2016. His current research interests include modulation techniques for multilevel

inverters and power electronic systems for renewable energy systems. He has participated in more than 100 Industrial and R&D projects and has published more than 300 papers, 84 of them in IEEE Journals.

Dr. Franquelo is an Industrial Electronics Society Distinguished Lecturer since 2006. In the IEEE Trans. on Ind. Electronics, he became an Associate Editor in 2007, Co-EiC in 2014, and the EiC since 2016. He was a Member-at-Large of the IES AdCom (2002-2003) and Vice President for Conferences (2004- 2007). He was the President of the IES (2010-2011) and is an IES AdCom Life member. In 2009 and 2013, he received the Andalusian Research Award and FAMA Award recognizing the excellence of his research career. He has received a number of Best Paper Awards from IEEE journals. He was the recipient of the Eugene Mittelmann Outstanding Research Achievement Award and the Antohny J. Hornfeck Service Award from IEEE-IES, in 2012 and 2015 respectively.