# Analysis and Modeling of Thermal Coupling Effect Between Power Semiconductor Devices

#### by Kaixin Wei

Thesis submitted in fulfilment of the requirements for the degree of

# **Doctor of Philosophy**

under the supervision of Dylan Dah-Chuan Lu

University of Technology Sydney Faculty of Engineering and IT

July 2020

Certificate of original authorship

I, Kaixin Wei declare that this thesis, is submitted in fulfilment of the requirements for

the award of Doctor of Philosophy, in the Faculty of Engineering and IT at the University

of Technology Sydney.

This thesis is wholly my own work unless otherwise referenced or acknowledged. In

addition, I certify that all information sources and literature used are indicated in the thesis.

This document has not been submitted for qualifications at any other academic institution.

This research is supported by the Australian Government Research Training Program.

**Production Note:**

Signature: Signature removed prior to publication.

Date: 09/07/2020

# Acknowledgment

I would like to express my gratitude to all those who helped me during the journey of my Ph. D study. I gratefully acknowledge the help of my supervisor Prof. Dr. Dylan Lu, for all the support and encouragement he provided to me during my entire Ph. D program. My first journal paper almost took one year from submission to acceptance, and it is him to help me revise more than ten drafts. His constant guidance has walked me through all the stages of my Ph. D study. Under his unselfish guidance, I am growing up to not only an eligible Ph. D student but a person of courage and honesty in life.

I would also like to extend my sincere gratitude to my co-supervisor, Dr. Yam P. Siwakoti, for his instructive advice and useful suggestions on my research progress. He is knowledgeable and always keeps patient for my sudden visit to his office. His timely feedbacks really have helped me a lot.

I also owe a special debt of gratitude to all my good friends and colleagues in my team. They shared happiness with me in daily life and enlightening brainstorming in study which I have benefited a lot.

I really appreciate the love and care of my family. Thanks to my parents for their support and help in my study and life over the years. Thanks to my wife for her tolerant and understanding which make me study abroad at ease. Thanks to my baby for his coming to make me full of energy.

I would like to express my sincere thanks to all the people who have been supporting me, understanding me, and encouraging me. To express my inner gratitude, I borrow a few sentences from a song called "raise me up":

You raise me up, so I can stand on mountains.

You raise me up, to walk on stormy seas.

I am strong, when I am on your shoulders.

You raise me up, to more than I can be.

Finally, I would like to express my heartfelt thanks to all the experts and scholars who have worked hard for the paper review.

Kaixin Wei September 2019 in Sydney

#### List of Publications

#### Journal papers

- J-1. **K. Wei**, D.D.C Lu, C. Zhang, Yam P. Siwakoti, et al. Modeling and Analysis of Thermal Resistances and Thermal Coupling Between Power Devices[J]. IEEE Transactions on Electron Devices,2019,66(10):4302-4308. (**SCI, IF 2.704**)

- J-2. **K. Wei**, C. Zhang, Yam P. Siwakoti, et al. Multi-Variable Thermal Modeling of Power Devices Considering Mutual Coupling[J]. Applied Sciences,2019,9(16): 3240-3243. (**SCI**, **IF 2.217**)

- J-3. **K. Wei**, D.D.C Lu, Yam P. Siwakoti, et al. Electro-thermal Modeling Considering Ambient Temperature and Convection Coupling[J]. Applied Sciences.(**Under review**, **SCI**, **IF 2.704**)

- J-4. **K. Wei**, C. Zhang, et al. Thermal Coupling Modeling for Multi-Chip Paralleled IGBT Modules Based on the Thermal Resistance Network Method[J]. Journal of Beijing Institute of Technology, 2017,26(1):147-152.

- J-5. **K. Wei**, C. Zhang, et al. The IGBT Losses Analysis and Calculation of Inverter for Two-seat Electric Aircraft Application[J]. Energy Procedia, 2017, 105:2623-2628

#### **Conference** papers

- C-1. **K. Wei**, C. Zhang, et al. A Thermal Coupling Model Based on the Thermal Resistance Network Method for Paralleled IGBT Modules[C]. ISEV, 2017.

- C-2. **K. Wei**, C. Zhang, et al. An Electric-thermal Model Calculating Losses and Junction Temperature for Paralleled IGBT Modules in an Inverter Application[C]. ICMEE, 2017.

# Contents

| Certificate of original authorship                                 | i   |

|--------------------------------------------------------------------|-----|

| Acknowledgment                                                     | ii  |

| List of Publications                                               | iii |

| Contents                                                           | I   |

| Abstract                                                           | VI  |

| Chapter 1 Introductions                                            | 1   |

| 1.1 Background and significance                                    | 1   |

| 1.2 Outline                                                        | 5   |

| Chapter 2 Thermal Transfer Mechanism and Literature Review         | 8   |

| 2.1 Thermal Transfer Mechanism for Power Devices                   | 8   |

| 2.1.1 Thermal Transfer Modes                                       | 8   |

| 2.1.2 Thermal transfer process                                     | 9   |

| 2.2 Research status of thermal analysis modeling for power devices | 10  |

| 2.2.1 Finite Element Method (FEM) models                           | 11  |

| 2.2.2 Thermal resistance network models                            | 12  |

| 2.2.3 <i>R<sub>ca</sub></i> and Ambient Temperatures               | 20  |

| 2.3 Research Gap/Problems                                          | 21  |

| Chapter 3 Modeling and Analysis of Thermal Resistances and Thermal Coupling                |

|--------------------------------------------------------------------------------------------|

| Between Power Devices23                                                                    |

| 3.1 Single testing analysis of power devices                                               |

| 3.1.1 Relationships between $T_c$ and $T_j$                                                |

| 3.1.2 Single testing of power devices                                                      |

| 3.1.3 Losses calculation                                                                   |

| 3.2 Thermal Coupling Experiments and Requirements of Temperature Control for               |

| Power Converter Systems                                                                    |

| 3.2.1 Thermal Coupling Experiments                                                         |

| 3.2.2 Temperature Controling Requirements of Power Converter System 33                     |

| 3.3 Thermal Coupling Testing Analysis of Power Devices                                     |

| 3.3.1 Thermal Coupling Testing of Adjacent Devices                                         |

| 3.3.2 Calculation of Self-thermal Resistance                                               |

| 3.3.3 Analysis of Variable Thermal Resistances                                             |

| 3.4 Thermal Coupling Resistances Network (TCRN) Modeling for Power Devices 44              |

| 3.4.1 TCRN Modeling                                                                        |

| 3.4.2 Analysis of Key Influencing Factors                                                  |

| 3.4.3 Losses of Power Devices                                                              |

| 3.5 Relationships Between Thermal Resistances and Analysis of the Thermal Coupling  Effect |

| 3.5.1 Analysis of Thermal Coupling Effect Under Different Working Conditions               |

| 3.5.2 The Relationships at Different Spacing                               |

|----------------------------------------------------------------------------|

| 3.5.3 The Relationships with Different Operating Currents                  |

| 3.5.4 The Steady-state $T_c$ Calculation                                   |

| 3.6 Experimental Verification                                              |

| 3.6.1 The Steady-state $T_c$ Calculation                                   |

| 3.6.2 TCRN Model and Relationships Verification                            |

| 3.7 Conclusions65                                                          |

| Chapter 4 Research on Convection Thermal Coupling Between Power Devices 67 |

| 4.1 Thermal Convection Testing Analysis of Power Devices                   |

| 4.1.1 Thermal Convection Testing of Devices                                |

| 4.1.2 Analysis of the Convection Thermal Coupling                          |

| 4.1.3 The Experimental Platform for MOSFET and Diode                       |

| 4.2 Multi-Variable Thermal Resistances Network Modeling                    |

| 4.2.1 Thermal Resistances Network                                          |

| 4.2.2 Self-Resistances Calculation                                         |

| 4.2.3 Thermal Coupling Resistances Calculation                             |

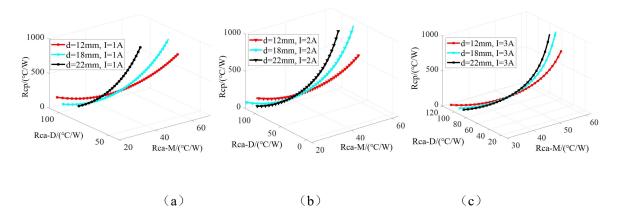

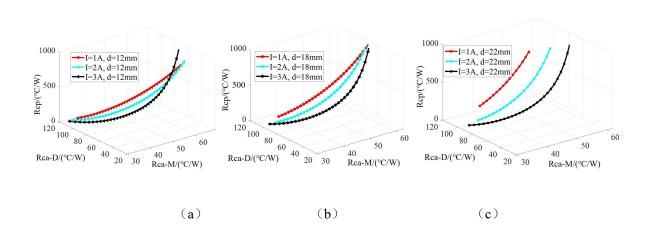

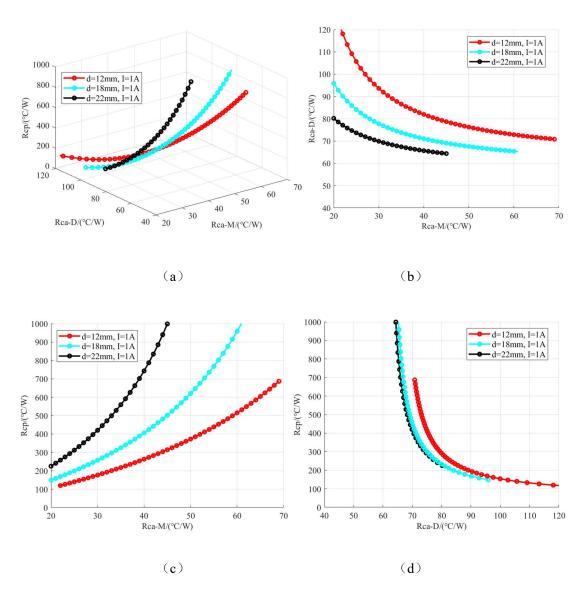

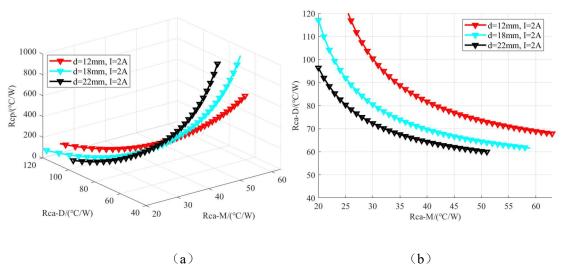

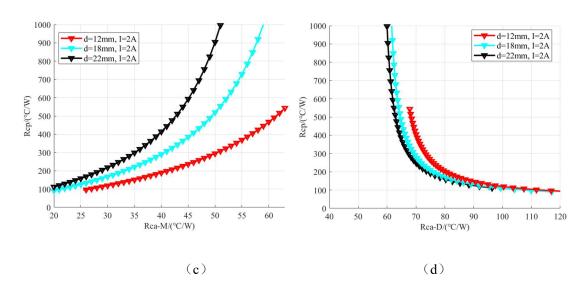

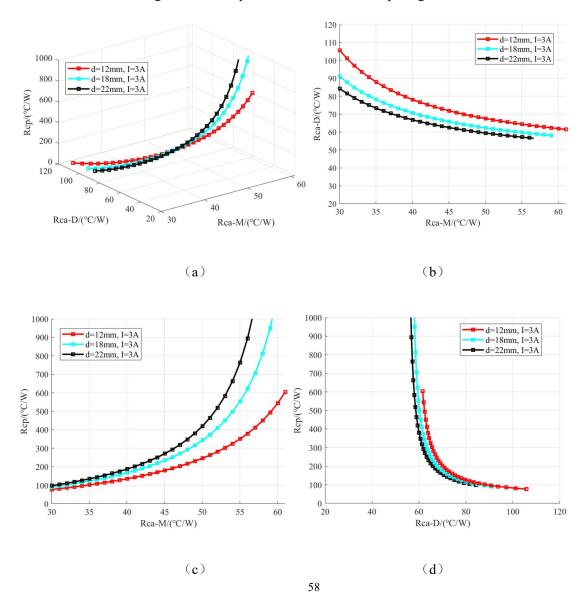

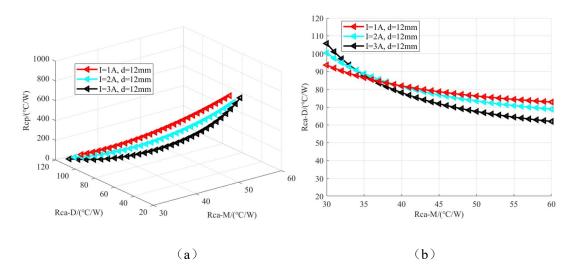

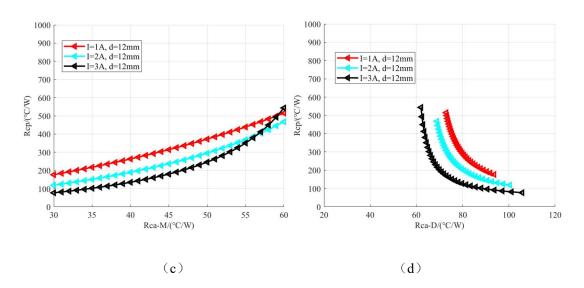

| 4.2.4 Relationships between $R_{cp}$ and the impact factors                |

| 4.2.5 <i>R<sub>cp</sub></i> Calculation79                                  |

| 4.3 Verifications                                                          |

| 4.4 Conclusions81                                                          |

| <b>Chapter 5 Thermal Analysis and Junction Temperature Calculation under Different</b> |

|----------------------------------------------------------------------------------------|

| Ambient Temperatures Considering Convection Thermal Coupling 82                        |

| 5.1 Ambient Temperatures                                                               |

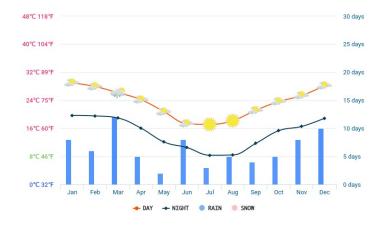

| 5.1.1 Ambient Temperatures Domain                                                      |

| 5.1.2 Analysis and Selection of the Ambient Temperatures                               |

| 5.2 Convection Thermal Coupling Modeling of Adjacent Devices                           |

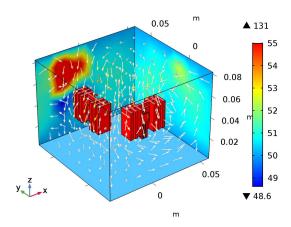

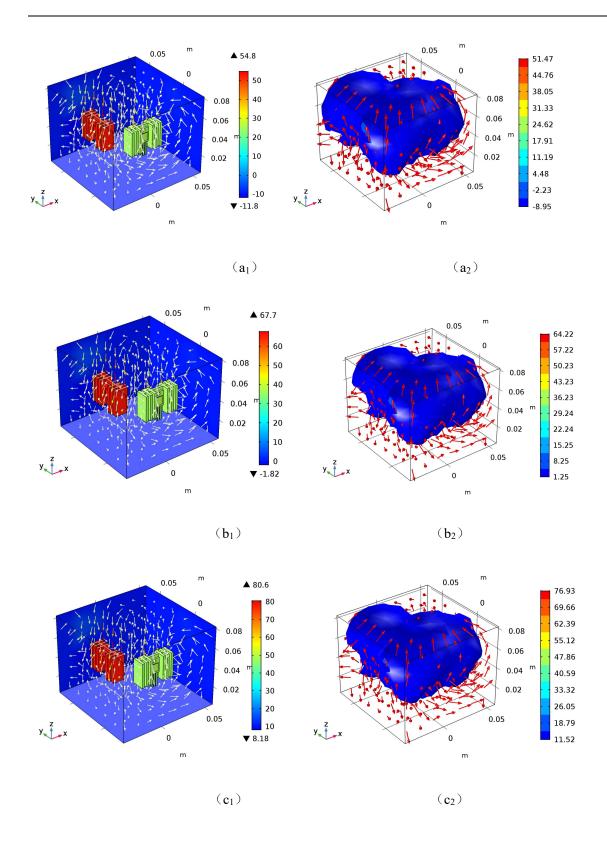

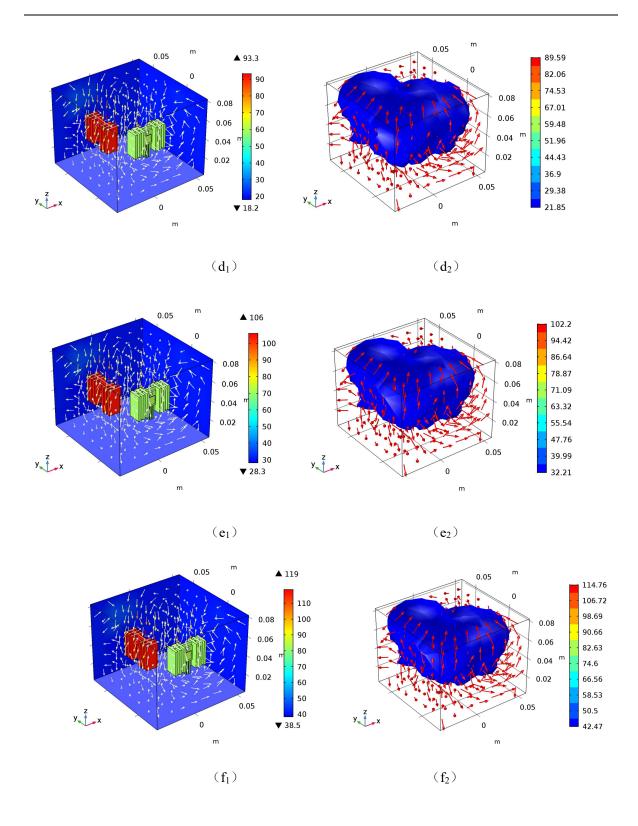

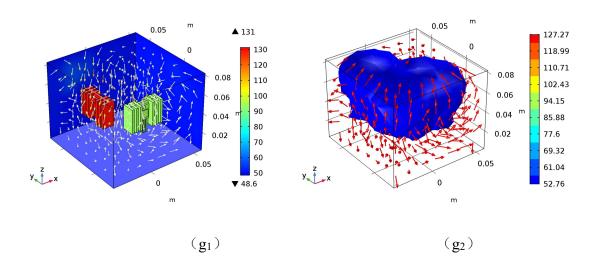

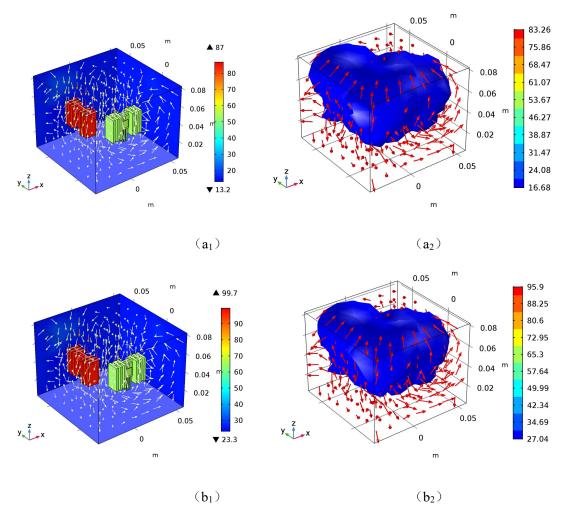

| 5.2.1 FEM Modeling85                                                                   |

| 5.2.2 Convection Thermal Coupling Simulation and Junction Temperature Calculation      |

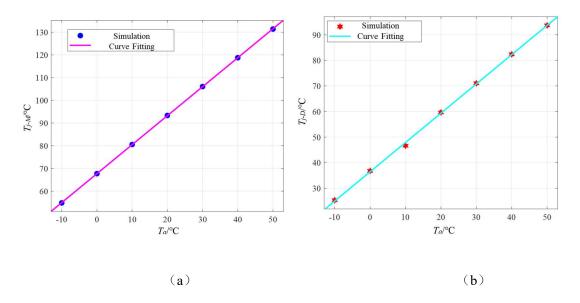

| 5.2.3 The Relationships Between Junction Temperature and Ambient                       |

| Temperatures                                                                           |

| 5.3 Modeling Verification                                                              |

| 5.3.1 The Simulation Analysis Under New Temperature Profile                            |

| 5.3.2 Junction Temperature Calculation and Comparisons                                 |

| 5.4 Conclusions                                                                        |

| Chapter 6 Modeling Analysis of Conduction Thermal Coupling Between IGBT  Modules       |

| Wiodules                                                                               |

| 6.1 Analysis of Conduction Thermal Coupling Effect                                     |

| 6.1.1 Analysis of Conduction Thermal Coupling Between IGBT Modules 94                  |

| 6.1.2 FEM Analysis of IGBT Modules95                                                   |

| 6.1.3 Electro-thermal Coupling Simulation Analysis of Power Converter System           |

| 6.2 Modeling of Thermal Conduction Coupling Between Power Modules 101     |

|---------------------------------------------------------------------------|

| 6.2.1 Conduction Thermal Coupling Effect Between Power Modules 101        |

| 6.2.2 Conduction Thermal Coupling Modeling Between Adjacent IGBT Modules  |

|                                                                           |

| 6.2.3 Calculation of Conduction Thermal Coupling Resistances and Junction |

| Temperature                                                               |

| 6.3 Model Validation                                                      |

| 6.4 Conclusions                                                           |

| Chapter 7 Conclusions and Future Work109                                  |

| 7.1 Conclusions                                                           |

| 7.2 Contributions                                                         |

| 7.3 Future Work                                                           |

| Bibliography113                                                           |

#### **Abstract**

Power semiconductor devices, which are mainly used in power converters such as buck and boost converters and inverters, are the core part of energy transformation and transmission and they are widely used in electric vehicle applications. The recent trend in the design of the high-power density power converters generally reduces the rate of the devices cooling process. As a result, an increased thermal coupling among devices increases the overall power supply temperature, and the uneven temperature distribution of the devices, which negatively affects the performance and lifespan of semiconductor devices and power converters. Traditional thermal models do not consider the changes of self-thermal resistances and also ignore the effect of thermal coupling among the adjacent devices. Compared with these models, the proposed thermal resistances modeling approaches provide better understanding of the thermal behavior of power devices.

The uneven case temperature distribution of the devices in the converter system increases the thermal coupling effect between adjacent devices and thermal stress concentration. In the design stage, considering the demand of power converter system for the case temperature control of the devices, a calculation method of thermal coupling effect is proposed based on the thermal coupling experiment platform for power devices. The thermal coupling effect between adjacent devices under different working conditions can be obtained by building a thermal coupling resistances network (TCRN) model and analyzing the relationships between the self-resistance and the thermal coupling resistances between adjacent devices. Finally, a new thermal coupling testing platform is established with a different device spacing, and the results are compared with the derived TCRN model. The comparisons show that the calculation method of the thermal coupling effect proposed is feasible and effective.

In order to analyze the convection thermal coupling effect between adjacent power devices, a convection thermal coupling testing platform for devices is established, and a multi-variable thermal resistances network model is proposed. Thermal coupling resistances

under different working conditions can be calculated by the proposed network. In addition, the relationships between the thermal coupling resistances and their influence factors are also analyzed. Finally, the model is validated by establishing a new coupling testing platform with a new device spacing.

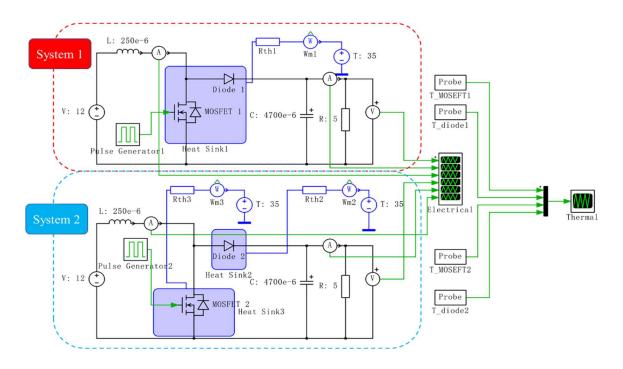

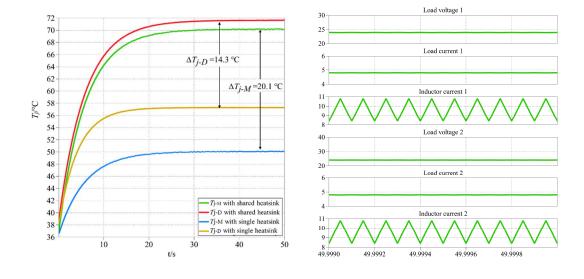

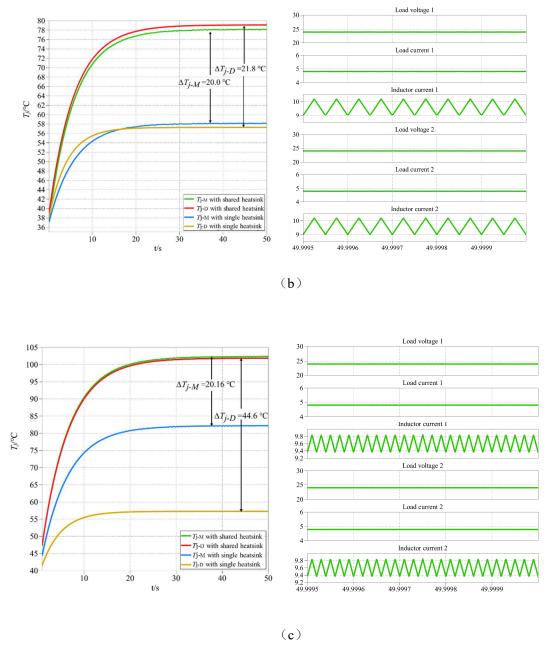

In order to analyze the conduction thermal coupling effect between the neighboring modules/devices, FEM and PLECS simulations are established for power converter systems. Based on the above analysis, the calculation model of conduction thermal coupling of adjacent power modules is established, and the junction temperature of the power module is calculated. Finally, the model is validated by an online simulation software provided by Infineon Technologies.

Key Words: power converter; semiconductor devices; thermal coupling effect; thermal network; thermal coupling resistances

# Chapter 1 Introductions

#### 1.1 Background and significance

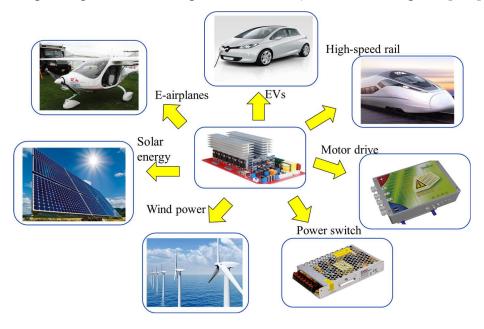

The power semiconductor devices used for voltage conversion, rectification and inversionis the core part of energy conversion and transmission in power electronic equipment, which is widely used in electrical appliances and electric vehicles [1, 2]. In recent years, power electronic applications are growing continuously, and their performance has strong correlation to national economy, such as transportation, aerospace, and renewable energy (wind power generation, solar photovoltaic, etc.), as shown in Fig. 1.1 [3, 4].

Fig. 1.1. Applications of power semiconductor devices.

According to the report on the current situation of power electronics industry in 2016-2019 [5], the power converter in the vehicles market, including electric vehicles (EV) and hybrid electric vehicles (HEV) and other new energy vehicles, increased by more than 20% in 2016. In 2017, the scale of semiconductor devices in the electric vehicle market is US \$4.41 billion, which is expected to reach US \$5.49 billion by 2022. According to statistics, the compound annual growth rate from 2017 to 2022 is 4.48%. In 2018, the share of power converters in the power electronics market is US \$53.4 billion, and that of power

semiconductor devices is US \$17.5 billion. According to the latest EV/HEV power converters market analysis in 2019, the growth rate expected to be as high as 20.7% from 2018 to 2024 [6].

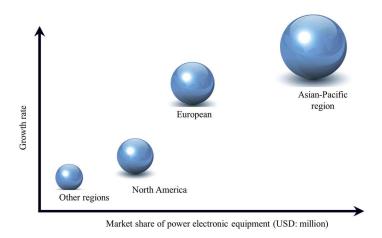

The power electronic equipments play important roles in motor drive and power control of general transportation industry such as power converter. The power electronics industry occupies an important position in the world. In the 2023 world semiconductor market forecast analysis, as shown in Fig. 1.2, the Asia Pacific region dominates the power electronics market, followed by Europe and North America [5]. Due to the increasingly serious energy and environmental problems, the energy-saving and new energy automobile industry will be vigorously promoted, so as to promote the development of power electronic equipment industry.

Fig. 1.2: Market share prediction of power electronic equipment in 2023.

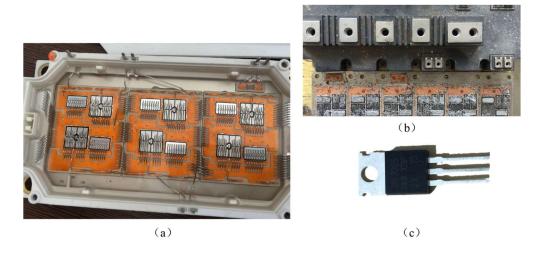

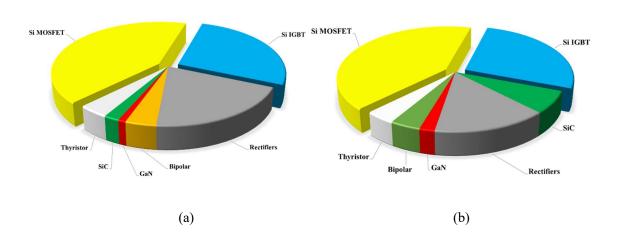

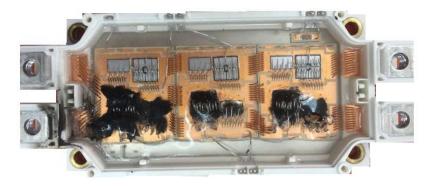

According to the materials of semiconductors, the power semiconductor devices can be divided into traditional silicon-based semiconductor devices, such as IGBT (insulated gate bipolar transistor) power module, MOSFET (metal oxide semiconductor field effect transistor), diodes and new wide band gap semiconducting devices, such as silicon carbide (SiC) and gallium nitride (GaN) based devices [7, 8]. In power converters for electric vehicles, IGBT modules and MOSFETs, as shown in Fig. 1.3, are mainly used. IGBT power modules are generally used in the field of medium and high voltage (high-power applications), and MOSFET are generally used in the field of medium and low-voltage (medium and small

power). The market share distribution of different power electronic devices is shown in Fig. 1.4 [9]. By comparison, in the market share of semiconductor devices in 2018 and 2024, power devices dominated by traditional silicon based MOSFETs and IGBT modules are still in the dominant positions and are developing rapidly and the share of the new wide band gap semiconductor devices has increased. As higher power density and integration are the main demands and goals pursued by power products, it is estimated that in 2022, semiconductor devices will boost the market share of power electronics to 35 billion US dollars [5].

Fig. 1.3: Power devices/modules: (a) 600A FF600R06ME3 IGBT module; (b) 1400A-

FF1400R17IP4 IGBTmodule; (c) 33A-IRF540N MOSFET.

Fig. 1.4: Power devices market share (a) in the year of 2018; (b) prediction in the year of 2024

With the increasing power density of semiconductor devices and the increasing design requirements of compact power converters, the reliability of semiconductor devices and power converter systems has been widely concerned. In the application of power converters, semiconductor devices are an important factor affecting the reliability of power electronic equipments such as power converters [10]. The main causes of electrical failure of power electronic equipment such as semiconductor devices and power converters are temperature, humidity, mechanical vibration, dust, overvoltage, over-current, etc. [11, 12]. According to the statistics of avionics equipment, 20% of the on-site faults are caused by thermal. When the working junction temperature of power electronic devices exceeds the maximum allowable junction temperature, thermal failure of devices will occur, as shown in Fig. 1.5.

Fig. 1.5: Burned IGBT module [13, 14].

The thermal analysis calculation models [15] can be used to describe the transient or steady-state thermal distribution to ensure that the device temperature is lower than the maximum junction temperature and at the same time to make it working in a good temperature operating range [16]. The temperature of the transient thermal analysis model changes with time, which is mainly used to calculate the temperature of the model in a specific time range. The steady-state thermal analysis model mainly analyzes the influence of stable thermal on the system or components, which can be used to analyze the temperature distribution under different working conditions. Both transient and steady-state thermal analysis have their applications and research significance [17]. By establishing the corresponding thermal analysis models, not only can help the thermal distribution of the system be better analyzed, but also assist the structure optimization of the converter system.

In the application of power converters, with the improvement of power density, higher current density leads to thermal concentration of power devices, and the non-uniformity of case temperature distribution of multiple power devices in power converter which is easy to cause thermal stress concentration [18]. At the same time, the demand of high power density of the power converters, its package volume gradually decreases, which makes the space between multiple power devices compact, thus causing thermal coupling effect between multiple power modules or devices, which greatly reduces the operation reliability of the module/device itself and the converter system.

In order to solve the above problems, based on the devices and system testing platforms and the traditional thermal analysis models of power devices, this paper studies the conduction and convection thermal coupling effect between adjacent devices, and establishes the thermal coupling resistance network models, to analyze the relationships between self-thermal resistance and thermal coupling resistances, which have signaficange for power converter design, structure optimization, and system reliability.

#### 1.2 Outline

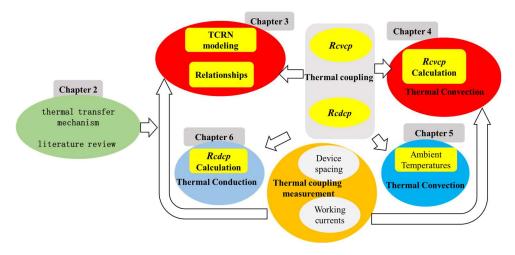

An overview of the power devices and power converters and their required thermal models are stated in the previous sections. According to the literature survey, there is a space to improve the proposed thermal models. The organization of this thesis is listed as follows, as shown in Fig. 1.6:

Fig. 1.6: The organization of the thesis.

In Chapter 2, thermal transfer mechanism and literature review are present which includes the thermal analysis modeling for power devices and the existing gap.

In Chapter 3, the TCRN model which considers the conduction and convection thermal coupling has been proposed for the adjacent power devices and the relationships between the thermal resistances are given.

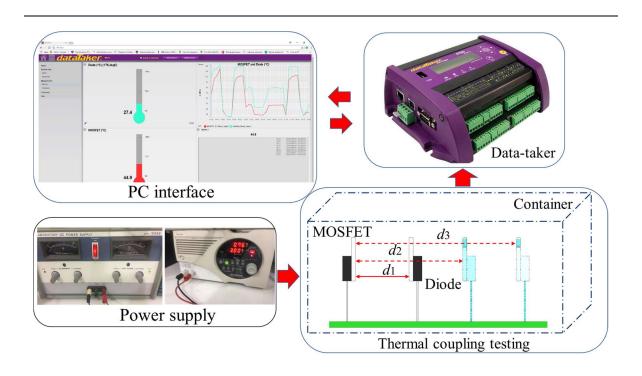

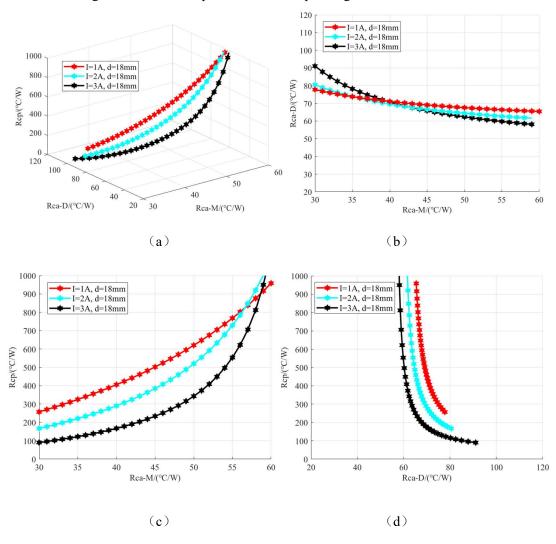

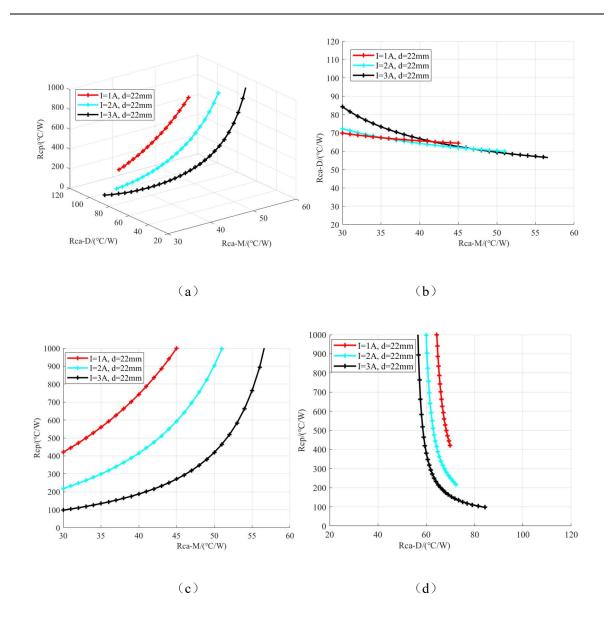

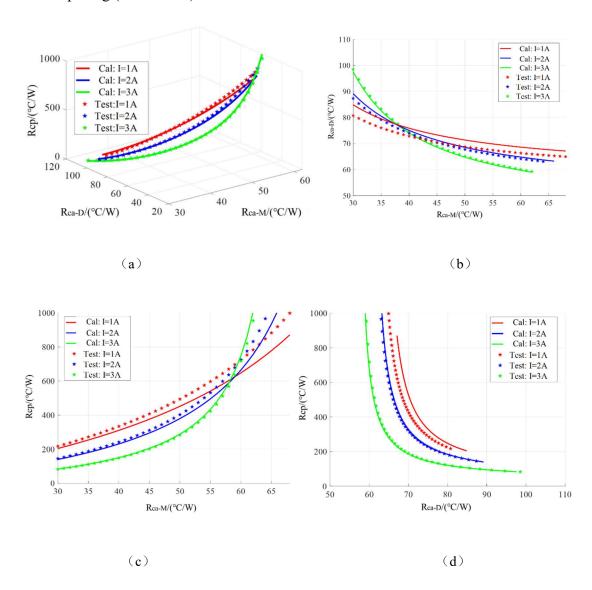

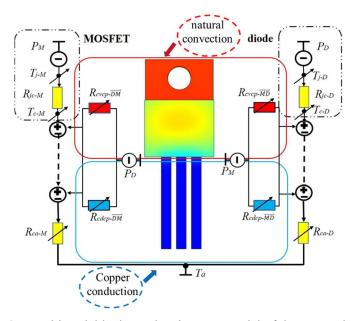

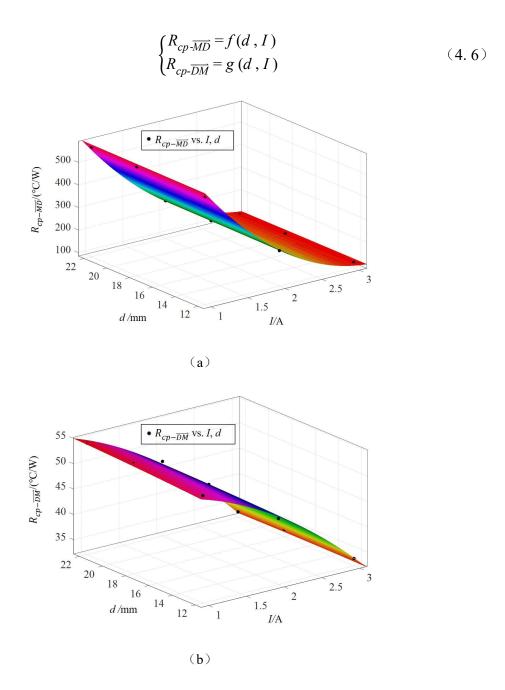

In Chapter 4, in order to further analyze the convection thermal coupling effect, thermal analysis and testing platform of power device is established in this chapter. By changing the working conditions, the influencing factors of convective thermal dissipation under different device spacing are analyzed. In addition, in order to better analyze the convective thermal coupling effect between devices, a single test platform for semiconductor devices (MOSFET and diode) and a convective thermal coupling test platform are established. By changing the device spacing and load current, the device case temperature under different working conditions is obtained. Based on the analysis of the thermal coupling effect in Chapter 3, a multi-variable thermal resistance network model is established considering the convection thermal coupling between power devices. The thermal coupling resistance between devices is calculated, and the relationships between the coupling thermal resistance and the influencing factors (device spacing and load current) are analyzed. Finally, a new convection thermal coupling testing platform under new device spacing is established to verify the proposed thermal model by the comparison results of the thermal coupling resistance values.

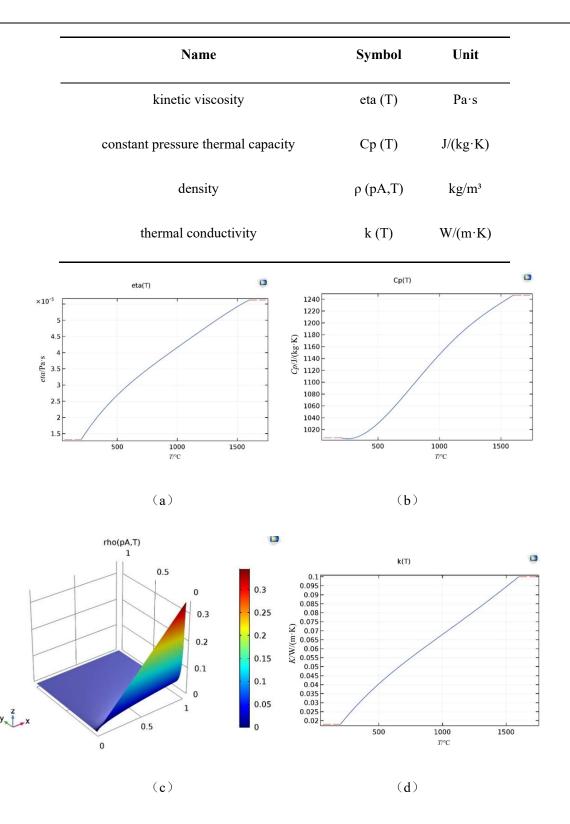

The convection thermal coupling between adjacent power devices is dependent on the ambient temperature, while the existing thermal analysis models are often based on a fixed ambient temperature. When the ambient temperature changes, convection thermal coupling also changes. This results in an inaccurate model that causes errors in the prediction of the thermal distribution and junction temperature for power devices. To solve this variable ambient temperate related issue, in Chapter 5, FEM (Finite Element Method) [19, 20] models for semiconductor power devices (MOSFET and diode) considering convection thermal coupling are established. Through these simulations, the junction temperatures of devices

under different ambient temperatures are obtained, and the relationships between junction temperature and ambient temperatures are established. Moreover, the junction temperatures of power devices under different ambient temperatures are calculated and temperature distribution is analyzed in this paper. This method shows the strong significance and has potential applications for high-efficient and high-power density converter design.

In Chapter 6, conduction thermal coupling model has been proposed based on the IGBT modules application.

Finally, a conclusion summary and suggestions for future works are presented in Chapter 7.

# Chapter 2 Thermal Transfer Mechanism and Literature Review

#### 2.1 Thermal Transfer Mechanism for Power Devices

The main forms of thermal transfer are thermal conduction, thermal convection, and thermal radiation [3, 21], and the mechanism diagram is shown in Fig. 2.1. In power applications, such as the power converters/inverters, there are many forms of thermal transfer at the same time [10, 22]. The semiconductor devices are important factors affecting the reliability of the power converter system and one of the main failure factors for power converters is the thermal failure caused by the process of thermal generation and transfer, as discussed in Section 1.1. Therefore, it is important to fully understand the thermal transfer theory, and establish corresponding thermal models for the reliability and structural optimization of the devices and systems.

Fig. 2.1: Thermal Transfer.

#### 2.1.1 Thermal Transfer Modes

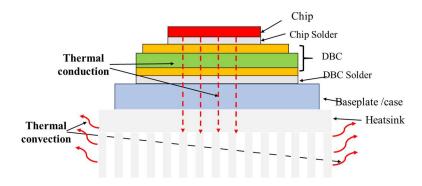

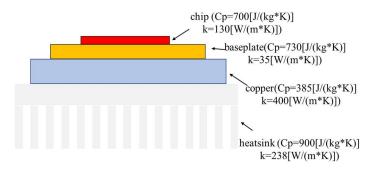

Thermal conduction is a phenomenon of thermal transfer caused by the thermal movement of micro particles (there is no macroscopic motion in the medium) [3]. The thermal transfers from the chip to the DBC layer, the copper substrate, and then the heatsink and finally to the ambient surroundings. Thermal convection refers to the relative displacement of fluids (liquid, gas, etc.) at different temperatures due to macroscopic motion

[3]. Thermal convection is caused by the density difference between the cold and hot fluids. When the thermal is transferred from the case/ baseplate of the semiconductor devices or through the heatsink to the surrounding air, and the form of thermal transfer is becoming into the thermal convection. Thermal radiation refers to the phenomenon that an object radiates electromagnetic waves due to its temperature [23].

#### 2.1.2 Thermal transfer process

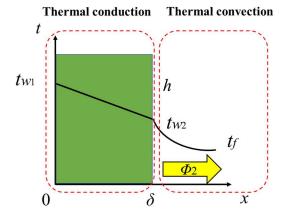

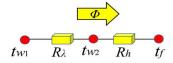

The thermal transfer process refers to the process that the thermal is transferred from the interior of the solid to the other side of the fluid through the solid wall, that is, the thermal transfers from the heating solid (chip) to the surrounding air, as shown in Fig. 2.2. In the figure,  $t_{w1}$ ,  $t_{w2}$ ,  $t_f$  are the temperatures and h is the convection coefficient. It is assumed that  $t_{w1}$ ,  $t_{w2}$ ,  $t_f$  and h do not change with time and  $\lambda$  is a constant [3].

Fig. 2.2: Thermal transfer.

The thermal conduction equation of flat wall can be obtained based on the steady state thermal transfer

$$\phi_1 = A\lambda \frac{t_{w1} - t_{w2}}{\delta} = \frac{t_{w1} - t_{w2}}{\frac{\delta}{A\lambda}} = \frac{t_{w1} - t_{w2}}{R_{\lambda}}$$

(2.1)

And the thermal convection equation can be expressed as

$$\emptyset_2 = A h_2 \frac{t_{w2} - t_f}{\delta} = \frac{t_{w2} - t_f}{\frac{1}{Ah}} = \frac{t_{w2} - t_f}{R_h}$$

(2.2)

When the thermal transfer reaches a steady state, it can be obtained by energy conservation

$$\emptyset = \emptyset_1 = \emptyset_2 \tag{2.3}$$

that is

$$\begin{cases}

\emptyset = \frac{t_{w1} - t_f}{\frac{\delta}{A\lambda} + \frac{1}{Ah}} = \frac{t_{w1} - t_f}{R_{\lambda} + R_h} = \frac{t_{w1} - t_f}{R_k} \\

R_k = R_{\lambda} + R_h

\end{cases} (2.4)$$

where  $R_k$  is the total thermal transfer resistance,  $R_{\lambda}$  is conduction thermal resistance and  $R_h$  is convection thermal resistance.

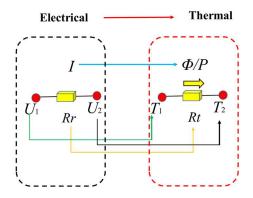

Fig. 2.3: The theory of electrical to thermal.

Based on the theory of electrical to thermal, as shown in Fig. 2.3: the resistance corresponds to the thermal resistance; the voltage difference corresponds to the temperature difference and the current corresponds to the power loss. The corresponding thermal resistance network in the thermal transfer process is shown in Fig. 2.4.

Fig. 2.4: Thermal resistance network.

# 2.2 Research status of thermal analysis modeling for power devices

For industrial applications, reliability, cost and power density are important considerations in the design of power converters. The increase of power density requires

efficient and intelligent thermal design and thermal management [24, 25] to ensure the reliability of the converter system [26, 27]. Based on the analysis in Section 1.1, a large proportion of the main failure in semiconductor devices and their power converters are temperature related, and the change of temperature may lead to bond wire shedding, welding fatigue crack, power chip breakdown, etc. [28]. For high power density [29] and compact power converters [30], the thermal dissipation of power devices slows down with the decrease of device spacing, thus making the overall temperature of devices and systems higher.

#### 2.2.1 Finite Element Method (FEM) models

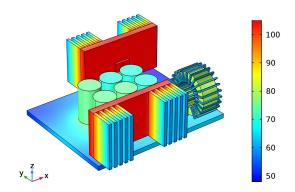

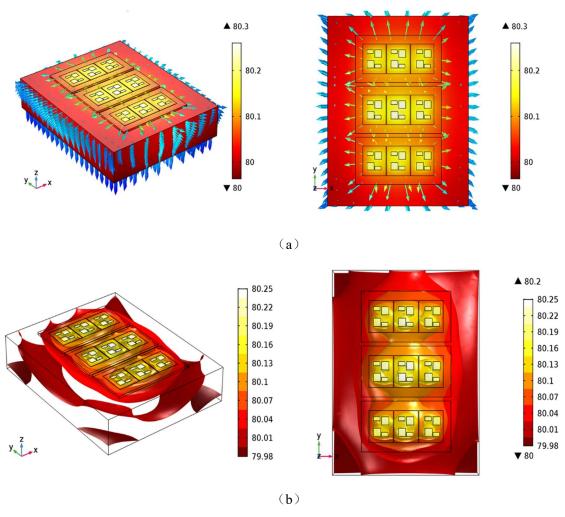

As shown in Fig. 2.5, different colors represent different temperature distributions. Thermal dissipation has a negative impact on the performance and lifetime of semiconductor devices and power converters.

Fig. 2.5: Temperature distributions of a power converter.

Therefore, thermal analysis modeling under different load conditions is essential, and it is necessary to seek the temperature calculation methods of power converters and the optimal distribution schemes of thermal distribution. As the size of a single traditional silicon-based device approaches its basic limit [31], a better understanding of the thermal distribution of adjacent devices under different operating conditions can help the system carry out reasonable thermal management, thus improving the performance of the converter system, and optimizing the overall structure of the converter [32]. The accuracy of the thermal

analysis model has a significant impact on the thermal management and reliability of devices and systems.

For semiconductor devices and power converter systems, the commonly used thermal modeling methods mainly include physical model calculation method, numerical calculation method, finite element method (FEM), thermal resistance network method, etc. [33, 34]. FEM can be used for thermal calculation of devices or power converter systems, and the simulated structures can be simplified within the range of accuracy allowed. The FEM results can be used to analyze the temperature distribution directly by different colors, and the junction/case temperature can be extracted by adding virtual thermal probes to the corresponding components. Unlike the real probes or temperature sensors, the virtual probes are considered to have absolutely ideal thermal conductivity and insulation properties, which can be attached to the device surface or injected inside the devices, or anywhere in the air region [35].

However, it has difficulties when using FEM to establish thermal models for the semiconductor devices, because you should be familiar with the specific parameters of internal structures for power devices or modules. The FEM analysis needs 3D modeling of the devices or systems. Although the structures can be simplified, the structures of the devices and systems need to be better understood. In addition, in order to build a more accurate FEM analysis model, in addition to being familiar with the geometric structure of devices/modules and the relative positions of multiple devices in the system, reasonable meshing and boundary conditions setting are also essential [36], then the speed of FEM simulation will be generally slow [37]. In this paper, the FEM method is used to analyze the convection thermal coupling of adjacent semiconductor devices.

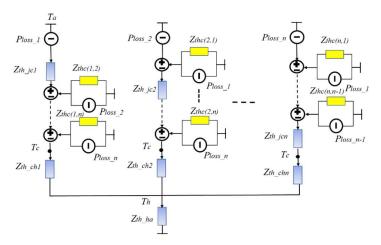

#### 2.2.2 Thermal resistance network models

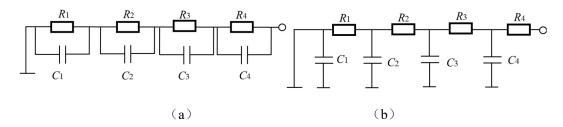

The thermal resistance network method, also known as thermal path method, is fast and effective [38]. It can not only calculate the temperature of junction temperature and case

temperature, but also can describe the thermal distribution of the devices or power converter system and the thermal coupling effect between adjacent devices through the values and distribution of thermal resistances. The thermal resistance network method is generally based on the Foster model [39, 40] and Cauer model [41, 42], as shown in Fig.2.6, and then it can be improved according to the practical application of semiconductor devices or power converters.

Fig. 2.6: Foster and Cauer network models [43]. (a) is Foster model; (b) is Cauer model.

Forster model is to obtain the thermal characteristic parameters of thermal resistance value (R) and thermal capacity (C), and the parameters R and C is by multi-order exponential fitting of dynamic thermal impedance curve which is measured by simulation or testing. Although the Foster model can not reflect the temperature distribution of different layers in the device, it is simple and effective. The Cauer model reflects the real thermal resistance and thermal capacity of the actual physical layer or each level of packaging structure material [44], which can be used to predict the temperature distribution of each layer or level of structure. However, for semiconductor devices, the packaging structure is complex, and it is difficult to obtain accurate thermal parameters among different levels of structure in the device. The thermal resistance network models established in this paper are all based on Foster model.

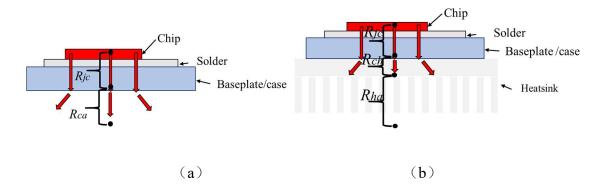

Based on the two kinds of thermal resistance network, the thermal resistance of heatsink can be expanded to establish one-dimensional thermal model. Z. Luo and H. Ahn et al. [44] used lumped parameter method to establish a seven-order electrio-thermal coupling model for a single IGBT power module. The thermal model is improved based on the Cauer model and solved by the fourth order Runge Kutta method. The equivalent thermal resistance and

equivalent thermal capacity are calculated and extracted through the combination of power module structure and FEM simulation. In the FEM simulation, a fixed temperature value is set for the substrate temperature (case temperature) to simulate the dynamic thermal dissipation of the heatsink to obtain the temperature of each layer in the module, which can avoid to calculate different kings of the heatsinks [45]. The one-dimensional thermal resistance network proposed by Graovac. Dusan and Purschel. Marcoet et al. is based on the datasheet given in the device manufacturer to obtain the junction-to-case thermal resistance curve of MOSFET. The device temperature is extracted from the thermal analysis testing, and the case-to-ambient thermal resistance is calculated. Finally, the thermal resistance network model of the device is established [46].

The one-dimensional thermal resistance network can well reflect the junction-to-case thermal resistance and can also quickly calculate the junction temperature of the device, while this kind of model often only focuses on the device self-thermal resistance. Although the extended model based on the self-thermal resistance network considers the thermal resistance of the heatsink, the model is relatively simple. The thermal dissipation of the heatsink is generally in three-dimensional way, and the dissipation way includes thermal conduction and convection. The one-dimensional model can not calculate the thermal coupling between adjacent devices (or modules), and the thermal coupling is usually ignored, which affects the accuracy of the model and the calculation results [44].

As the analysis in Section 1.1, with the development of design requirements for power converters at present and in the future, the shape factor is reduced, while the power density is constantly increasing [47, 48], as a result, the thermal dissipation of power devices slows down with the decrease of device spacing, and then the overall temperature of power converter increases. This trend usually reduces the cooling (thermal dissipation) rate of power converter system and semiconductor devices, thus increasing the mutual thermal coupling between adjacent power devices and increasing the junction temperature of devices. Most of the traditional models usually ignore the thermal coupling between devices or only focus on conduction and the conduction coupling. However, in practical power converter applications,

the conduction thermal coupling formed by metal contact surface or copper wire connection and the convection thermal coupling formed by air convection will have a certain impact on the junction temperature (or case temperature) of the device, and then affect the temperature distribution and junction temperature prediction of the device, and the reliability of the device and system will also be affected.

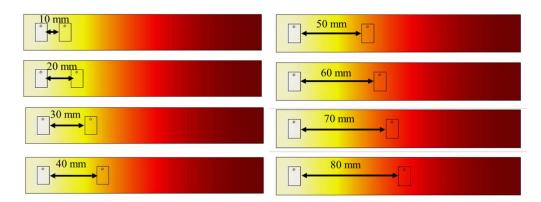

The conduction thermal coupling thermal resistance ( $R_{cdcp}$ ) can be formed in the following ways: one is that multiple thermaling sources, such as power chips or semiconductor devices/modules, are placed on the same metal substrate, such as copper substrate or heatsink, on which the adjacent thermaling sources will affect each other in the process of thermal transfer, and in different disances the thermal coupling is different, as shown in Fig. 2.7; the other way is that a part of the thermal is conducted along the copper line in the PCB, and the thermal between adjacent devices will affect each other through the circuit.

Fig. 2.7: Thermal couping between IGBT chips.

For a single IGBT power module, several IGBT chips and diode chips are generally packaged in an IGBT module. K. Subramanya, J. Pandit et al. and M. Shahjalal et al. analyzed the thermal effect of multiple chips on the same copper substrate in a single IGBT module and gave the calculation method of conduction thermal coupling resistance generated by the adjacent chips, as shown in Fig. 2.8. Compared with the one-dimensional thermal network model, the junction temperature of the device calculated by this model is more accurate.

Fig. 2.8: The conduction thermal coupling thermal resistance ( $R_{cdcp}$ ) in a single IGBT module.

Tang Yunyu and Lin Liaoyuan proposed the influence of installation distance on the thermal coupling of multiple parallel power modules in the power converter, and calculated the average junction temperature of adjacent power modules, while they did not give the specific relationship between different module distances and thermal coupling effect. Moreover, Tang Yunyu and Lin Liaoyuan et al. [49] established a thermal resistance network model of multiple IGBT and diode chips in the power module. The thermal coupling matrix established in the model adopts a given power loss and applies it to the chip and extracts the chip temperature through a series of FEM simulation. The simulation results show that the temperature difference (between the highest point and the lowest point) is 0.52 °C (3.8 cm) and 0.96 °C (6.8 cm) at two different distances, which indicates that the thermal coupling between chips depends on the geometric position of the chips and the chip spacing [50-52]. Similarly, the conduction thermal coupling model established by Li Hui et al. is also generated by adjacent chips on the same substrate in a single power module [53].

The thermal model established by M. Bernardoni and P. Cova et al. calculates the junction temperature of chips through ANSYS simulation, and the conduction coupling thermal resistance under different working conditions by changing the number of chips and chip spacing are studied [54]. The thermal model established by A. S. Bahman and K. Ma compares the temperatures at the same position of different structural layers in the vertical direction of the power module, calculates the conduction coupling thermal resistance when

the thermal flow passes through the vertical structure layer, and analyzes the influence of different working conditions on the conduction thermal coupling resistance [55].

In [53], Li Hui and Liu Shengquan et al. collected the chip junction temperature through FEM analysis, and then extracted the R and C by curve fitting, and then to derive the calculation formula of transient thermal resistance under multi-chip thermaling source. The calculated thermal resistance includes self-thermal resistance and conduction thermal coupling resistance and the junction temperature of edge position chip and non-edge position junction in the improved model and conventional model are compared. In power module applications, as the limited thermal dissipation conditions and the thermal coupling between adjacent chips at the non-edge position, the junction temperature at the non-edge position is often higher than that at the edge position. Compared with the traditional thermal models, the conduction thermal coupling is considered in this paper, and the junction temperature at different positions can be calculated. C. Batard and N. Ginot et al. [56] established a dynamic electric thermal model of a single IGBT module with multi-chips, which is based on the Cauer thermal model. The model adds a first-order R and C into the three-dimensional network. As the thickness of the chip is far less than the length and width, it can be regarded as a thin flat wall structure. Therefore, the thermal transfer mode considered in the model is one-dimensional thermal conduction in each physical layer of the module; when the thermal of the chip is transferred to the copper substrate, the thermal transfer form changed into threedimensional thermal conduction.

A.S. Bahman and K. Ma et al. analyzed the several existing thermal models of devices. The analysis shows that the one-dimensional thermal model is limited to the thermal distribution inside the module and some variables, such as cooling and thermaling conditions. The three-dimensional thermal model based on FEM needs a lot of calculation, which is quite difficult for long-term thermal dynamic simulation. Based on the above analysis, a new concentrated three-dimensional thermal model considering the thermal coupling between different layers is proposed in this study. The critical temperature distribution can be obtained relatively easily from the FEM simulation and the boundary conditions of the thermal model

are analyzed. Finally, FEM simulation and an infrared camera (IR) are used to monitor an opened IGBT module's temperature. Tang Yunyu and Ma Hao et al. established an improved loss calculation model based on the analysis of the thermal impedance of power modules, considering the conduction coupling between multiple power modules. The model can be used to describe the interaction between the current distribution and thermal dissipation of several modules. The main work of the study is as follows: 1) The parameters of stray inductance in adjacent parallel modules are analyzed by FEM. 2) An improved power loss model is established based on impedance analysis, considering the couping between adjacent modules. 3) The RC data extracted from the 3D structural model are used to establish the thermal resistance network model and to obtain the transient thermal impedance of the module and the cooling system. The method presented in this paper is a fast electro-thermal co-simulation method for converter systems with multiple parallel power modules, while they do not consider the convection coupling.

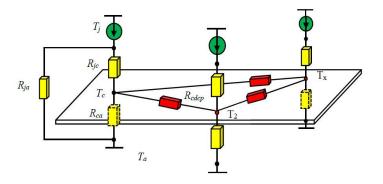

Fig. 2.9:  $R_{cdcp}$  in a power converter.

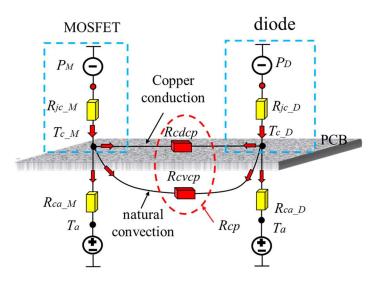

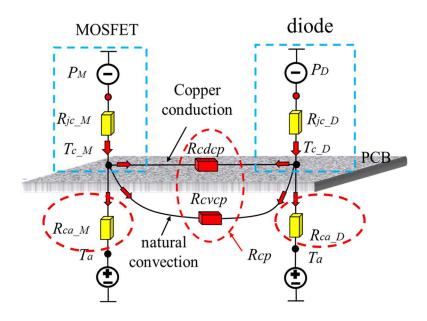

Another way for generating the  $R_{cdcp}$  is the thermal coupling effect between the power components (MOSFET, diode, capacitance, and inductance, etc.) in a converter through the copper wire connection. Erik C. W. de Jong et al. established a thermal resistance network model based on the device's surface/case temperature ( $T_c$ ), as shown in Fig. 2.9. They considered the conduction thermal coupling effect between adjacent devices and the coupling is generated through the interaction of copper wires connected in the PCB. The  $R_{cdcp}$  changes when the distance or position of the devices are changed. Therefore, the thermal coupling

resistance depends on the locations of the devices, the length of the copper circuit (spacing between adjacent devices), etc [18].

Erik et al. firstly optimized the two-dimensional temperature distribution map by device case temperature and then based on the thermal map to optimize the device positions and device spacing and finally the structural optimization of the power converter is realized [57]. The conduction thermal coupling effect between adjacent devices is considered, while it ignores the convection thermal coupling between adjacent devices when the device dissipates thermal to the surrounding air. As the small thickness of copper wire for multiple devices connected by copper wire in the PCB, a considerable part of the thermal is transferred to the air domain in the power converter by convection. Due to the limited space and small device spacing, the thermal will be coupled to each other in the surrounding air, forming convection thermal coupling effect. Convection coupling is dependent on environmental factors and is not constant under different loads and the convection thermal coupling between adjacent devices will be formed in the process of convection thermal dissipation. However, there is no method or standard to extract the convection thermal coupling effect/resistance in the device datasheet, and there are relatively few literatures to study the convection thermal coupling effect [58].

The calculation method of thermal coupling effect is complicated, and the means for calculation of the conduction thermal coupling in literatures is to use the linear superposition principle [59]. For two adjacent thermaling devices, only a certain loss *P* is applied to one device (device I), and the temperature rise of the non-power device (device II) is caused by conduction thermal coupling. Therefore, the conduction thermal coupling effect of device I to device II can be obtained, that is, the values of the conduction thermal coupling thermal resistance. Siliarly, the conduction thermal coupling effect of device II to device I can be obtained through the same method. Based on the principle of linear superposition, this method has certain limitations and is only applicable to linear relations [55, 59]. However, the actual thermal coupling effect contains non-linear convection terms [60]. If the superposition principle is still applied, some errors or wrong results will occur to a certain

extent [3].

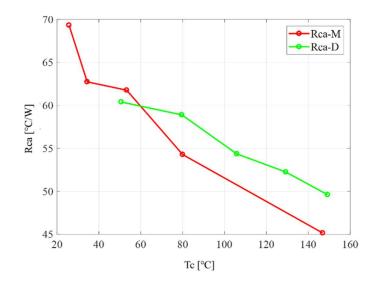

#### 2.2.3 R<sub>ca</sub> and Ambient Temperatures

With regard to the analysis on the self-thermal resistance (case-to-ambient thermal resistance,  $R_{ca}$ ) of the power devices, the measured values of  $R_{ca}$  in datasheet [61] show that the value will vary from the range of 190 °C/W to 310 °C/W [52] when the devices packaged with SO-8 with different forms of substrate (P-DSO-14-4 and P-TO252-3-1) insulate. Meanwhile, the manufacturer Infineon, has provided the variation curves for the junction-to-ambient thermal resistance ( $R_{ja}$ ) packaged under the two conditions of natural convection and forced air cooling, which indicates that the  $R_{ca}$  is variable and the values depends on the package, working conditions and the boundary conditions. The existing literatures generally calculate the  $R_{ca}$  under one working condition and barely analyze the variation under different working conditions.

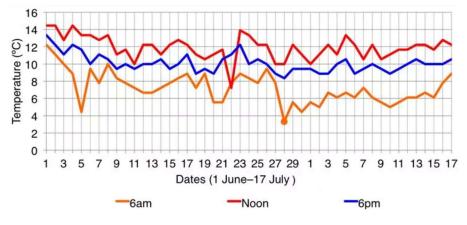

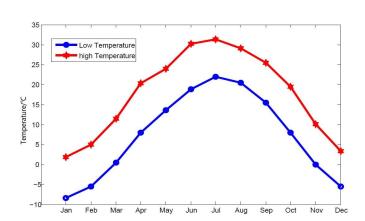

Furthermore, the existing thermal analysis models are always established based on a fixed ambient temperature, such as 25 °C [62], while as a matter of fact the environmental profile could be diversified. The temperature is different at the different time in one day and different seasons [63, 64]. The convection thermal coupling effect between the adjacent semiconductor devices are reliable to the environment temperature so that the junction temperature will be changed as well. On the contrary, the convection thermal coupling will influence the temperature distribution and the junction temperature. The traditional thermal analysis model does not consider the variable ambient temperature [59].

The calculation formula of junction temperature is derived in [62] which considering the conduction thermal coupling effect, while the calculation formula is based on a fixed ambient temperature and the analysis is based on the ideal air region where the parameters are independent to the temperature while the ambient temperatures are not constant and the parameters are ambient temperatures dependent.

The short-term and long-term electro-thermal models are analyzed in [64], and the long-

term one is considered to be affected by the ambient temperature. The junction and case temperatures of power devices are estimated by the models. The device model estimates the voltage-drop and switching energy of the device by considering the current, the blocking voltage of the off-state and the junction temperature change. The thermal models consider the conduction thermal coupling between MOSFETs and diodes integrated in the same package, and the effect of the junction temperature of devices at the ambient temperatures of 25 °C and 30 °C. In this paper, it is pointed out that different ambient temperature has an influence on the thermal coupling and the junction temperature, while only two ambient temperature points are considered, and the thermal model is only for one power device.

In [28], a dynamic ambient profile is analyzed, and a thermal analysis model based on the profile is established. As the power devices are located in the outdoor environment and the ambient temperature is not constant as discussed in [65], the thermal coupling effect among power devices in the system is not considered [66].

## 2.3 Research Gap/Problems

Through the thermal analyses of the literature on power devices at home and abroad, the challenges and problems are:

Self-thermal resistance (case-to-ambient) is dependent on environmental factors, when the convection coefficient changes, the thermal resistance will also change. The existing models only calculate the self-thermal resistance under a single working condition, without considering the change of self-thermal resistance under different working conditions or boundary conditions.

When the distance/spacing between adjacent devices changes, the thermal coupling resistance will change, no matter the multiple devices connected in a PCB through copper wires or multiple power modules/devices on the same heatsink. Therefore, the coupling thermal resistance/thermal coupling effect is dependent on the device spacing, while the existing models rarely analyze the relationship between device spacing and thermal coupling.

The non-uniform distribution of the device case temperature is easy to cause the

influence of thermal coupling between adjacent devices and the concentration of thermal stress in the converter system [67]. And the device spacing and working currents will affect the thermal coupling between adjacent devices, and then affect the case temperature or junction temperature of the devices. Through the relationship between the self-thermal resistance and the coupling thermal resistance between adjacent devices, the thermal distribution uniformity can be satisfied, that is, the case temperature/junction temperature of the devices can work at a certain temperature value or a value range through better understanding of the thermal coupling effect between devices under different working conditions. While this is rarely studied in the literatures.

The existing thermal analysis models of semiconductor devices are usually based on a fixed ambient temperature, while there are few kinds of literatures on different environmental ambient profiles. The convection thermal coupling effect between adjacent semiconductor devices depends on the ambient temperature, which leads to the change of thermal coupling effect and device junction temperature. In addition, the convection thermal coupling which caused by air convection will also have a certain impact on the device temperature rise. However, the existing thermal analysis models rarely analyze the effect of convection thermal coupling.

At present, the studies on the thermal model of power devices are largely device level and mostly on thermal conduction that based on a single device or a module. Moreover, the established thermal coupling mostly just considers the multiple chips inside of a single module, which ignores the conduction coupling between power devices or modules in a power converter system.

# Chapter 3 Modeling and Analysis of Thermal Resistances and Thermal Coupling Between Power Devices

Reliability, cost, and power density are some of the major factors in the design of a power converter [68], where thermal management and design play important roles [27]. According to the analysis in Section 1.1, one of the major faults in power converters is temperature related. The recent trend in the design of the high-power density [29] and compact [69] power converter generally reduces the rate of the device cooling process. As a result, an increased thermal coupling among devices exists. The thermal dissipation, as shown in Figure 1.8 in Section 1.2, thermal dissipation has a negative impact on the performance and life of semiconductor devices and power converters. Hence for high-power density and compact converters, an optimum solution is sought for the thermal management of power devices under different loading conditions [32]. However, the dimensions of traditional Si-based devices approach their fundamental limits, it is difficult to increase the power by improving the structures of the power devices [31]. Although the research and development of the new materials such as silicon carbide (SiC), gallium nitride (GaN) and other semiconductor devices are developing rapidly, the current cost is relatively high. For the traditional silicon devices, the devices themselves and their application are very mature which will still have strong markets and application advantages. Therefore, a better understanding of thermal resistances and good thermal management of silicon-based power devices at different locations and currents facilitate better optimization [32].

To better analyze the thermal coupling effect between power devices, this chapter establishes the thermal coupling experiments of the power converter system, and the case temperature and temperature difference of devices under different spacing types and load current is analyzed. In addition, in order to meet the requirements of the uniformity of the device case temperature or junction temperature distribution for the power converter system, a thermal coupling testing platform for adjacent semiconductor devices is built.

Traditional thermal models do not consider the changes of  $R_{ca}$  and also ignore the effect

of thermal coupling among the adjacent devices. Compared with these models, the proposed thermal resistances modeling approach provides a better understanding of the thermal behavior of power devices. It is helpful for the scheme design of thermal dissipation system (the heatsink selection), the optimization of printed circuit board (PCB) and the design of better power converters [27, 57, 70]. In addition, this chapter is based on the research of establishing the calculation method of thermal coupling effect by the experiments and the measured data. Experiments based analysis method also was adopted by L. mucchi et al [71].

### 3.1 Single testing analysis of power devices

# 3.1.1 Relationships between $T_c$ and $T_j$

For MOSFET, diode and other semiconductor devices the structure is small and complex, so it is relatively difficult to measure the junction temperature [72]. It is easy to destroy the structure of the device when it is unpacked testing [73], and the actual themal transfering mode will be changed to make errors of the measurement results. The case temperature ( $T_c$ ) of the devices is one of the important parameters reflecting the semiconductor performance, and it is also an important technical parameter for heatsinks selection. It can reflect the trend of the temperature change and realize the prediction of the  $T_j$  of the device through the corresponding thermal calculation method [74]. The themal calculation equation of the  $T_j$  and  $T_c$  can be expressed as

$$T_j = P_{loss} \cdot R_{jc} + T_c \tag{3.1}$$

where  $P_{loss}$  is the power loss of the power device,  $T_c$  is the case temperature of device,  $R_{jc}$  is the junction-to-case thermal resistance which is generally given in the datasheet provided by the manufacturer.

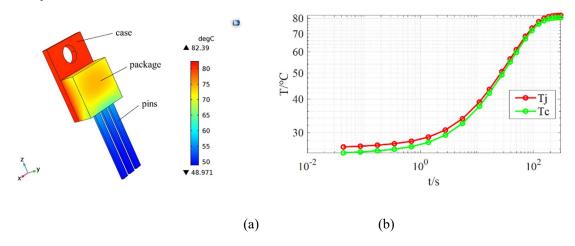

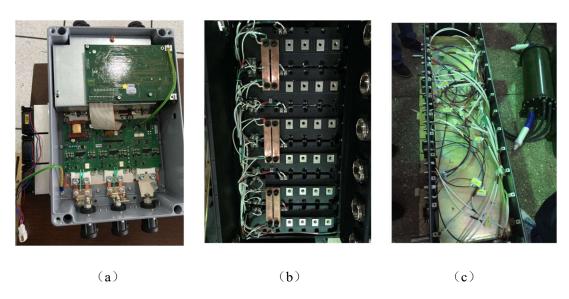

Fig. 3.1 shows the FEM themal model of MOSFET. As shown in Fig. 3.1 (a), different colours constitute the thermal map and this simulation can be used to obtain the junction temperature  $(T_j)$  and case temperature  $(T_c)$ , and the temperature at the chip and copper substrate layer is the highest. Fig. 3.1 (b) is extracted by the simulation results to compare

the  $T_i$  and  $T_c$ .

Fig. 3.1: FEM thermal analysis model of MOSFET: (a) three-dimensional thermal calculation model; (b)  $T_j$  (red solid line) and  $T_c$  (green solid line), where time coordinate is marked in the form of exponential.

COMSOL simulation software can be used to establish the three-dimensional model of devices and system. Based on the three-dimensional model, the corresponding thermal analysis and calculation of thermal conduction and convection can be carried out. In addition, some professional modeling softwares also have thermal analysis modules such as UG NX, etc., which can realize the three-dimensional modeling and carry out some columns of FEM analysis on the established model. In this section, the power device model is established by UG NX and imported into COMSOL through the corresponding interface, and then a series of initial conditions and boundary conditions will be set: the initial  $T_a$  is 25 °C, and a certain power loss will be applied into the thermal source (1.2 W is set in the proposed thermal model). The boundary conditions are as follows: 1) the packed side is considered to be insulated; 2) all thermal will flow from the copper substrate (case) and pins into the surrounding air; 3) the thermal transfering mode is thermal conduction and natural convection. Probes are added at the key points to extract and compare the device temperature. The simulation runs for 1000 seconds until the device temperature reaches a stable state for a certain time.

The thermal transfering mode of the chip and the substrate is metal thermal conduction.

The temperature distribution and the comparison between the  $T_j$  and  $T_c$  of the device in Fig. 4.8 show that as the high thermal conduction coefficient and the fast temperature transfering speed of the metal, the temperature of the two structural layers is the highest. The  $T_j$  and  $T_c$  have the same rising trend from transient state to steady-state, and the temperature difference is only about 1.4 °C under the power loss of 1.2 W. This shows that the temperature characteristics of the packaged semiconductor devices can be characterized by collecting and analyzing the  $T_c$ . Therefore, in the device temperature testing, the temperature characteristics can be reflected by measuring the  $T_c$ , and then the  $T_j$  of the device can be estimated by the  $T_c$ . The thermal model can also be used in other TO-220 packaging devices, such as diodes.

#### 3.1.2 Single testing of power devices

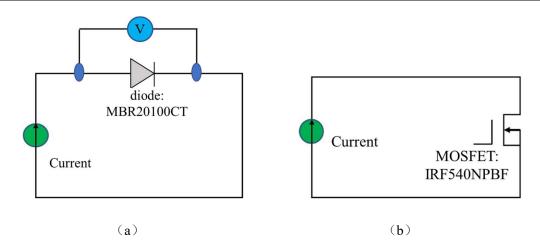

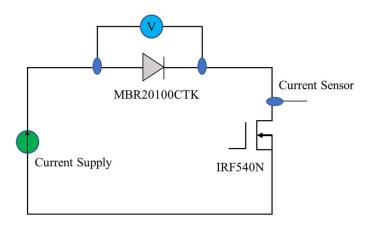

The single test of semiconductor is to supply power to a single device directly through a controllable current source, and the temperature rise of the device is realized by changing the size of the current source. In order to avoid the interference of other devices, the single testing only has a single semiconductor device, which is connected to the circuit in on-state mode without other components. For the MOSFET used in the testing, it should be noted that the initial condition is that the MOSFET can be turned on only after the PN junction of the gate-source electrode is activated by a certain voltage driving signal. Generally, a voltage of  $5 \sim 15$  V can be selected for the driving, but the smaller the driving voltage, the greater the on internal resistance ( $R_{DS}$ ) corresponding to MOSFET [75]. In this section, a 15 V DC voltage source is selected as the driving signal. The voltage drop at both ends of the diode is collected by a digital multimeter. The working current of MOSFET and diode is monitored by the current sensor. The single testing circuit is shown in Fig. 3.2.

Fig. 3.2: Single testing circuit diagram of power devices: (a) for diode; (b) for MOSFET.

There are two methods to realize the temperature rise of the power devices. The first one is based on different driving forms and switching frequencies to collect the switching loss, on-state loss, and other power losses of each device when the converter system is working. All power losses will be transferred in the form of thermal and then transferred in the device and the surrounding air, causing the temperature of the case/junction temperature to rise from ambient temperature ( $T_a$ ) and finally reach a stable state. The second method is to make the device working under the on-state mode. When the device switches on, a certain loss can be generated, which will increase the case temperature. In this case, the loss of the device is only the on-state loss. As discussed in [76] and [77], a controlled current source or a given power loss can increase the temperature of the device [76, 78], regardless of the types of the power loss. Based on the above analysis, the second method is employed in this study to establish the thermal coupling testing platform for the single measurement and the thermal coupling measurement.

#### 3.1.3 Losses calculation

Power loss is considered to be the main cause of thermal generation in semiconductor devices [79, 80]. In the single device testing in Section 3.1.2, the power device is in the on the state, and the temperature-rise of the device mainly comes from the on state loss [33], and its power loss can be calculated by (3.2) [33].

$$P_M = I^2 \cdot R_{DS} \tag{3.2}$$

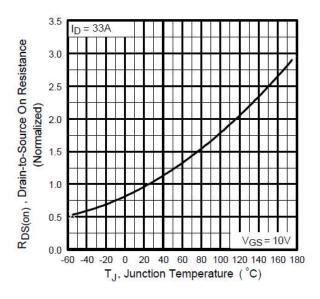

where  $P_M$  is the power loss and I is the working current.  $R_{DS}$  is the on-state resistance of MOSFET, which is dependent on the  $T_j$  [127]. The relationship between  $R_{DS}$  and  $T_j$  is always given by manufacturers, as shown in Fig. 3.3. According to the relationship, the values of  $R_{DS}$  at different temperatures (as shown in Table 3.1) can be obtained, and then the losses of MOSFET devices can be calculated.

Fig. 3.3: The relationship between  $R_{DS}$  and  $T_j$ .

There is no reverse recovery loss for the diode in the on-state, and the power loss of the diode is mainly the on-state loss. Therefore, the loss can be expressed by

$$P_D = V_{fd} \cdot I \tag{3.3}$$

where  $V_{fd}$  is the forward voltage drop at both ends of the diode, and I is the current flowing through the diode pin.

By bring the  $T_c$  of MOSFET and diode collected from the single device testing of semiconductor devices into (3.2) and (3.3), the power losses under different operating currents can be obtained, as shown in Tables 3.1 and 3.2 respectively.

Table 3.1: The values of  $T_c$ ,  $R_{DS}$  and  $P_M$  for MOSFET.

| <i>I /</i> A | $T_{c\_M}/^{\circ}\mathrm{C}$ | $R_{DS}/\mathrm{m}\Omega$ | $P_M/\operatorname{W}$ |

|--------------|-------------------------------|---------------------------|------------------------|

| 1            | 25.75                         | 44                        | 0.044                  |

| 2            | 34.43                         | 46.64                     | 0.187                  |

| 3            | 53.27                         | 55                        | 0.495                  |

| 4            | 80.01                         | 66                        | 1.056                  |

| 5            | 146.85                        | 110                       | 2.750                  |

Table 3.2: The values of  $T_c$ ,  $V_{fd}$  and  $P_D$  for diode.

| I/A | $T_{c\_D}$ /°C | $V_{fd}$ /V | $P_D$ /W |

|-----|----------------|-------------|----------|

| 1   | 50.66          | 0.46        | 0.46     |

| 2   | 79.59          | 0.50        | 1.00     |

| 3   | 105.85         | 0.51        | 1.53     |

| 4   | 129.26         | 0.51        | 2.04     |

| 5   | 149.19         | 0.51        | 2.55     |

# 3.2 Thermal Coupling Experiments and Requirements of Temperature Control for Power Converter Systems

## **3.2.1 Thermal Coupling Experiments**

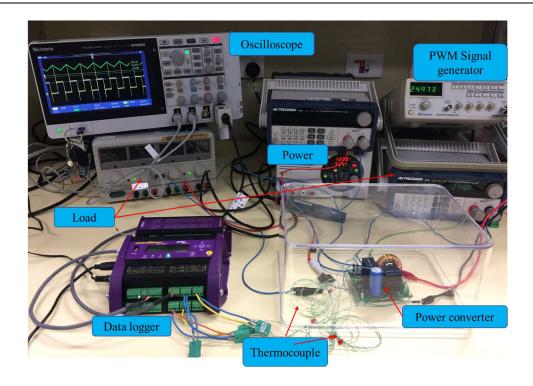

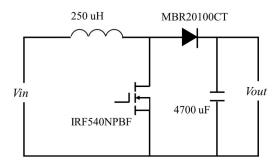

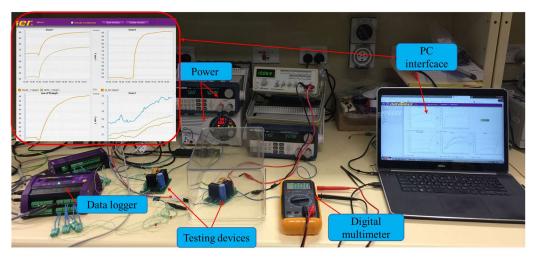

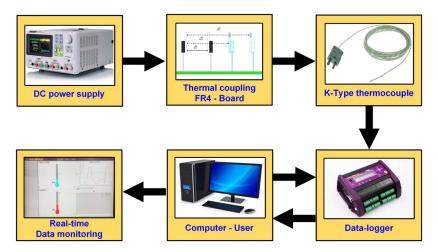

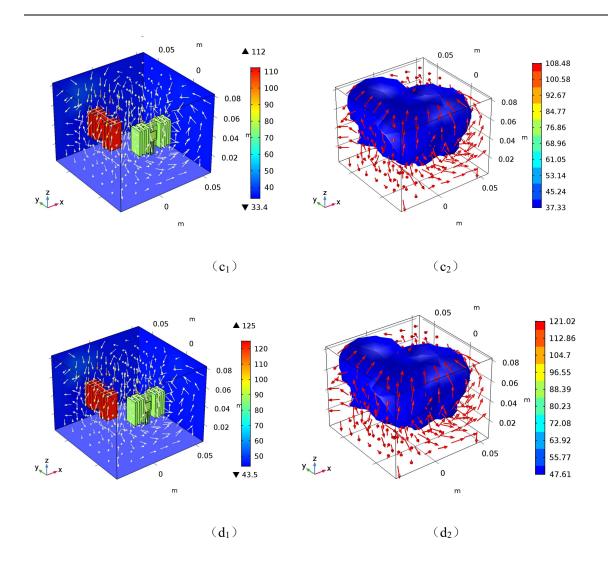

In this section, thermal coupling testing platform for the power converter is established as shown in Fig. 3.4, and its circuit diagram is shown in Fig. 3.5.

Fig. 3.4: Thermal coupling testing platform of power converter.

Fig. 3.5: The circuit diagram of power converter.

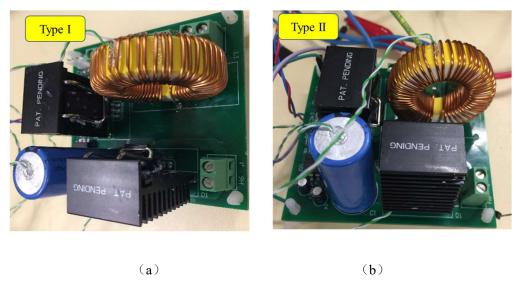

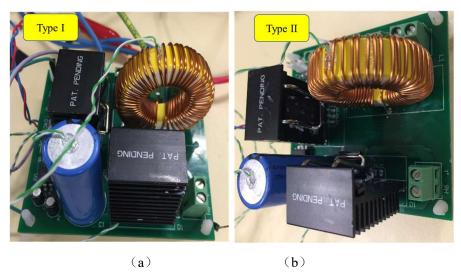

In this platform, the selected switching frequency of power converter is commonly used, which is 10 kHz, 25 kHz and 50 kHz, respectively. The duty cycle is set to 0.5, and the load resistance is 8  $\Omega$ , 6  $\Omega$  and 5  $\Omega$ , respectively. The type of MOSFET is IRF540 NPBF, the diode model is MBR20100CT, and the semiconductor devices are in TO-220 package. The capacitor is MAL215050472E3-35 V and the value of its capacitance is 4700 UF. The inductance is MCAP115018047A and the value of its inductance is 250 uH. In order to study the influence of device spacing and thermal coupling effect of adjacent devices on the

junction temperatures under different working conditions, two different types of power converters are tested and compared: type I with large device spacing and type II with small device spacing, as shown in Fig. 3.6.

Fig. 3.6: Two types of power converters: (a) Type I with large device spacing; (b) Type II with small device spacing.

The power converter system is tested in this section. The MOSFET is controlled by PWM wave and its on-state and off-state are controlled by the given duty cycle and switching frequency. During the testing of the converter system, the input voltage and output voltage of the circuit are 12 V and 24 V, respectively. The case temperature of the power devices of the converter system are collected by changing the load resistances.

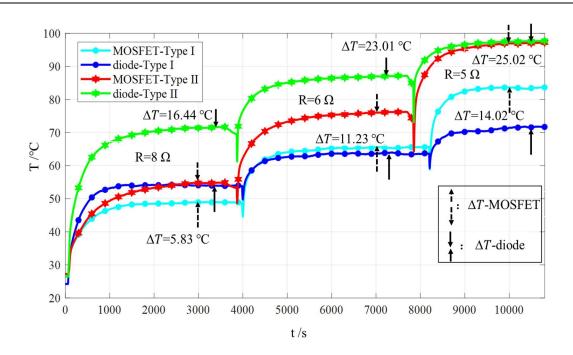

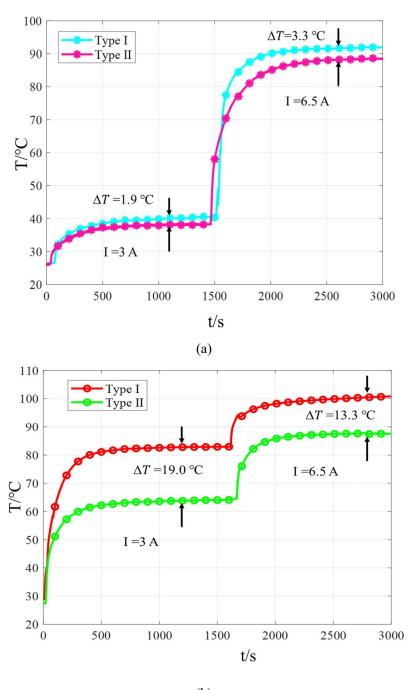

Fig. 3.7 shows the measurement results of case temperature and the calculation results of the temperature difference of the devices with different types of spacing. In this figure, the case temperature of MOSFET and diodes with two types of spacing (type I: large spacing, dot mark on the blue and cyan solid line; type II: small spacing, six-star mark on red and green solid line) are compared at the switching frequency of 25 kHz and the load resistance are  $8 \Omega$ ,  $6 \Omega$  and  $5 \Omega$ , respectively.

Fig. 3.7: Comparison of case temperature and the temperature difference of power devices with different spacing types.

It can be seen from the comparison results that, for both MOSFET and diode, with the decrease of device spacing the case temperature of the device increases under a same working condition. This shows that the thermal coupling effect between adjacent devices is affected by the device spacing, and with the decrease of the spacing the thermal coupling effect increases. In addition, according to the comparison results of case temperature difference in Table 3.3, we know that when the load resistance decreases, the current flowing through the semiconductor device increases. At this time, the case temperature difference of the two devices changes with the change of current, which shows that the thermal coupling effect between adjacent devices is affected by the working current, and with the increase of the current the thermal coupling effect increases. It is verified that the thermal coupling effect obtained from the thermal coupling testing platform (only the MOSFET and diode are tested) of devices can also be applied to the case where multiple devices exist in the power converter system.

Table 3.3: Temperature difference of case temperature under different load resistances.

| $R/\Omega$                               | 8     | 6     | 5     |

|------------------------------------------|-------|-------|-------|

| $\Delta T_{c\_M} / {}^{\circ}\mathrm{C}$ | 5.83  | 11.23 | 14.02 |

| $\Delta T_{c\_D} / {}^{\circ}\mathrm{C}$ | 16.44 | 23.01 | 25.02 |

## 3.2.2 Temperature Controling Requirements of Power Converter System

There are two important considerations in the converter design phase to ensure the reliable operation of the converter [81, 82]: (1) Maximum junction temperature  $T_j$  of the devices, e.g., Si-based devices, cannot exceed the maximum  $T_j$  ( $T_{jmax}$ ) 175 °C [24, 83]. We usually make the devices working around the temperature of 150 °C to ensure the devices working in safe operation; and (2) the ability to share thermal among the components with a more uniform temperature distribution [18, 70]. As discussed in [57] the optimal temperature range of the silicon semiconductor devices are about 110 °C.

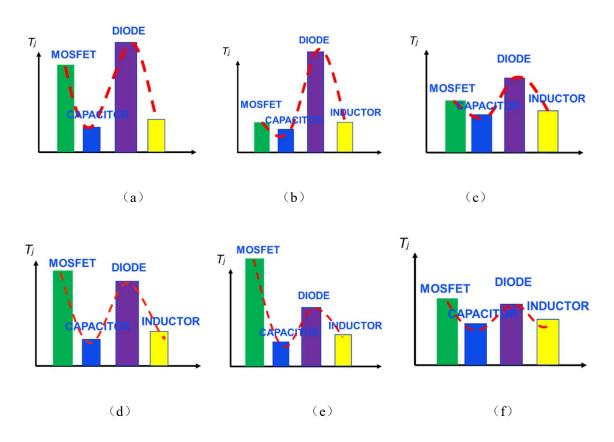

As discussed, the thermal dissipation between power devices slows down with the decrease of devices spacing, which result in the temperature increasing of the power converter. Fig. 3.8 describes six cases of thermal maps in UTS Tech lab, where Fig. 3.8 (f) shows the best thermal profile for converter design and operation. Followed by Fig. 3.8 (c), while in the operation of other systems, the temperature distribution peaks locally, and the high-temperature devices have serious impact on the thermal coupling of the low-temperature devices, which will affect the thermal distribution of the overall performance of the system [84]. This means it is desirable to control the temperatures at junctions to operate the power devices at good temperature ranges within the safety operation region even in the worst-case scenario. The methods for controling the case temperature or junction temperature can be by controlling the circuit, then the temperatures can be changed under different power losses, or by adjusting parameters of the drive circuit [85].

In this chapter, based on the fact that in the desigh stage when the heatsinks of the

devices are not selected, the self-thermal resistances are variable; and when the position of the devices and the device spacing are not determined, the coupling thermal resistances are also variable. Thermal coupling resistances analysis among the components can help with the thermal distribution, and by establishing the corresponding thermal resistances network model to analyze the relationships between the variable thermal resistances, the junction pr case temperatures can be controlled.

Fig. 3.8: Thermal maps of a basic boost DC-DC converter in six cases:(a) MOSFET and diode are with higher case temperature, and the diode is with the highest case temperature; (b) the diode is with the highest case temperature; (c) the temperature distribution is relatively smooth, and the diode is with the higher case temperature; (d) MOSFET and diode are with higher case temperature, and MOSFET is with the highest case temperature; (E) MOSFET is with the highest case temperature; (f) the temperature distribution is relatively smooth, and MOSFET is with the higher case temperature.

#### 3.3 Thermal Coupling Testing Analysis of Power Devices

In the design stage, the thermal coupling effect between adjacent power devices, including the conduction thermal coupling effect and the convection thermal coupling effect, is further analyzed and calculated at fixed values of case temperature ( $T_c$ ) of the devices. It is divided into two steps:

- 1) the thermal coupling network (TCRN) model between adjacent devices is established, and the case-to-ambient thermal resistance ( $R_{ca}$ ) and coupling thermal resistance ( $R_{cp}$ ) are analyzed under different working conditions.

- 2) the relationships between individual Rca and their  $R_{cp}$  to the adjacent device have been obtained for different spacing and load currents during the design phase consideration.

Based on the two steps above, the themal coupling effect can be obtained. New  $T_c$  data from the calculation and measurement, which employs different spacing verifies the proposed thermal model and the relationships. The error analysis verifies the correctness and validity of the calculation method of thermal coupling effect between power devices under the fixed case temperature.

## 3.3.1 Thermal Coupling Testing of Adjacent Devices

The temperatures of the devices are affected by the thermal coupling, which includes conduction and convection coupling. As discussed in Section 3.2.2, temperatures should be controlled in some fixed values to make the converter work in a good performance. In order to better analyze the thermal coupling effect and its influencing factors, a thermal coupling measurement platform for power devices is established, as shown in Fig. 3.9.

Fig. 3.9: Thermal coupling measurement platform.

Fig. 3.9 shows the thermal coupling measurement platform to test two identical types of MOSFET (IRF540N) and diode (MBR20100CT) which are the same ones as shown in the single measurements. The energy source is a current-controlled power supply and the two devices are connected in series. The devices are in the fully on-state and a digital multimeter is used to measure the voltage drop of the diode.

In the application of the power converters, heatsinks are employed for thermaling devices to transfer thermal effectively and the thermal dissipation capability, size, and installation location need to be considered. Hence in a converter, spacing should be given between the components to avoid installation interference. In the design of the platform, the spacing between two devices started from d = 12 mm, and was followed by d = 18 mm and d = 22 mm.

In this platform,  $T_c$  starts from the ambient temperature ( $T_a$ ) and collects every 2 seconds until the temperature reaches a relatively steady level before the next load current values. In the steady state, it takes a longer time to obtain Tc when the magnitude of the current becomes larger. Therefore, to get a relatively stable Tc, the duration of testing should be

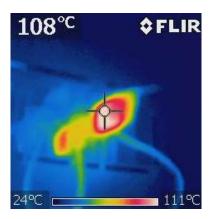

increased by increasing the operating current. For all measurements at different spacings, the total testing time is 3500 s. All the collected Tc data are recorded through a thermal datalogger (DT 80) and the values are verified by an infrared camera. Under the working condition of d = 18 mm and I = 3 A, the steady-state case temperatures for the diode ( $T_{c-D}$ ) are 108.42°C (collected by the datalogger) and 108.0 °C (taken by the infrared camera, as shown in Fig. 3.10), respectively. The error between the two methods is 0.39% which shows good accuracy.

Fig. 3.10:  $T_c$  taken by the infrared camera.

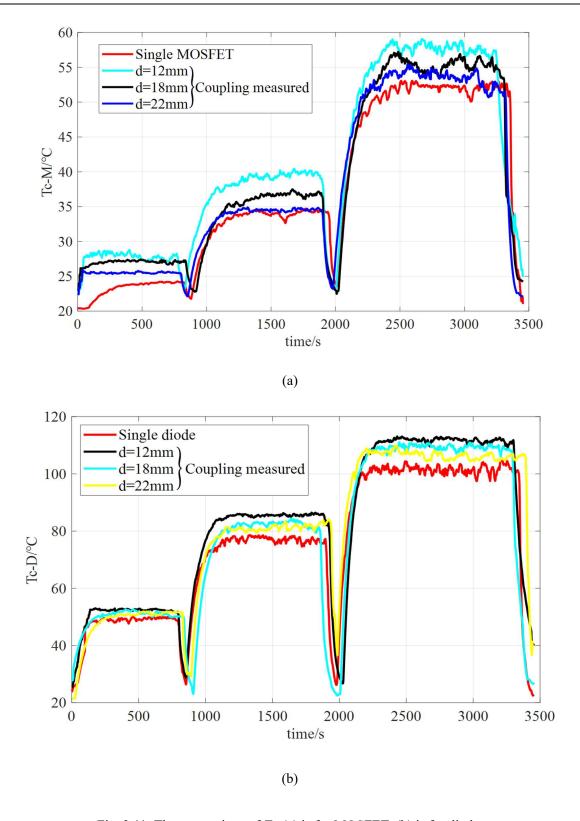

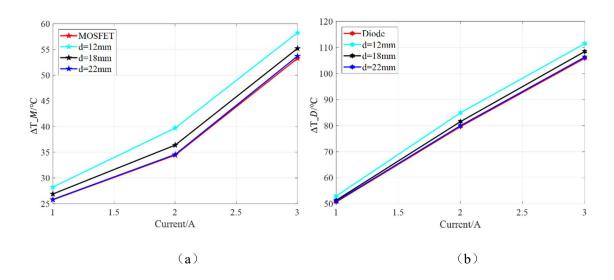

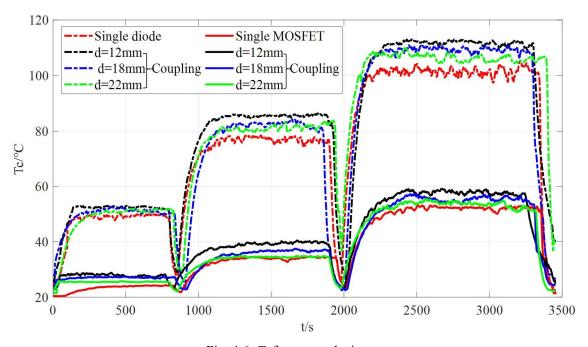

Under different working currents, the comparisons of  $T_c$  obtained by the testing of individual devices and thermal coupling at different spacings are given in Fig. 3.11, in which the red solid line is the case temperature of the devices collected in the single testing platform in Section 3.1.2 and other color solid lines are the temperatures collected from the thermal coupling measurement platform. It is observed from the measurement results that:

- I)  $T_c$  rises rapidly from  $T_a$  for the MOSFET and diode and the rate of temperature-rise decreases near the steady-state.

- II)  $T_c$  shows the lowest value when a single device is tested.  $T_c$  is higher when the spacing between two devices decreases.

Fig. 3.11: The comparison of  $T_c$ . (a) is for MOSFET; (b) is for diode.

#### 3.3.2 Calculation of Self-thermal Resistance

In self-thermal resistance,  $R_{jc}$  depends on metal thermal conduction, and the values are generally given in the datasheet provided by the manufacturers. The maximum  $R_{jc}$  of MOSFET (IRF540NPBF) is 1.15 °C / W, and that of diode (MBR20100CT) is 2.0 °C / W.

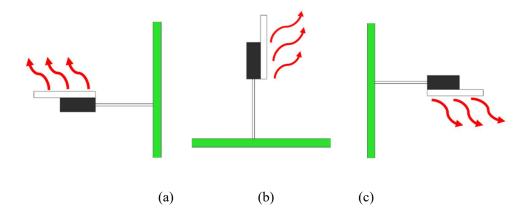

Convection thermal transfer is the thermal transfer between fluid and solid wall, which depends on the movement of fluid to transfer the thermal [3]. Therefore, convection thermal transfer is closely related to the flow conditions and density of the fluid. As shown in Fig. 3.12, the convection thermal transfer of the same device is different when it is located at different hot surfaces.

Fig. 3.12: Different positions of hot surface. (a) the hot surface is upward; (b) the hot surface is vertical;

(c) the hot surface is downward.