**Research Article**

# Distribution system protection by coordinated Received on 13th July 2019 fault current limiters

Revised 7th November 2019 Accepted on 3rd January 2020 E-First on 3rd February 2020 doi: 10.1049/iet-esi.2019.0066 www.ietdl.org

Amir Heidary<sup>1</sup> . Hamid Radmanesh<sup>2</sup>, Seyed Hamid Naghibi<sup>1</sup>, Sahand Samandarpour<sup>1</sup>, Kumars Rouzbehi<sup>3</sup>, Negin Shariati<sup>4</sup>

<sup>1</sup>Department of Electrical Engineering, Zanjan Branch, Islamic Azad University, Zanjan, Iran <sup>2</sup>Electrical Engineering Department, Shahid Sattari Aeronautical University of Science and Technology, Tehran, Iran <sup>3</sup>Departamento de Ingeniería de Sistemas y Automática, Universidad de Sevilla, Sevilla, 41092, Spain <sup>4</sup>School of Electrical and Data Engineering, University of Technology Sydney, Sydney, NSW, 2007, Australia ⊠ E-mail: amir.powersys@gmail.com

Abstract: The protection of distribution networks is one of the most substantial issues, which needs special attention. Using appropriate protective equipment enhances the safety of the power distribution network during the fault conditions. Fault current limiter (FCL) is a kind of modern preserving system being used for protecting power networks and equipment. One of the main concerns of power networks is the voltage restoration of buses during faulty conditions. In this study, a group of coordinated DC reactor type faults current limiters are designed and tested to protect the network and restore its buses voltage within the fault period. To coordinate FCLs and measurement devices during the fault sequences, a wireless communication system and decision-making computer are used. The proposed FCLs coordination strategy is modelled and simulated in MATLAB platform and the results are validated by the developed laboratory test setup.

#### 1 Introduction

In modern electrical networks, a large variety of electrical loads and generators use protective equipment. Fault current limiter (FCL) is a device that has very low impedance during the normal operation condition, while it shows considerable impedance during the fault state [1, 2]. So far, a variety of FCLs have been introduced such as superconductive FCL [3, 4], resonance-type FCL [5, 6], transformer-based FCL [7, 8], saturated core FCL [9, 10] and permanent magnet-based FCL [11, 12]. A type of FCL based on superconductive inductance was introduced in [13, 14]. The AC power systems, performance improved by the hybrid rectifier and an insulated-gate bipolar transistor (IGBT) switch-based FCL [15-17]. In [18] a dual function smart protection system is developed. The protection system utilises a communicating process to provide relays with additional context and also facilitates the coordination [19]. The Internet of Things (IoT) enables architecture for deployment of independent federated services and applications, characterised by the high degree of autonomous data capture, event transfer, network connectivity and interoperability [20, 21]. There is an emergent interest in IoT technologies in various industries such as agriculture, food processing industry, environmental monitoring, security surveillance, and bush fire detection and so on [22]. DC reactor-based FCL (DCR-FCL) is a valuable equipment to protect electrical networks against potential faults [23]. The FCL is a feasible solution to address the mismatching overcurrent protection system problem between microgrid and distributed generators [24]. Recently, a compound type of reactor-based FCL with the capability of fast circuit breaking is presented in [25, 26]. IoT as a data transferring system has been proposed to increase FCLs reliability [27-29].

The main contribution of this paper to the existing body of knowledge is on the development and implementation of a coordinated FCL technology that will be used to protect networks by different processes including sense, compute, communicate and FCL coordination. The method is presented according to the fault current analysis and applying the controlling decision to the coordinated FCLs. The achievements of the proposed method over the traditional FCL approaches are:

- Limited fault current value can be accurately adjusted after a coordination delay.

- Limited fault current value for each source can be independently adjusted after a communication delay.

- Load voltage remains in an acceptable range during the fault period.

- Series equipment work in their nominal condition during the fault limiting mode.

- The current of each line limited in the valid range.

- Using controllable DCR-FCL with the capability of fault current magnitude adjustment is used.

Under study network is presented in Section 2. Section 3 demonstrates the power communication implementation. The analytical study is given in Section 4. In Section 5 the control strategy is provided. Section 6 describes simulation results. Section 7 presents the experimental results as well as a comparison study between simulation and laboratory results. Subsequently, the conclusion section summarises the key achievements of this study.

# 2 FCL placement and configuration in the studied network

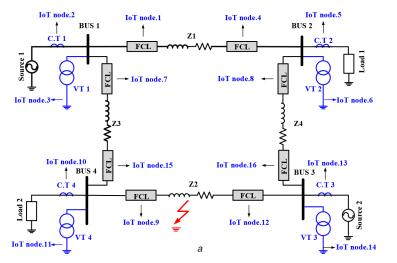

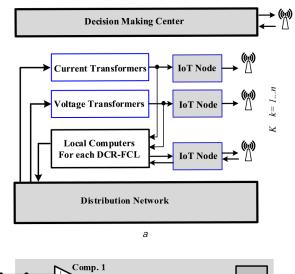

Single line diagram of the under study network is shown in Fig. 1a which includes FCLs, current transformers (CTs) and voltage transformers (VTs) which are equipped with wireless communications. The distribution system feeds by two sources and impedance of the lines are  $Z_1$  and  $Z_2$ ,  $Z_3$  and  $Z_4$ .

Fig. 1b shows the controlled switch-based DCR-FCL topology. The DCR-FCL includes a DC reactor, an IGBT switch, damping resistor  $R_1$ , and the full-bridge rectifier consisting of D1-D4. Each line is protected by two FCLs in its sending and receiving ends.

The duty cycle of the IGBT is determined by the control system and received by communication nodes. D1 and D2 conduct in the positive half-cycles, whereas D3 and D4 conduct in the negative half-cycles, and the output voltage of the rectifier bridge reaches the DC reactor voltage drop to zero, during the normal operation mode. In the normal state, the IGBT switch is closed. In the fault

IET Energy Syst. Integr., 2020, Vol. 2 Iss. 1, pp. 59-65

**Fig. 1** *DCR-FCL placement in the power network* (*a*) Single line diagram of the network, (*b*) DCR-FCL

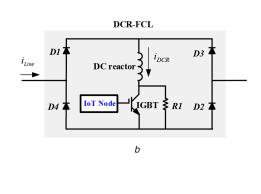

Fig. 2 Single line diagram of network including FCL

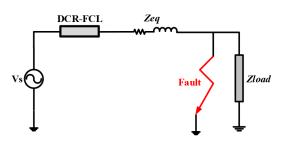

Fig. 3 DC reactor and line currents during normal and fault conditions

state, the current high variation that is conducted by D1-D4 like a normal state causes a high voltage drop on the DC reactor and by IGBT switching DC reactor adjust between two limited levels depends on IGBT pulse width. The IoT is one of the most practical technologies, which is able to connect to the unlimited world of internet. Undoubtedly, the industry is an important part of this puzzle that can profit from this growing technology [28]. In this paper, VTs, CTs and FCLs are equipped with a wireless network node to achieve protected coordination. The sensing layer contains CT and VT where the outputs of this equipment are sent to the faults detection and processing unit.

In the network layer, nodes are connected to each other and exchange the fault information. According to the location and responsibilities of the nodes, they must take the proper action. All nodes are connected to the main server which is responsible to make all decisions. The advantages of the server are light processing load in nodes, cost efficiency, simple application layer deployment, scalability and the ease of maintenance and upgrade. With the aid of the server, all nodes are directly communicating to each other. Unquestionably, nodes must make the decision themselves. Hence, scalability is a major issue of this topology as each node has a heterogeneous status according to its location, energy source and load coverage area.

The application layer manages all parts of the system and controls the actions of each node in the system. The responsibility of the application layer is analysing the input data and making decisions for each involving node in the system using control strategies. The time complexity of the control process must be as low as possible since the speed of processing and actions in the system is crucial and directly affects the system performance.

# 3 DCR-FCL analytical study

The analytical study is carried out, taking into account the behaviour of DCR-FCL in the sample diagram of Fig. 2 which shows the circuit for studying the behaviour of DCR-FCL without the controllable electronic switch in both fault transient and normal steady-state.

In Fig. 2,  $Z_{eq}$  indicates the equivalent impedance of the source and the line which is modelled in series and  $V_s$  is the voltage of the sinusoidal source. The load impedance includes resistance and inductance and fault is modelled in parallel with the load while its resistance is nearly zero. The analytical study of the proposed system is presented in the following sections.

#### 3.1 Line current without fault occurrence

In this case, it is assumed that there is no fault in the network and line current is in steady-state. The DC reactor is bypassed via DC output of the rectifier bridge, while there is a negligible voltage drop on it

$$v_{\rm S}(t) = V_{\rm max} \sin \omega t \tag{1}$$

$$v_{\rm DCR}(t) = \frac{{\rm d}i(t)}{{\rm d}t} = 0 \tag{2}$$

$$I_{\rm line} = \frac{V_{\rm s}}{Z_{\rm total}} \tag{3}$$

$$Z_{\text{total}} = (R_{\text{eq}} + R_{\text{load}}) + j(X_{\text{eq}} + X_{\text{load}})$$

(4)

where (1) expresses the source voltage and (2) shows the current changes and DC reactor voltage drop in normal operation mode. In this mode, the line current amplitude depends on the source, line and load impedances. Equation (3) demonstrates the line current and (4) introduces the total impedance of the circuit.

#### 3.2 Line current in fault state (uncontrolled DCR-FCL)

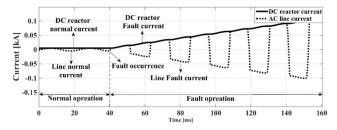

During the fault condition, the current of the DC reactor is equal to the line maximum current. In the instant of fault occurrences, the fault current suddenly increases, but the DCR-FCL limits the fault current by DC reactor time constant as shown in Fig. 3. In this part, the behaviour of DCR-FCL is studied without controllable IGBT in AC networks. Mathematical equations are derived for the fault condition as follows:

$$i_{\text{DCR}}(0) = \max (i_{\text{Line}}(t))$$

(5)

IET Energy Syst. Integr., 2020, Vol. 2 Iss. 1, pp. 59-65

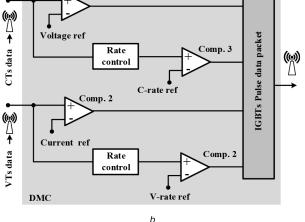

Fig. 4 Controlling mechanism (a) Proposed control diagram, (b) DMC

$$i_{\rm DCR}(t) = i_{\rm DCR}(0) + \frac{\max(v_{\rm S}(t))}{R_{\rm eq}} \left(1 - e^{-(R_{\rm eq}/L_{\rm DCR})t}\right)$$

(6)

$$R_{\rm eq} = R_{\rm s} + R_{\rm Line} + R_{\rm f} \tag{7}$$

$$i_{\text{DCR}}(t) = i_{\text{DCR}}(0)e^{-(R_{\text{DC}}/L_{\text{DCR}})t}$$

(8)

$$R_{\rm DC} = R_{\rm D} + R_{\rm S} + R_{\rm DCR} \tag{9}$$

$$i_{\text{Line}}(t) = \frac{v_{\text{s}}(t) - v_{\text{DCR}}(t)}{R_{\text{eq}} + L_{\text{eq}}}$$

(10)

In (7),  $R_{\text{Line}}$ ,  $R_{\text{S}}$  and  $R_{\text{f}}$  are the resistance of the line, source and fault, respectively. In (9),  $R_D$  and  $R_{DCR}$  are the resistance of diodes and DC reactor, respectively. Also, iLine and iDCR are line current and current of the DC reactor, respectively.  $L_{\text{DCR}}$  and  $L_{\text{eq}}$  are inductance of DC reactor and equivalent inductance of the line and source, respectively. In the case of the fault occurrence, the analytical study is divided into two parts. In the first part, the line current is equal to DC reactor current and it is not bypassed by the diodes which work as the series reactor in the network. Equations (6) and (8) show charging and discharging current, respectively. In (10), line current in the fault state is shown considering Fig. 2. In this equation, it is clear that Fig. 3 shows line and DC reactor current with applying uncontrolled DCR-FCL. This figure proves that the operation delay of DCR-FCL for fault current limiting is almost zero even without a control switch. By using uncontrolled DCR-FCL, line current increases according to the DC reactor time constant and the first peak of fault current suppresses. It is a valuable feature to compensate communication system delay.

# 3.3 Line current in fault state (controllable DCR-FCL)

While IGBT switch is ON, DC reactor current is raised considering (6). In this equation, t is related to the duty cycle of IGBT and determined by the coordination system. Due to the increasing of t, DC reactor current will increase. By turning off IGBT, DC reactor current is declined assuming (11)

$$i_{\rm DCR}(t) = i_{\rm DCR}(0)e^{-(R_{\rm DC} + R_1/L_{\rm DCR})t}$$

(11)

Here  $R_1$  is the IGBT parallel resistance. By controlling the control pulse of IGBT and considering the charging and discharging DC reactor current, the current of the line can be adjusted accordingly. By determining the current limiting value of each DCR-FCLs in the coordination system, communicated pulse for IGBTs can protect the power network. Consequently, by using DCR-FCL with the fixed pattern or coordinated pattern of pulse width controlling power network can be protected as well.

# 4 Control strategy of the coordinated DCR-FCLs

Fig. 4*a* shows the control strategy diagram, which includes one decision-making centre (DMC) and '*n*' measurement units and local computer (LC). A DMC is responsible to analyse the transferring data from VT and CT and send data to FCLs in order to manage the fault current. The main target of DMC is restoring all bus voltages to their valid value by controlling the value of current in each line in the fault condition. This goal can be achieved by generating a proper pulse for FCLs to adjust its limiting current. The control strategy is divided into two parts including LC and coordinated control.

During the fault occurrence, VTs and CTs measure the voltage sag and directly send the measures results to the local computers to create fast decision before DMC coordinated signal to all DCR-FCLs.

### 4.1 IoT-based data acquisition system

In the data acquisition system, the VT and CT data is converted to digital signals and which will be transmitted to the communication network. Every sensor contains a pseudo-code as shown with code 'A' in Fig. 5. This code creates a digital data from an analogue sensor. The variable 'X' determines the number of clocks according to the sensor type.

### 4.2 Data analysis

In this stage, data received by DMC is compared with the references value to detect the fault and its approximate location according to code B of Fig. 5. By comparing the voltage of buses and line current with the level of voltage sag and over current, it is possible to find an output variable that determines the data packet of coordinated FCLs.

# 4.3 Fault pulse series

In the normal operation mode, after detecting the fault and matching the proper pulse width, control commands are generated by DMC to communicate the power electronic parts. In this part, the system relay on the hardware and topology which are used in the communication network. Code 'C' includes pulse series data packet according to the signal comparison, fault proximate location and fault type.

# 4.4 Fault correction validating

This stage checks whether the fault is truly fixed or not, or the network fault is addressed or not. This is done by the comparison method again.

Pattern s is the network signal during the normal mode. In this case, the signal is compared with the pattern s and if the program realises that the network has been back to the normal mode, it sets the output as the default output. If this condition is not met, the program tries to find out, if the fault is fixed in the network or not.

IET Energy Syst. Integr., 2020, Vol. 2 Iss. 1, pp. 59-65

| Stage | Pseudo code                                                        |

|-------|--------------------------------------------------------------------|

| Α     | Define Sensor[x];                                                  |

|       | $for(j=0, j \le x, j++)$ {                                         |

|       | Sensor[j] = get signal value;                                      |

|       | Reproduce(Signal[i]);                                              |

|       | }                                                                  |

| В     | Get Signal k;                                                      |

|       | for(i=0; i < x; i++)                                               |

|       | Compare(Signal k, reference i);                                    |

|       | if (result = fault){                                               |

|       | Output = fault pulse series;                                       |

|       | Calculate distance (Signal k, pattern i)                           |

|       | Fault-type = reference type;                                       |

|       | }else                                                              |

|       | Output= default;                                                   |

|       | }                                                                  |

| С     | Get reference value;                                               |

|       | Get distance;                                                      |

|       | Fault pulse series =calculate pulse series(reference, fault-type); |

| D     | Get Signal k;                                                      |

|       | Compare (Signal k, reference s)                                    |

|       | if (result=solved)                                                 |

|       | Output= default;                                                   |

|       | else {                                                             |

|       | for(i=0, i <x; i++){<="" th=""></x;>                               |

|       | Compare (Signal k, reference i);                                   |

|       | If $(result = valid)$ {                                            |

|       | Output = fault pulse series;                                       |

|       | return;                                                            |

|       | }else{                                                             |

|       | New fault pulse series =Find nearest reference (Signal k);         |

|       | Output= New fault pulse series;                                    |

|       | }                                                                  |

|       | }                                                                  |

|       | }                                                                  |

Fig. 5 Pseudo-code for coordination system

Table 1

Distribution network parameters values

| Parameter          | Value             | Description              |

|--------------------|-------------------|--------------------------|

| Vs                 | 20,000 sin 314t V | electric sources voltage |

| ZLine1             | 0.2 + j0.314 Ω    | first line impedance     |

| Z <sub>Line2</sub> | 0.2 + j0.314 Ω    | second line impedance    |

| Z <sub>Line3</sub> | 0.1 + j0.155 Ω    | third line impedance     |

| Z <sub>Line4</sub> | 0.1 + j0.155 Ω    | fourth line impedance    |

| L <sub>DCR</sub>   | 0.3 H             | DC reactor inductance    |

| Z <sub>Load1</sub> | 200 + j100 Ω      | first load impedance     |

| Z <sub>Load2</sub> | 100 + j60 Ω       | second load impedance    |

| R <sub>Fault</sub> | 0.001 Ω           | fault resistance         |

| R <sub>S</sub>     | 0.1 Ω             | source resistance        |

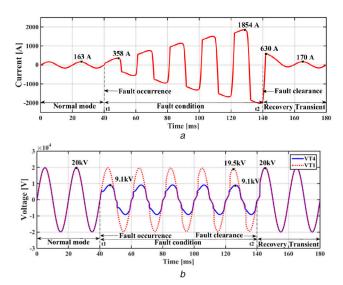

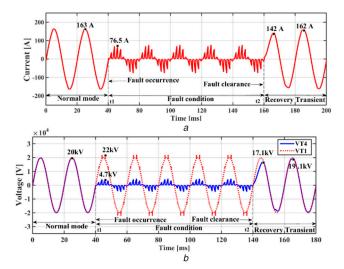

Fig. 6 Protection effect of uncontrolled DCR-FCL (a) First CT current with uncontrolled DCR-FCL effect, (b) First and fourth VT voltages with uncontrolled DCR-FCL effect

The faulty network has a fixed condition if the signal matches with one of the patterns. If the comparison result is valid, it means that the signal matches with one of the patterns, so the program continues to send the previous signal. Also if it is not, the program will run the method to find the nearest pattern. This method will search for a proper pattern to suit the network fault and put its signal into a new fault pulse series.

# 5 Simulation results

In this section, simulation analysis is carried out based on the proposed distribution network as shown in Fig. 1 where the line to ground fault occurs in the middle of lines 3–4. Simulation is performed using coordinated FCLs and their performance in the network. The distribution network is simulated in three states:

(a) Network protection by uncontrollable DCR-FCL.(b) Network protection by controllable DCR-FCL.

(c) Network protection by coordinated DCR-FCL.

The distribution network parameters are listed in Table 1. In this simulation, candidate signals for the measurement are voltage and current of sources 1 and 2 that are measured via VT1, VT3, CT1 and CT3 in buses 1 and 4. In addition, voltage and current signals of the loads 1 and 2 are measured via VT2, VT4, CT2, and CT4, respectively.

#### 5.1 Power grid protection by uncontrolled DCR-FCL

In this case, FCL is not controlled by an external signal while the electronic switch and the DC reactor inductance limit the fault current. The FCL delay is near zero and the magnitude of fault current is raised in each cycle. As shown in Fig. 6, the fault is occurred at t1 and is cleared at t2. The CT1 and VT1, four are candidate signals that are measured during the normal, fault and recovery transient states, respectively. Three examples of measurement are shown in Fig. 7. Fig. 6a shows the first source current in the grid. In the first source, the first peak of the fault current is limited but, after five cycles the current reaches to approximately ten-fold more increase than the nominal system current. This overcurrent influences the source and load voltages (Fig. 6b).

### 5.2 Power grid protection by controllable DCR-FCL

In this section, the proposed DCR-FCL becomes controllable by the aid of the IGBT switch. Each FCL and its local computer processor choose a fixed uncoordinated pattern to limit the fault current which gives time to DMC to make a coordinated decision. In this case, all DCR-FCLs operate in the instant of fault occurrence by approximately similar pattern and hence, protect the sources against the fault current and voltage sag as shown in Fig. 8. The switching pattern includes pulses that are applied to IGBT switches to limit the fault current to an acceptable level. This figure illustrates current and voltage during normal, fault and transient state. Fig. 8a shows the current candidate source in the network measured by CT1. It is clear that the source meets no peak of fault current. The magnitude of peak current declines to 76.5 A. The load and source voltages during normal, fault and recovery states as shown in Fig. 8b in order to VT1 and VT4 measured data. It is shown that in the fault state voltage of the source is saved but the voltage of the load declines to 4.7 kV.

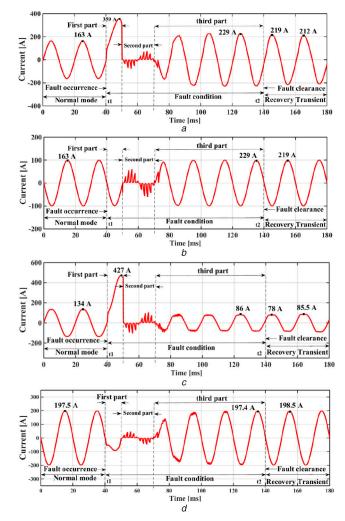

# 5.3 Network protection by coordinated DCR-FCL

DCR-FCL can control the fault current amplitude and it can also postpone the real maximum peak of the fault current. To improve the performance and reliability of the DCR-FCL, the IoT is used to coordinate FCLs in the computer network.

In the first part of distribution network protection, the DCR-FCL is operated in the instant of fault inception and the fault without any controlling command. Consequently, the current is limited by the DC reactor effect without any delay.

In the second part of the protection sequence, after half a cycle (10 ms), the local computer sends an appropriate pulse series with

IET Energy Syst. Integr., 2020, Vol. 2 Iss. 1, pp. 59-65

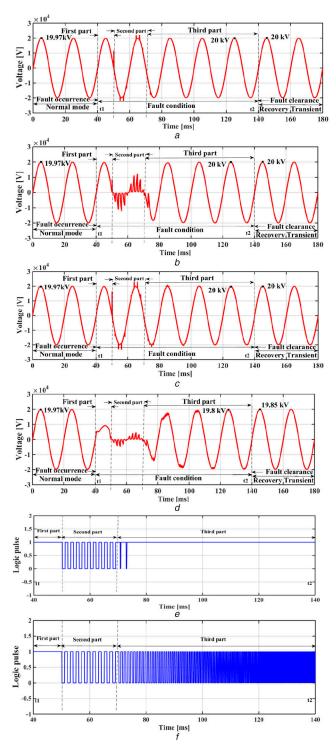

Fig. 7 VT voltage during fault and normal operation by IoT-based coordinated DCR-FCL

(a) First VT, (b) Second VT, (c) Third VT, (d) Fourth VT, (e) Series pulse of DCR-FCL in far distance of fault, (f) Series pulse of DCR-FCL in near distance of fault

the fixed pattern to DCR-FCL to limit fault current by controllable IGBT switch.

In the third part, coordination pulses are generated by DMS and it is sent via the communication network and IoT nodes. So the current limit value of each DCR-FCL has adjusted accordingly and all buses of the network will be saved. Generated pulse via DMC depends on the fault location in the network. It is supposed that fault has occurred in the middle of lines 3–4.

In Figs. 7 and 9 measured current and voltage of CTs and VTs are presented considering the three mentioned parts above.

According to the CT and VT measured data and delivered data to the DMC by IoT, intelligence analysis is done to generate the coordinated pulse series pattern for IGBTs. Figs. 9a and c show the

**Fig. 8** Protection effect of controlled uncoordinated DCR-FCL (a) First CT current, (b) First and fourth VT voltages

Fig. 9 *CT current with coordinated DCR-FCL* (*a*) First VT, (*b*) Second VT, (*c*) Third VT, (*d*) Fourth VT

first peak of the fault current of sources that is limited by the DCR-FCL inductance, where its value for both sources is <450 A. After limiting the first peak of the fault current via DC-reactor, the local decision and uncoordinated controlling pulses limit the fault current. Hence, DMC calls FCLs via IoT to coordinate the patterns. Finally, the source current is limited to the normal current of the power grid. Figs. 9*b* and *d* show the load current in all stages.

Fig. 7 depicts VTs voltage after a short period of first and second parts. As shown in these waveforms, the load and source

# IET Energy Syst. Integr., 2020, Vol. 2 Iss. 1, pp. 59-65

# Table 2 Distribution network parameters values

| Parameter          | Value                   | Description                             |

|--------------------|-------------------------|-----------------------------------------|

| Vs                 | 100 sin 314t            | voltage of the first and second sources |

| Z <sub>Line1</sub> | $0.2 + j0.314 \ \Omega$ | first line impedance                    |

| ZLine2             | $0.2 + j0.314 \ \Omega$ | second line impedance                   |

| Z <sub>Line3</sub> | 0.1 + j0.155 Ω          | third line impedance                    |

| Z <sub>Line4</sub> | 0.1 + j0.155 Ω          | fourth line impedance                   |

| LDCR               | 0.3 H                   | DC reactor inductance                   |

| Z <sub>Load1</sub> | 100 Ω                   | first load impedance                    |

| Z <sub>Load2</sub> | 60 Ω                    | second load impedance                   |

| R <sub>Fault</sub> | 0.001 Ω                 | fault resistance                        |

| R <sub>S</sub>     | 0.1 Ω                   | sources resistance                      |

|                    |                         |                                         |

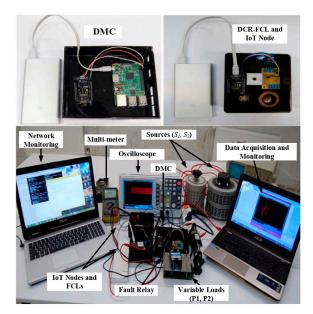

Fig. 10 Developed IoT-based protection system laboratory experimental setup ARM-based computer, and DCR-FCL

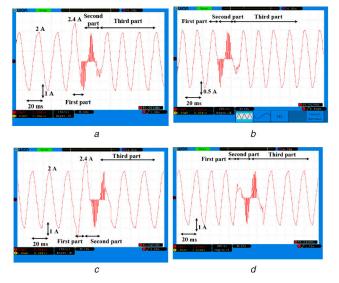

**Fig. 11** *Current signal during normal and fault states* (*a*) First source *S*<sub>1</sub>, (*b*) First load *P*<sub>2</sub>, (*c*) Second source *S*<sub>1</sub>, (*d*) Second load *P*<sub>2</sub> (Probe X1)

voltages are changed to the nominal value, while the power grid is successfully managed by coordinated DCR-FCLs.

Figs. 7e and f shows two pulse patterns in three explained cycles. Initially, the pulse value is one and IGBT is turned on. In the second part, the pulse has a fixed frequency and shows the fixed pattern of the local processor. The third part shows the

**Fig. 12** Voltage and logic pulse signal during normal and fault states (a) First source  $S_1$ , (b) Second source  $S_2$ , (c) First load  $P_1$ , (d) Second load  $P_2$ , (e) Pulse for DCR-FCL far from fault location, (f) Pulse for DCR-FCL near fault location (Probe X10)

coordinated series pulse, which directly depends on the position and distance of the FCL from the fault location.

# 6 Experimental results

A scaled down laboratory test setup is developed considering the distribution network presented in Fig. 1. The laboratory setup parameters are listed in Table 2 and the built prototype setup is shown in Fig. 10.

In this prototype, two variable transformers are used as the first and second electrical sources (S1, S2), the DC reactor consists of a toroid coil, full-bridge diode and IGBT switch and its driver are used as DCR-FCL which is connected to a Wi-Fi network by node MCU module. This module is programmed as a local processor computer and equipped the DCR-FCL with the IoT mechanism. The DMC is used as the DCR-FCL main processor and it is made by an ARM-based computer. The DCR-FCLs coordination and decision making to manage faults in the electrical system are the most important duties of this unit which is sequenced and arranged by database and data analysing. C and Python languages are used to create DMC. In this experimental network, two loads are fed that these loads introduced as first and second loads (P1, P2). In this prototype, the fault is modelled by a solid-state high current relay with  $0.01 \Omega$  resistance. This fault is controlled by the logical system and its duration is 100 ms. During a short circuit fault, the effect of IoT and DCR-FCL coordination is tested as well. The current and voltage waveforms are measured using a digital meter and data is transferred with IoT package. Measured data is monitored by the computer network and is used to obtain the status of the electrical system. The voltage and current waveforms are shown in Figs. 11 and 12, respectively. Figs. 11a and b show sources current and Figs. 11b and d illustrate load current which clearly verifies simulation results in Fig. 9.

In this experimental test, peak current of source in the normal state is approximately 1 A and after fault it experiences 1.5 A as first peak of fault current. After 30 ms current of sources and loads reaches to their normal value.

# IET Energy Syst. Integr., 2020, Vol. 2 Iss. 1, pp. 59-65

This is an open access article published by the IET and Tianjin University under the Creative Commons Attribution-NoDerivs License (http://creativecommons.org/licenses/by-nd/3.0/)

Figs. 12*a* and *c* show both sources voltage and Figs. 12*b* and *d* demonstrate the loads' voltage during normal and fault operation modes. The source voltage directly depends on it is current hence, by limiting the fault current, the source voltage is fixed to the nominal value. Using IoT and coordinated DCR-FCL, the source and load voltages are protected and fixed after two cycles. It is obviously shown that the voltage of the bus bar 1–4 is restored to normal voltage after coordination delay that it is <30 ms. The value of peak voltage after coordination reaches to 100 V. Also, current loads and sources do not see fault current and its value restore after DCR-FCL coordinated operation. The local processor and DMC generated pulses are shown in Figs. 12*e* and *f*. Illustrated experimental signal is in fair agreement with the simulation results presented in Fig. 7.

# 7 Conclusion

In this paper, a smart protection system based on coordinated FCLs is proposed, developed and implemented. The protection strategy relies on the IoT and decision-making centre which provide a reliable mechanism to coordinate all FCLs in the network. Each DCR-FCL employs the local processor to react against the fault quickly and receive sending data from the decision-making centre to act as a coordinated FCL. The simulation and experimental results show that the coordinated DCR-FCL manages faults in a decent manner. Therefore, it is a successful method to increase the quality of supply for available sensitive loads. The next important achievement of the proposed coordinated DCR-FCLs is power flow management in the fault conditions as well as load voltage recovery, which successfully provides high reliability during fault conditions.

#### 8 References

- Hob, A., Krämer, S., Elschner, S., et al.: 'Superconducting fault current limiters – a new tool for the grid of the future'. CIRED 2012 Workshop: Integration of Renewables into the Distribution Grid, Lisbon, May 2012, pp. 1–4

- [2] Bock, J., Hob, A., Schramm, J., et al.: 'Resistive superconducting fault current limiters are becoming a mature technology', *IEEE Trans. Appl. Supercond.*, 2015, 25, (3), pp. 1–4

- [3] Moscrop, J., Darmann, F.: 'Design and development of a 3-phase saturated core high temperature superconducting fault current limiter'. Int. Conf. on Electric Power and Energy Conversion Systems, Sharjah, United Arab Emirates, 2009, pp. 1–5

[4] Lee, B.W., Park, K.B., Sim, J., et al.: 'Design and experiments of novel

- [4] Lee, B.W., Park, K.B., Sim, J., et al.: 'Design and experiments of novel hybrid type superconducting fault current limiters', *IEEE Trans. Appl. Supercond.*, 2008, 18, (2), pp. 624–627

- [5] Arai, H., Inaba, M., Ishigohka, T., et al.: 'Fundamental characteristics of superconducting fault current limiter using LC resonance circuit', *IEEE Trans. Appl. Supercond.*, 2006, 16, (2), pp. 642–645

[6] Heidary, A, Radmanesh, H., Rouzbehi, K., et al.: 'A DC-reactor based solid-

- [6] Heidary, A, Radmanesh, H., Rouzbehi, K., et al.: A DC-reactor based solidstate fault current limiter for HVDC applications', *IEEE Trans. Power Deliv.*, 2019, 34, (2), pp. 720–728

- [7] Heidary, A., Radmanesh, H., Fathi, H., et al.: 'Series transformer based diodebridge-type solid state fault current limiter', Front. Inf. Technol. Electron. Eng., 2015, 16, (9), pp. 769–784

- Yamaguchi, H., Kataoka, T.: 'An experimental investigation of magnetic saturation of a transformer type superconducting fault current limiter', *IEEE Trans. Appl. Supercond.*, 2009, **19**, (3), pp. 1876–1879

Cvoric, D., de Haan, S.W.H., Ferreira, J.A.: 'New saturable-core fault current

- [9] Cvoric, D., de Haan, S.W.H., Ferreira, J.A.: 'New saturable-core fault current limiter topology with reduced core size'. 2009 IEEE 6th Int. Power Electronics and Motion Control Conf., Wuhan, China, May 2009

- [10] Cvoric, D., de Haan, S.W.H., Ferreira, J.A.: 'Improved configuration of the inductive core-saturation fault current limiter with the magnetic decoupling'. 2008 IEEE Industry Applications Society Annual Meeting, Edmonton, AB, Canada, October 2008

- [11] Yuan, J., Lei, Y., Wei, L., et al.: 'A novel bridge-type hybrid saturated-core fault current limiter based on permanent magnets', *IEEE Trans. Magn.*, 2015, 51, (11), pp. 1–4

- [12] Knott, J.C., Moscrop, J.W.: 'Increasing energy efficiency of saturated-core fault current limiters with permanent magnets', *IEEE Trans. Magn.*, 2013, 49, (7), pp. 4132–4136

- [13] Hoshino, T., Salim, K.-M., Nishikawa, M., et al.: 'DC reactor effect on bridge type superconducting fault current limiter during load increasing', *IEEE Trans. Appl. Supercond.*, 2001, **11**, (1), pp. 1944–1947

- [14] Mutaa, I., Hoshinoa, T., Salima, K.M., et al.: 'Proposal of DC shield reactor type superconducting fault current limiter', Cryogenics, 2004, 44, (3), pp. 177–182

- [15] Zhao, Y., Saha, T.K., Krause, O., et al.: 'Current limiting impedance comparison between different designs of iron cores of the flux-lock-type superconducting fault current limiter', *IET Gener. Transm. Distrib.*, 2016, 10, (2), pp. 548–554

- [16] Sadeghi, M.H., Damchi, Y., Shirani, H.: 'Improvement of operation of power transformer protection system during sympathetic inrush current phenomena using fault current limiter', *IET Gener. Transm. Distrib.*, 2018, **12**, (22), pp. 5968–5974

- [17] Zheng, F., Deng, C., Chen, L., et al.: 'Transient performance improvement of micro-grid by a resistive superconducting fault current limiter', *IEEE Trans. Appl. Supercond.*, 2015, 25, (3), pp. 1–5

- [18] Radmanesh, H., Heidary, A., Fathi, S.H., et al.: 'Dual function ferroresonance and fault current limiter based on DC reactor', *IET Gener. Transm. Distrib.*, 2016, 10, (9), pp. 2058–2065

- [19] Hamman, S.T., Hopkinson, K.M., Fadul, J.E.: 'A model checking approach to testing the reliability of smart grid protection systems', *IEEE Trans. Power Deliv.*, 2016, **32**, (6), pp. 2408–2415

- [20] Atzori, L., Iera, A., Morabito, G.: 'The internet of things: a survey', *Comput. Netw.*, 2010, 54, pp. 2787–2805

[21] Xu, L.D., He, W., Li, S.: 'Internet of things in industries: a survey', *Trans.*

- [21] Xu, L.D., He, W., Li, S.: 'Internet of things in industries: a survey', *Trans. Indus. Inf.*, 2014, 10, (4), pp. 2233–2243

[22] Li, Y., Hou, M., Liu, H., *et al.*: 'Towards a theoretical framework of strategic

- [22] Li, Y., Hou, M., Liu, H., et al.: 'Towards a theoretical framework of strategic decision, supporting capability and information sharing under the context of IoT', *Inf. Technol. Manag.*, 2012, **13**, (4), pp. 205–216

- [23] Abdolkarimzadeh, M., Nazari-Heris, M., Abapour, M., et al.: 'A bridge-type fault current limiter for energy management of AC/DC microgrids', *IEEE Trans. Power Electron.*, 2017, 32, (12), pp. 9043–9050

- Trans. Power Electron., 2017, 32, (12), pp. 9043–9050

[24] Ghaemi, S., Abapour, M.: 'Effect of fault current limiter (FCL) on reliability and protection coordination of distribution system'. 2016 24th Iranian Conf. on Electrical Engineering (ICEE), Shiraz, Iran, 2016

- [25] Heidary, A., Radmanesh, H., Bakhshi, A., et al.: 'A compound current limiter and circuit breaker', *Electronics. (Basel)*, 2019, 8, (5), p. 551

- [26] Heidary, A., Radmanesh, H., Moghim, A., et al.: 'A multi-inductor H bridge fault current limiter', *Electronics. (Basel)*, 2019, 8, p. 795

[27] Gomathi, S., Venkatesan, T., Sri Vidhya, D.: 'Design and implementation of

- [27] Gomathi, S., Venkatesan, T., Sri Vidhya, D.: 'Design and implementation of fault current limiters in distribution system using internet of things', *Wirel. Pers. Commun.*, 2018, **102**, (4), pp. 2643–2666

- [28] Tan, L., Wang, N.: 'Future internet: the internet of things'. Proc. of the 3rd Int. Conf. on Advanced Computer Theory and Engineering (ICACTE), Chengdu, China, 2010, pp. 376–380

- [29] Arai, K., Tanaka, H., Inaba, M., et al.: 'Test of resonance-type superconducting fault current limiter', *IEEE Trans. Appl. Supercond.*, 2006, 16, (2), pp. 650–653