"© 2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works."

# Qubit Mapping Based on Subgraph Isomorphism and Filtered Depth-Limited Search

Sanjiang Li, Xiangzhen Zhou, Yuan Feng

**Abstract**—Mapping logical quantum circuits to Noisy Intermediate-Scale Quantum (NISQ) devices is a challenging problem which has attracted rapidly increasing interests from both quantum and classical computing communities. This paper proposes an efficient method by (i) selecting an initial mapping that takes into consideration the similarity between the architecture graph of the given NISQ device and a graph induced by the input logical circuit; and (ii) searching, in a filtered and depth-limited way, a most useful SWAP combination that makes executable as many as possible two-qubit gates in the logical circuit. The proposed circuit transformation algorithm can significantly decrease the number of auxiliary two-qubit gates required to be added to the logical circuit, especially when it has a large number of two-qubit gates. For an extensive benchmark set of 131 circuits and IBM's current premium Q system, viz., IBM Q Tokyo, our algorithm needs, in average, 0.4346 extra two-qubit gates per input two-qubit gate, while the corresponding figures for three state-of-the-art algorithms are 0.6047, 0.8154, and 1.0067 respectively.

Index Terms—NISQ, quantum circuit transformation, qubit mapping, subgraph isomorphism, heuristic search.

# **1** INTRODUCTION

C INCE Shor's exciting quantum algorithms for solving Dinteger factorization and discrete logarithm [1], many quantum algorithms have been proposed that could offer an exponential speed-up when compared with best classical algorithms. These include in particular the HHL algorithm for solving systems of linear equations [2] and other machine learning algorithms derived from HHL (cf. [3] for a summary). Typically, the implementation of these algorithms requires quantum computers with millions of qubits which are perhaps still not available in the next two decades. On the other hand, IBM, Intel and Google have all announced their quantum devices with around 50-70 qubits recently. The Noisy Intermediate-Scale Quantum (NISQ) era seems coming in reality. Despite that quantum error correction is not yet available in the near future, quantum supremacy is recently demonstrated in Google's 53-qubit quantum processor Sycamore [4].

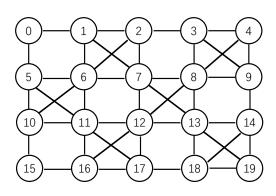

There is yet another gap between theoretical research on quantum algorithms and their implementation on realistic quantum devices. When designing quantum algorithms, typically, the quantum circuit model allows multi-qubit gates to act on any set of qubits without restriction. This is, however, not the case in realistic NISQ devices, which have "limited number of qubits, limited connectivity between qubits, restricted (hardware-specific) gate alphabets, and limited circuit depth due to noise" [5]. In the superconducting devices of IBM, Google, and Rigetti, only single and special two-qubit gates (like CNOT or CZ) are supported. Even worse, these two-qubit gates can only be implemented between neighbouring qubits. For example, Fig. 1 shows the

Fig. 1. The architecture graphs for IBM Q Tokyo.

architecture graph of IBM's current premium quantum system IBM Q Tokyo (also known as IBM Q20), which supports elementary single-qubit gates and two-qubit CNOT gates and a CNOT gate can be implemented only between qubits which are connected by an (undirected) edge. In order to use these NISQ devices, the desired quantum functionality in an ideal quantum circuit should be *transformed* or *mapped* so that the underlying coupling constraints imposed by these quantum devices are satisfied.

More precisely, in order to implement an ideal quantum circuit on an NISQ device like IBM Q Tokyo, we need to address two issues. The first is to decompose the desired functionality (arbitrary quantum gates) into elementary operations that can be directly applied on the NISQ device. This issue has already been properly addressed in several works [6], [7], [8]. The second issue, known as *qubit mapping* or *circuit transformation*, is to map or route the qubits in the ideal quantum circuit to qubits of the quantum device so that the coupling constraints imposed by the quantum device are satisfied and thus the two-qubit gates in the ideal quantum circuit are executable.

Sanjiang Li and Yuan Feng are with Centre for Quantum Software and Information (QSI), Faculty of Engineering and Information Technology, University of Technology Sydney, NSW 2007, Australia. E-mail: {sanjiang.li, yuan.feng}@uts.edu.au

Xiangzhen Zhou is with State Key Lab of Millimeter Waves, Southeast University, Nanjing 211189, China and Centre for Quantum Software and Information, University of Technology Sydney, NSW 2007, Australia.

In the past several years, the qubit mapping problem has attracted rapidly increasing interests from both classical and quantum computing communities, see, e.g., [9], [10], [11], [12], [13], [14], [15], [16], [17], [18] and references therein. Given an arbitrary quantum circuit and an NISQ device, the task of qubit mapping is to construct automatically a quantum circuit with the same functionality which can be immediately implemented in the NISQ device. For ease of presentation, we call an arbitrary quantum circuit a logical circuit and call a circuit that is implementable in the NISQ device a physical circuit. Similarly, we call qubits in a logical (physical) circuit logical (physical) qubits. We assume that gates in the input logical circuit are already decomposed into elementary gates supported by the NISQ device. In particular, each gate in the logical circuit involves at most two qubits. Naturally, we also assume that the number of logical qubits is not larger than the number of physical qubits.

It is not difficult to find such a solution for an input logical circuit. Indeed, we can start with an arbitrary initial mapping and then execute one two-qubit gate per round (note single-qubit gates can be executed directly) by inserting several SWAP operations to transform the current mapping to a mapping that can execute the current twoqubit gate. The challenge lies in that if we can find a solution with minimal overhead in terms of the number of auxiliary SWAP gates added. This is crucial for the success of quantum computing as a large number of extra two-qubit gates will significantly accumulate the error of the output physical circuit.

Finding an optimal solution for the qubit mapping problem is often very difficult. Indeed, it is NP-complete [11] to decide if an input logical circuit can be transformed into an equivalent physical circuit using up to k SWAP gates for a fixed integer k > 0. Several previous works use offthe-shelf tools like dynamic programming [11], SAT solvers [10], temporal planners [12], Integer Linear Programming (ILP) [19], satisfiability modulo theory (SMT) solvers [13]. In worst cases, all these approaches take time exponential in the number of qubits.

Many other works devise specialised heuristic search algorithms for solving the qubit mapping problem. For example, Zulehner, Paler and Wille [14] partition the input logical circuit into layers and introduce an  $A^*$  search algorithm. When combined with a lookahead scheme and a dedicated method for selecting the initial mapping, their algorithm performs much better than IBM's own solution. However, this  $A^*$  algorithm also takes time exponential in the number of qubits. Li, Ding and Xie [15] propose a search algorithm based on reverse traversal, which is polynomial in the number of qubits and works very well for small circuits with less than a hundred two-qubit gates. Their algorithm, called SABRE, outperforms the  $A^*$ -approach [14] with exponential speedup and comparable or better results on various benchmarks. Childs, Schoute and Unsal [16] also propose efficient methods that attempt to minimise the circuit depth or size overhead and have worst-case time complexity polynomial in the sizes of the input circuit and the architecture graph. To this end, they decompose the problem into two subproblems: qubit movement and qubit placement. The first subproblem concerns how to transform the current

mapping to a selected next mapping by imposing SWAP gates on edges in the architecture graph, while the second subproblem gives method to compute the next mapping. In another work, Cowtan et al. [17] describe a solution implemented in the platform-independent compiler  $t|ket\rangle$ . They also partition the input circuit into layers and then select the SWAP which can maximally reduce the diameter of the subgraph composed of all pairs of qubits in the current layer. We address their algorithm as the Cambridge algorithm henceforth. In [18], we designed a new qubit mapping algorithm, called SAHS in this paper, which uses simulated annealing for constructing an initial mapping and searches the next mapping by using a heuristic function that reflects the variable influence of gates in different layers. Empirical results showed that SAHS outperforms both SABRE and the Cambridge algorithm by a large margin. Initial mappings of SAHS are, however, computed non-deterministically by simulated annealing, which is sometimes unstable and runs slowly when the circuit size is large [18].

In this paper, we propose a new search algorithm based on subgraph isomorphism and filtered depth-limited search. The idea is to construct a graph G from the input circuit which is isomorphic to a subgraph of  $\mathcal{AG}$ , the architecture graph of the given NISQ device, and select any embedding from G to  $\mathcal{AG}$  as the initial mapping. Starting from this initial mapping, we then, step by step, construct the physical circuit while removing executable gates from the logical circuit. If the current mapping can execute some gates in the front layer of the logical circuit, we remove them from the logical circuit and properly append them to the current physical circuit; if there are no executable gates in the front layer, then we need to insert SWAP gates and obtain a new mapping so that some two-qubit gates in the front layer can be executed. To select a good next mapping, we tend to exhaustively search all possible combinations of SWAP operations such that the number of executable twoqubit gates per SWAP is maximised. As selecting the best SWAP combination is expensive, we set up a fixed limit k > 0 and only consider combinations of at most k SWAPs. The search process could be further sped up if we 'filter' those SWAPs which do not interact with gates in the front layers of the circuit. Such filters are designed and used in our algorithm. While less efficient when compared with SABRE, our algorithm is, if neglecting not considering the time for computing the initial mapping, still polynomial in all relevant parameters and can significantly reduce the number of SWAPs required to transform the input logical circuit. Indeed, empirical evaluation shows that our algorithm can often reduce by half the number of SWAPs required when compared with SABRE, if the input logical circuit has hundreds or more two-qubit gates. Similar empirical evaluations also show that our algorithm is significantly better than the Cambridge algorithm developed by Cowtan et al. [17] and our SAHS algorithm [18] in terms of the size of the output circuits, when no postmapping optimisation is used.

The remainder of this paper is organised as follows. In Section 2, we recall some background of quantum computation and quantum circuits, and describe and analyse our algorithm in Section 3. Detailed empirical evaluation is reported in Section 4. The last section concludes the paper with discussions on directions for future research.

#### 2 BACKGROUNDS

In this section, after a brief introduction of quantum gates and quantum circuits, we describe the dependency graph associated to a logical circuit and show how to partition the logical circuit into layers by using the dependency graph.

# 2.1 Quantum Gates and Quantum Circuits

Qubit is the counterpart of bit in quantum computation. While a 'classical' bit can only be in one of two states, viz., 0 and 1, a qubit can be in the superposition state  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$  of the two basis states,  $|0\rangle$  and  $|1\rangle$ , where  $\alpha, \beta \in \mathbb{C}$  are probability amplitudes satisfying  $|\alpha|^2 + |\beta|^2 = 1$ . For example,  $|+\rangle = \frac{1}{\sqrt{2}}(|0\rangle + |1\rangle)$  and  $|-\rangle = \frac{1}{\sqrt{2}}(|0\rangle - |1\rangle)$  are two superposition states. The success of quantum computation partially lies in ingenious use of quantum superposition.

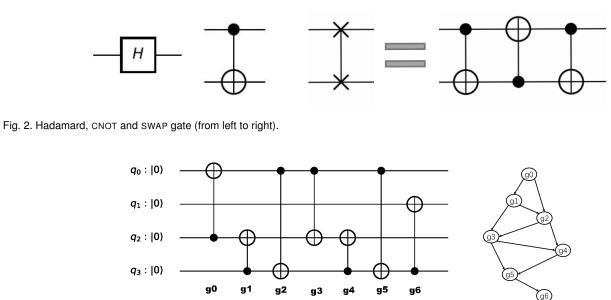

Quantum computation is realised by applying quantum gates on qubits. Complex, multi-qubit gates can be decomposed into elementary single or two-qubit gates. In fact, any quantum gate can be approximated to arbitrary accuracy using a fixed set of single-qubit gates and CNOT gates [20]. Fig. 2 illustrates three very useful gates: Hadamard gate H, CNOT gate and SWAP gate. Hadamard gate is a singlequbit gate which can evenly mix the basis states to produce a superposed one. Precisely, H maps  $|0\rangle$  to  $|+\rangle$  and  $|1\rangle$  to  $|-\rangle$ . CNOT and SWAP are both two-qubit gates, i.e., they operate on two qubits. A CNOT gate flips the target qubit (indicated graphically with  $\oplus$ ) if and only if the control qubit (indicated graphically with a black dot •) is in state  $|1\rangle$ , while a SWAP gate exchanges the states of the two qubits operated. Precisely, CNOT maps  $|a\rangle |b\rangle$  to  $|a\rangle |a \oplus b\rangle$ and SWAP maps  $|a\rangle |b\rangle$  to  $|b\rangle |a\rangle$  for  $a, b \in \{0, 1\}$ . Most NISQ devices do not support SWAP gates directly and, if this is the case, we may implement a SWAP gate by three CNOT gates (see Fig. 2 (right)).

Quantum circuits are the most commonly used model to describe quantum algorithms, which consist of input qubits, quantum gates, measurements and classical registers [21]. As only input qubits and quantum gates are relevant in the qubit mapping problem, in this paper, we represent a quantum circuit simply as a pair (Q, C), where Q is the set of involved qubits and *C* a sequence of quantum gates.

#### 2.2 Dependency Graph and Front Layer

Two-qubit gates in a logical circuit LC = (Q, C) are not independent in general. We say a two-qubit gate  $g_1$  depends on another two-qubit gate  $g_2$  if the latter must be executed before the former. This happens when  $g_2$  is in front of  $g_1$  in *C* and they share a common qubit, or when  $g_1$  depends on a two-qubit gate  $g_3$  which depends on  $g_2$ . For clarity, we say  $g_1$  directly depends on  $g_2$  if  $g_2$  is in front of  $g_1$  in C and they share a common point and there are no other gates between them which share the same common point.

For a logical circuit LC = (Q, C), we construct a directed acyclic graph (DAG), called the dependency graph, to characterise the direct dependency between two-qubit gates in LC [15], [16]. Each node of the dependency graph

3

represents a two-qubit gate and each directed edge the direct dependency relationship from one two-qubit gate to another. The front layer of *LC*, denoted  $\mathcal{F}(LC)$  or  $\mathcal{L}_0(LC)$ , consists of all two-qubit gates in *LC* which have no parents in the dependency graph. The second layer  $\mathcal{L}_1(LC)$  is then the front layer of the circuit obtained from *LC* by deleting all gates in  $\mathcal{F}(LC)$ . Analogously, we can define the k-th layer  $\mathcal{L}_k(LC)$  of LC for all  $k \ge 0$ .

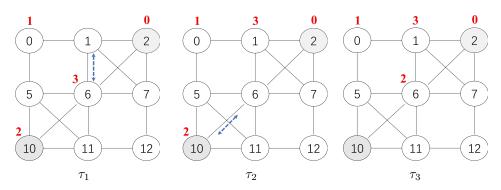

**Example 1.** Consider the logical circuit LC = (Q, C) shown in Fig. 3 (left), where

$$\begin{aligned} Q &= \{q_0, q_1, q_2, q_3\}, \\ C &= (g_0 \equiv \langle q_2, q_0 \rangle, g_1 \equiv \langle q_3, q_2 \rangle, g_2 \equiv \langle q_0, q_3 \rangle, g_3 \equiv \langle q_0, q_2 \rangle, \\ g_4 &\equiv \langle q_3, q_2 \rangle, g_5 \equiv \langle q_0, q_3 \rangle, g_6 \equiv \langle q_3, q_1 \rangle), \end{aligned}$$

where  $\langle q_2, q_0 \rangle$ , for example, denotes the CNOT gate in the logical circuit with  $q_2$  being the control qubit and  $q_0$  the target.

For this circuit, we have  $\mathcal{F}(LC) = \{g_0\}, \mathcal{L}_1(LC) = \{g_1\},\$  $\mathcal{L}_2(LC) = \{g_2\}$ , and  $\mathcal{L}_3(LC) = \{g_3\}$ , and so on. From the dependency graph (showing in Fig. 3 (right)), we can see that, for example, gate  $g_2$  can be executed only after  $g_0$  and  $g_1$ .

# **3** THE PROPOSED APPROACH

The main objective of qubit mapping is to transform an input logical circuit to a physical one with minimal size or depth so that the constraints imposed by the NISQ device are satisfied. To simplify the discussion, we only consider the connectivity constraints for two-qubit gates as specified by the architecture graph. This means that single-qubit gates have no effect in the circuit transformation process. Furthermore, we make the following assumptions:<sup>1</sup>

- The NISQ device supports all single-qubit gates and 1) CNOT gates;

- The architecture graph of the NISQ device,  $\mathcal{AG}$ , is 2) an undirected graph;

- CNOT gates are the only two-qubit gates in the input 3) logical circuit.

From now on and as in Example 1, we write a CNOT gate simply as a pair  $\langle q, q' \rangle$ , where q is the control qubit and q' is the target qubit. We call the CNOT gate  $\langle q', q \rangle$  the *inverse* of  $\langle q, q' \rangle$ .

Let  $\mathcal{AG} = (V, E)$  be the undirected architecture graph of the NISQ device we are given, where V is the set of physical qubits and E the set of edges along which CNOT gates can be performed. Recall that an edge e in an undirected graph is an unordered pair of the two endnodes p, q of e. In the following, we write *e* simply by  $\{p, q\}$ , i.e., the set of its two endnodes.

Let LC = (Q, C) be a logical circuit with |Q| < |V|. Suppose C consists of only CNOT gates after removing all single-qubit gates. We need to construct a physical circuit  $PC = (V, C^p)$  which contains only CNOT gates, is functionally equivalent to LC after adding back all single-qubit gates accordingly, and respects the connectivity constraints imposed by  $\mathcal{AG}$ , i.e., for any CNOT gate  $\langle q,q'

angle$  in  $C^p$ , we have  $\{q, q'\} \in E$ .

1. The occurrences of CNOT gates may be replaced by CZ gates when, e.g., a Rigetti device is used.

Fig. 3. A logical quantum circuit with only CNOT gates (left) and its dependency graph (right).

It is easy to find a physical circuit that satisfies the above conditions, but the real challenge is to find one with *minimal* size or depth, which is NP-hard in general [11]. In this paper, we modify the input logical circuit stepwise by inserting auxiliary SWAP operations (each implemented with three CNOT gates as in Fig. 2 (right)) until the logical circuit is transformed into a physical circuit that can be executed on the NISQ device. To evaluate the effectiveness of qubit mapping algorithms, we use the sizes of the output circuits, i.e., the total number of its two-qubit gates.

# 3.1 Qubit Mapping

In each step, qubits in the logical circuit are mapped or allocated to physical qubits in the NISQ device. Mathematically, a (partial) qubit mapping is a (partial) function  $\tau$  from Qto V such that  $\tau(q) = \tau(q')$  if and only if q = q' for any  $q, q' \in Q$ . We say a partial qubit mapping is *complete* if it is defined for every q in Q. A physical qubit v is *occupied* if  $\tau$  maps some logical qubit q to v. If otherwise, we say v is unoccupied. The mapping may change in consecutive steps of the transformation which is determined by the inserted auxiliary SWAP operations.

Given a logical circuit *LC* and a mapping  $\tau$ , a CNOT gate  $g = \langle q, q' \rangle$  in *LC* is said to be *satisfied* by  $\tau$ , or  $\tau$  satisfies g, if  $\{\tau(q), \tau(q')\}$  is an edge in *AG*. Furthermore, g is *executable* by  $\tau$  if it appears in the front layer of *LC* and  $\tau$  satisfies g. If this is the case, we remove g from *LC* and append a CNOT gate  $\tau(g) := \langle \tau(q), \tau(q') \rangle$  to the end of the physical circuit. This process is called the *execution* of g.

For two physical qubits v, v' in  $\mathcal{AG}$ , we write  $dist_{\mathcal{AG}}(v, v')$  for the distance (i.e., the length of a shortest path) from v to v' in  $\mathcal{AG}$ .

For any mapping  $\tau$  and any two-qubit gate  $g = \langle q, q' \rangle$ , the *physical distance* between the two qubits q, q' in g under mapping  $\tau$ , written dist<sub>ph</sub> $(q, q', \tau)$ , is defined as

- the distance between  $\tau(q)$  and  $\tau(q')$  in  $\mathcal{AG}$ , i.e., dist<sub> $\mathcal{AG}$ </sub>( $\tau(q), \tau(q')$ ), if both  $\tau(q)$  and  $\tau(q')$  are defined,

- the shortest distance between  $\tau(q)$  or  $\tau(q')$  to all unoccupied physical qubits if only one of  $\tau(q)$  and  $\tau(q')$  is defined, and

- the shortest distance between two unoccupied qubits if neither  $\tau(q)$  nor  $\tau(q')$  is defined.

Apparently, a gate  $g = \langle q, q' \rangle$  in the front layer is executable by  $\tau$  (after possible extension if  $\tau$  is incomplete) iff the physical distance between q and q' under  $\tau$  is 1.

**Example 2** (Example 1 cont'd). Consider the logical circuit *LC* shown in Fig. 3. Let  $\tau_1 : Q \to V$  be the mapping specified by  $\tau_1(q_0) = v_2, \tau_1(q_1) = v_0, \tau_1(q_2) = v_{10}, \tau_1(q_3) = v_6$ , see Figure 4 (left). Then, because  $\tau_1(q_2) = v_{10}$  and  $\tau_1(q_0) = v_2$  and  $dist_{AG}(v_2, v_{10}) = 2$ , we can see that  $g_0 \equiv \langle q_2, q_0 \rangle$  is not executable by  $\tau_1$  in IBM Q Tokyo. However, for the mapping  $\tau_3$  shown in Figure 4 (right),  $g_0$  is executable by  $\tau_3$  and, indeed, every gate in *LC* is satisfied by  $\tau_3$ .

# 3.2 Initial Mapping

An initial mapping can be constructed step by step or selected arbitrarily or computed from a dedicated subroutine. Zulehner et al. [14] tested both arbitrary initial mappings and initial mappings evolved from an empty mapping. Their experimental evaluation shows that, in general, the latter approach has better performance. In [15], Li et al. proposed to use an initial mapping that takes the whole input circuit into consideration. Starting from a randomly generated mapping  $\tau_0$ , they first take this mapping as the initial mapping and apply it on the input circuit (Q, C), the obtained final mapping  $\tau_1$  is then used as the initial mapping and applied to the inverse circuit<sup>2</sup>  $(Q, C^{inv})$ , and lastly, the obtained final mapping  $\tau_f$  is selected as the initial mapping for their main algorithm SABRE. Their approach is demonstrated as consistently better than the  $A^*$  search algorithm in [14]. In [18], we proposed SAHS, which uses

<sup>2.</sup> Note the "inverse" here has a different meaning as the "inverse" CNOT gate defined in page 3.

Fig. 4. Qubit mappings  $\tau_i : \{q_0, q_1, q_2, q_3\} \rightarrow V$  for i = 1, 2, 3, where  $\tau_2$  is obtained from  $\tau_1$  by SWAP(1,6) and  $\tau_3$  is obtained from  $\tau_2$  by SWAP(6,10), where SWAP(1,6) is a shorthand for SWAP( $v_1, v_6$ ).

simulated annealing to search for the best initial mapping that fits well with the input logical circuit and empirical evaluation there shows that, when compared with the naive mapping that sends  $q_i$  to  $v_i$ , SAHS works significantly better with the initial mapping obtained by simulated annealing.

In this section we show how to obtain a good initial mapping by matching a particular graph induced by the input circuit with the architectural graph.

Suppose LC = (Q, C) is the input logical circuit. We first construct an undirected graph  $\mathcal{G}_{circ}(C) = (Q, E_{circ})$  on Q, where  $\{q, q'\}$  is an edge in  $E_{circ}$  if either  $\langle q, q' \rangle$  or its inverse  $\langle q', q \rangle$  is in C. If  $\mathcal{G}_{circ}(C)$  happens to be isomorphic to a subgraph of the architecture graph  $\mathcal{AG}$ , then the qubit mapping problem is solved by constructing an (arbitrary) isomorphic embedding  $\tau$  from  $\mathcal{G}_{circ}(C)$  to  $\mathcal{AG}$ . For NISQ devices, which have up to several thousands qubits, this can be solved by, for example, the VF2 algorithm [22]. If  $\mathcal{G}_{circ}(C)$  is not isomorphic to a subgraph of  $\mathcal{AG}$ , then we may select a maximal sub-circuit  $C_{top}$  of C such that

- (i) C<sub>top</sub> is a front section of C = {g<sub>i</sub> ∈ C | 1 ≤ i ≤ n} w.r.t. the dependency graph of C, i.e., a two-qubit gate g<sub>i</sub> is in C<sub>top</sub> only if all two-qubit gates g<sub>j</sub> on which g<sub>i</sub> depends are in C<sub>top</sub>;

- (ii) the graph  $\mathcal{G}_{circ}(C_{top})$  is isomorphic to a subgraph of  $\mathcal{AG}$ ; and

- (iii) the graph G<sub>circ</sub>(C<sub>top</sub> ∪ {g<sub>i\*</sub>}) is not isomorphic to a subgraph of AG for any g<sub>i\*</sub> that is in the front layer of C \ C<sub>top</sub>.

We call  $\mathcal{G}_{circ}(C_{top})$  a top subgraph (topgraph for short) of  $\mathcal{G}_{circ}(C)$ . Let  $\tau_{top}$  be an isomorphic embedding from  $\mathcal{G}_{circ}(C_{top})$  to  $\mathcal{AG}$ . We select  $\tau_{top}$  as the initial mapping, which satisfies all gates in  $C_{top}$ . Note that  $\tau_{top}$  might not be a complete mapping from Q to V.

**Example 3** (Example 1 cont'd). For the circuit LC in Example 1, we have  $Q = \{q_0, q_1, q_2, q_3\}$  and  $E_{circ} = \{\{q_0, q_2\}, \{q_0, q_3\}, \{q_2, q_3\}, \{q_1, q_3\}\}$ . Clearly,  $\mathcal{G}_{circ}(C)$  is isomorphic to a subgraph of  $\mathcal{AG}$  and such an isomorphism is specified by the qubit mapping  $\tau_3$  in Fig. 4 (right).

Note that  $\tau_{top}$  often does not take the whole circuit into consideration. We propose another method for constructing the initial mapping that considers the whole circuit. For a logical circuit LC = (Q, C), we introduce a weight function  $\omega$  which assigns a weight on each edge of  $E_{circ}$  (the edge set

of the undirected graph  $\mathcal{G}_{circ}(C)$  defined above) such that  $\omega(\{q,q'\})$  is the number of gates  $g_i$  in C with  $g_i = \langle q,q' \rangle$ or  $g_i = \langle q', q \rangle$ . Let  $E^w_{\text{circ}} = \{e_1, e_2, ..., e_n\}$  where  $\omega(e_1) \geq \omega(e_1)$  $\ldots \geq \omega(e_n)$ . We then construct a subgraph  $\mathcal{G}^* = (Q, E^*)$  of  $\mathcal{G}_{circ}(C)$  which is isomorphic to a subgraph of  $\mathcal{AG}$  as follows. We start by letting  $E^* = \{e_1\}$  and then consider the next edge  $e_2$ . In general, suppose we have decided if  $e_i$  should be put into  $E^*$  or not for all i < k for some  $k \leq n$  and the current subgraph  $\mathcal{G}^*$  is isomorphic to some subgraph of  $\mathcal{AG}$ . We consider  $e_{i+1}$ . If putting  $e_{i+1}$  into  $E^*$  will make  $\mathcal{G}^*$  non-isomorphic to any subgraph of  $\mathcal{AG}$ , we skip this edge; otherwise, we put  $e_{i+1}$  into  $E^*$  and update  $\mathcal{G}^*$ , which is still isomorphic to some subgraph of  $\mathcal{AG}$ . If i + 1 < n, we continue to consider  $e_{i+2}$  till there is no edge left in  $E^w_{\text{circ}}$ . In this way, we obtain a subgraph  $\mathcal{G}^*$  of  $\mathcal{G}_{\text{circ}}(C)$  that is isomorphic to some subgraph of  $\mathcal{AG}$ . The sum of weights of edges in  $\mathcal{G}^*$ , though not necessary the largest, is sufficiently large among all subgraphs of  $\mathcal{G}_{circ}(C)$  that are isomorphic to some subgraph of  $\mathcal{AG}$ . Using the VF2 algorithm, we can find an embedding  $\tau_{wgt}$  which embeds  $\mathcal{G}^*$  into  $\mathcal{AG}$ . Again, we note that  $\tau_{wgt}$  might be a partial mapping from Q to V.

In the following, we call  $\tau_{top}$  the topgraph initial mapping and call  $\tau_{wgt}$  the weighted graph initial mapping of *LC*. Besides these two initial mappings, we also introduce a method for evolving an initial mapping from the empty mapping. Similar idea was used by Zulehner et al. [14], while we extend a partial mapping only when necessary, i.e., when the thus extended mapping can execute a two-qubit gate in the current front layer or it can reduce the *minimum* physical distance (cf. Section 3.1) between qubits in a two-qubit gate in the current front layer. This mapping extension technique is also used when  $\tau_{top}$  or  $\tau_{wgt}$  is incomplete.

# 3.3 Fixed-Depth Heuristic Search

In most search-based algorithms for the qubit mapping problem, a heuristic function is used to select an action (i.e., a SWAP or a sequence of SWAPs) which can maximally reduce the sum or the minimum of the distances between the two qubits in the CNOT gates of the front layer and, sometimes, the lookahead layer.

For each edge  $e = \{v, v'\}$  in  $\mathcal{AG}$  there is an associated SWAP operation, written SWAP(e), which swaps the states on v and v'. More precisely, suppose  $\tau$  is the current mapping and  $\tau(q) = v$ ,  $\tau(q') = v'$ . Then SWAP(e) transforms  $\tau$  into a new mapping  $\tau'$  such that  $\tau'(q) = v'$ ,  $\tau'(q') = v$ , and

$\tau'(q^*) = \tau(q^*)$  for  $q^* \notin \{q, q'\}$ . In case if  $\tau(q)$  ( $\tau(q')$ ) is not defined and  $\tau(q') = v'$  ( $\tau(q) = v$ ), then  $\tau'(q')$  ( $\tau'(q)$ ) is not defined and  $\tau'(q) = v'$  ( $\tau'(q') = v$ ). If both are undefined, then  $\tau' = \tau$ . We often write SWAP(e)  $\circ \tau$  for  $\tau'$ .

**Example 4** (Example 1 cont'd). For the three qubit mappings in Fig. 4, we have  $\tau_2 = \text{SWAP}(1, 6) \circ \tau_1$  and  $\tau_3 = \text{SWAP}(6, 10) \circ \tau_2$ .

In this section, we propose a new heuristic function which measures how *efficient* the mapping can execute gates in the logical circuit. For convenience, we say a CNOT gate (in or not in the front layer) is executable by a mapping  $\tau$  if itself and all CNOT gates it depends on are satisfiable by  $\tau$ .

Starting with a selected initial mapping  $\tau^0$ , we write  $s^0 = (\tau^0, PC^0, LC^0)$  for the initial state of the search process, where  $LC^0$  is obtained by removing all CNOT gates  $\langle q, q' \rangle$  that are executable by  $\tau^0$  from LC, and  $PC^0$  is obtained by adding the corresponding CNOT gates  $\langle \tau^0(q), \tau^0(q') \rangle$  in an empty physical circuit. Step by step, we select an action *a* from S, the set of sequences of SWAPs on  $\mathcal{AG}$  and enforce all SWAPs in *a* one by one to get the next mapping (and the next state) till there are no gates left in the logical circuit.

Suppose  $s^i$  is the current state with  $s^i = (\tau^i, PC^i, LC^i)$ and all gates that are executable by  $\tau^i$  are already removed from  $LC^i$ . For a sequence  $a = (SWAP_1, SWAP_2, ..., SWAP_\ell)$  of SWAPs on  $\mathcal{AG}$ , we define a value function

$$\operatorname{val}(\tau^{i}, a) = \frac{\operatorname{number of gates executable by } \tau'}{\operatorname{len}(a) \times 3}, \quad (1)$$

where  $\tau'$  is the mapping obtained by enforcing SWAPs in action *a* one by one on  $\tau^i$  and  $\text{len}(a) = \ell$  is the number of SWAPs in *a*. Recall each SWAP is implemented by three CNOT gates (see Fig. 2 (right)).

Our action set consists of all sequences of SWAPs on  $\mathcal{AG}$  and we select any one with the maximal value, i.e., we select  $a^*$  from

$$\underset{a \in \mathcal{S}}{\operatorname{arg\,max}} \operatorname{val}(\tau^{i}, a).$$

(2)

After selecting  $a^*$ , we enforce on  $\tau^i$  SWAPs in  $a^*$  one by one and obtain the next mapping  $\tau^{i+1}$ . Then we remove all gates that are executable by  $\tau^{i+1}$  from  $LC^i$  and write  $LC^{i+1}$  for the resulted logical circuit. In the meanwhile, we append to  $PC^i$  three CNOT gates (as in Fig. 2 (right)) for each SWAP in  $a^*$ , and a CNOT gate  $\langle \tau^{i+1}(q), \tau^{i+1}(q') \rangle$  for each CNOT gate  $\langle q, q' \rangle$  removed from  $LC^i$ . In this way, we obtain  $PC^{i+1}$  and the next state  $s^{i+1} = (\tau^{i+1}, PC^{i+1}, LC^{i+1})$ .

Apparently, considering all sequences of SWAPs is inefficient. In practice, we propose to consider actions with up to k SWAPs for some fixed  $k \ge 1$ . In particular, for IBM Q Tokyo, we select k = 3, which reflects a good compromise between efficiency and effectiveness.

**Example 5** (Example 1 cont'd). Suppose  $\tau_1$  is the qubit mapping which maps  $q_0, q_1, q_2, q_3$  to, respectively,  $v_2, v_0, v_{10}, v_6$ , see Fig. 4 (left). As the front layer contains only  $g_0 = \langle q_2, q_0 \rangle$ , which is not executable by  $\tau_1$ , there are no gates in LC that can be executed by  $\tau_1$ . Examining all sequences of up to 3 SWAPs, the four best actions are as follows:

•  $a_1 = (SWAP(1, 6), SWAP(6, 10))$ , which can execute all 7 gates in LC;

- $a_2 = (SWAP(5, 6), SWAP(2, 6))$ , which can execute all 7 gates in LC;

- $a_3 = (SWAP(6,7), SWAP(6,10))$ , which can execute all but the last gate in LC;

- $a_4 = (SWAP(6, 11), SWAP(2, 6))$ , which can execute all but the last gate in LC.

The fifth best action contains 3 SWAPs. Thus  $a_1$  and  $a_2$  are the optimal actions, with the optimal value  $val(\tau_1, a_1) = val(\tau_1, a_2) = 7/6$ .

## 3.3.1 Heuristics used in related works

Now it is a good time to compare our heuristic function with those used in the related works.

Zulehner et al. [14] select the action that results in a mapping which can execute all gates in the front layer and the lookahead layer. The action consists of a sequence of SWAPs and is selected by using  $A^*$  search and the following heuristics:

$$\begin{split} h(\tau^{i}) &= \sum \bigg\{ 3 \times \left( \mathsf{dist}_{\mathcal{AG}}(\tau^{i}(q), \tau^{i}(q')) - 1 \right) \mid \\ & \langle q, q' \rangle \in \mathcal{L}_{0}(LC^{i}) \cup \mathcal{L}_{1}(LC^{i}) \bigg\}, \end{split}$$

where, for any two-qubit gate  $\langle q, q' \rangle$ , dist<sub>AG</sub>( $\tau^i(q), \tau^i(q')$ ) is the distance from  $\tau^i(q)$  to  $\tau^i(q')$  in AG. The heuristic cost is not admissible and thus an optimal action is not guaranteed. Moreover, the worst-case time complexity of this  $A^*$  search algorithm is exponential in the number of logical qubits.

Childs et al. [16] select the action which can maximally reduce the total distance between qubits in the CNOT gates in the current front layer, i.e.,

$$R(\tau^{i}) = \sum \left\{ \mathsf{dist}_{\mathcal{AG}}(\tau^{i}(q), \tau^{i}(q')) \mid \langle q, q' \rangle \in \mathcal{L}_{0}(LC^{i}) \right\}.$$

(3)

Their algorithm is polynomial in all relevant parameters but its performance is not directly compared with the  $A^*$  algorithm in [14].

To overcome the inefficiency of the  $A^*$  search algorithm, several researchers (see, e.g., [15], [17]) propose to select a *single* SWAP each time. Their methods are more efficient than the  $A^*$  approach when processing logical circuits with more than 15 qubits. In [15], Li et al. design a heuristic cost function that can reduce the sum of distances between the two qubits in each two-qubit gate in the front (and the lookahead) layers. Analogously, Cowtan et al. [17] use a heuristic cost function that can reduce the diameter of the subgraph composed of all qubits in the two-qubit gates of the front layer. In the evaluation section, we will see that the efficiency of these algorithms is achieved at the cost of the quality of the output physical circuit.

In the SAHS algorithm [18], we introduce a heuristic function that supports weight parameters to reflect the variable influence of gates in different layers. In each step, instead of selecting the action with the minimal cost to apply, the SAHS algorithm selects the SWAP which has the best consecutive SWAP to apply.

### 3.4 Optimisation and Fallback

Considering all sequences of up to k SWAPs is still not very efficient for devices with a medium to large architecture graph. Let  $\tau$  be the current mapping and  $\mathcal{L}_i$  the current *i*-th  $(0 \le i \le k)$  layer. Write  $Q_i$  for the set of logical qubits in  $\mathcal{L}_i$ . It's natural not to consider SWAPs that do not interact with gates in the front layers. This idea was used for edges in the front layer in, e.g., [14], [15], [18].

For an edge  $e = \{v, v'\}$ , if neither  $\tau^{-1}(v)$  nor  $\tau^{-1}(v')$  is in  $Q_0$ , then swapping v and v' does not reduce the minimum distance between qubits in a two-qubit gate in the current front layer, viz.  $\mathcal{L}_0$ . Therefore, it is reasonable to introduce the following filter for selecting actions  $a = (e_1, e_2, ..., e_\ell)$ with at most k SWAPs:

1.  $Q_0$ -filter: We say  $a = (e_1, e_2, ..., e_\ell)$  is a  $Q_0$ -plausible action if, for any edge  $e_j = \{v, v'\}$  of a, we have either  $\tau_{j-1}^{-1}(v)$  or  $\tau_{j-1}^{-1}(v')$  is in  $Q_0$ , where  $\tau_0 \equiv \tau$  and  $\tau_j$  is obtained from  $\tau_{j-1}$  by enforcing SWAP $(e_j)$  for  $1 \leq j \leq \ell$ .

Similarly, we could look ahead and introduce  $Q_i$ -filter for 0 < i < k.

2.  $Q_i$ -filter: We say  $a = (e_1, e_2, ..., e_\ell)$  is a  $Q_i$ -plausible action if, for any edge  $e_j = \{v, v'\}$  of a with j > i, we have either  $\tau_{j-1}^{-1}(v)$  or  $\tau_{j-1}^{-1}(v')$  is in  $Q_i$ , where  $\tau_0 \equiv \tau$  and  $\tau_j$  is obtained from  $\tau_{j-1}$  by enforcing SWAP $(e_j)$  for  $1 \le j \le \ell$ .

The above  $Q_i$ -filter could be weakened by requiring that either  $\tau_{i-1}^{-1}(v)$  or  $\tau_{i-1}^{-1}(v')$  is in (a subset of)  $Q_0 \cup Q_1 \cup \cdots \cup Q_i$ . In our evaluation, we used  $Q_0$  and (weakened)  $Q_1$  filters and the results are very promising (see Section 4).

It should be stressed that, sometimes,  $Q_0$ -filter may 'filter' out optimal actions.

**Example 6** (Example 1 cont'd). Note that  $Q_0 = \{0, 2\}$  and  $\tau_1(q_0) = v_2, \tau_1(q_2) = v_{10}$ . Each  $a_i$  for  $1 \le i \le 4$  in Example 5 is not  $Q_0$ -plausible. Thus our algorithm with  $Q_0$ -filter cannot find an optimal action. In fact, the following  $Q_0$ -plausible action is selected by our algorithm

•  $a_5 = (SWAP(2,7), SWAP(1,6), SWAP(6,10)).$

This action (see Fig. 4) can execute all 7 gates in LC and has  $val(\tau_1, a_5) = 7/9$ .

Another type of filters is also introduced in our algorithm. Let  $\tau$  be the current mapping and  $\mathcal{L}_i$  the *i*-th layer of the current logical circuit. Recall the notion of physical distance defined in Sec. 3.4 and assume that  $\gamma \in [0,1]$  is a discount factor and  $s \geq 0$ . For two mappings  $\tau_1$  and  $\tau_2$ , we say  $\tau_1$  is *s*-better than  $\tau_2$  if  $\hat{R}_s(\tau_1) < \hat{R}_s(\tau_2)$ , where for i = 1, 2 we have

$$\hat{R}_{s}(\tau_{i}) = \sum_{\ell=0}^{s} \gamma^{\ell} \times \left( \sum \left\{ \mathsf{dist}_{ph}(q, q', \tau_{i}) \mid \langle q, q' \rangle \in \mathcal{L}_{\ell} \right\} \right).$$

(4)

Intuitively,  $\tau_1$  being *s*-better than  $\tau_2$  implies that it is easier to execute all gates in the first *s*-level if we starts from  $\tau_1$  instead of  $\tau_2$ .

Let  $\tau$  be the current mapping. We define the  $D_s$ -filter as follows.

3.  $D_s$ -filter: We say  $a = (e_1, e_2, ..., e_\ell)$  is a  $D_s$ -plausible action if  $\tau_{j-1}$  is *not s*-better than  $\tau_j$  for any  $1 \le j \le \ell$ , where  $\tau_0 \equiv \tau$  and  $\tau_j$  is obtained from  $\tau_{j-1}$  by enforcing SWAP $(e_j)$  for  $1 \le j \le \ell$ .

Note that if  $\gamma = 0$  then  $D_s$ -filter is the same as  $D_0$ -filter.

## Fallback

For a prefixed positive integer k, it is possible that, in some cases, no sequence of SWAPs with length  $\leq k$  can lead to a mapping which can execute any CNOT gate in the current front layer. If this is the case, we use the following natural fallback:

**Fallback:** Select any SWAP that can reduce  $FB(\tau)$ , the minimum distance between qubits in a two-qubit gate in the current front layer, which is formally defined as follows:

$$FB(\tau) = \min\left\{\mathsf{dist}_{\mathcal{AG}}(\tau(q), \tau(q')) \mid \langle q, q' \rangle \in \mathcal{L}_0\right\}.$$

(5)

It is worth noting that, for our experiments on IBM Q Tokyo and an extensive set of logical circuits, the fallback is rarely activated.

# 3.5 Complexity Analysis

In the following we give a rough estimation of the complexity of the search process of our algorithm.

The construction of the topgraph and weighted graph initial mappings requires finding an isomorphic graph embedding. In general, it is NP-hard to check if a graph is isomorphic to a subgraph of another but there are efficient algorithms, say the VF2 algorithm [22], which can quickly solve this problem and output an embedding if the answer is yes for graphs with several thousands nodes. Therefore, for the purpose of qubit mapping with NISQ devices, we don't take into our analysis the time of computing an initial mapping. Experiments on various architecture graphs with up to 361 nodes and circuits with up to 50 qubits and 15,000 CNOT gates show that the time consumption is acceptable. For detailed discussion please see Sec. **??**.

Suppose LC = (Q, C) is a logical circuit and  $\mathcal{AG} = (V, E)$  is the architecture graph of a NISQ device. Write |Q|, |V|, and |E| be, respectively, the cardinalities of Q, V, and E. Let *diam* be the diameter of  $\mathcal{AG}$  and m the number of CNOT gates in C.

We have the following simple observations:

- The dependency graph of *LC* can be computed in time linear in *m*.

- For any mapping τ and any logical circuit *LC*, we can identify (and remove from *LC* as well as from its dependency graph) in time linear in *m* the set of gates in *LC* executable by τ.

We first consider the ideal case when fallback is never activated during the search process. As described in Section 3.3, starting with a selected initial mapping  $\tau^0$ , step by step, we select an action a consisting of up to k SWAPs on  $\mathcal{AG}$  and enforce all SWAPs in a one by one to get the next mapping till there are no gates left in the logical circuit. Suppose  $s^i = (\tau^i, PC^i, LC^i)$  is the current search state. As there are at most  $O(|E|^k)$  actions with up to k SWAPs, we can generate at most  $O(|E|^k)$  different mappings from  $\tau^i$ . To

select from these mappings the one which can execute the most gates in  $LC^i$ , we need time  $O(|E|^k \cdot m)$  (cf. the second observation above). Because each step removes at least one CNOT from LC, in at most  $O(|E|^k \cdot m^2)$  time, we can execute all gates in LC. We note that this is an overestimated upper bound. If any Q-filter is used, there are at most  $n^k \cdot deg^k$  actions with up to k SWAPs, where deg is the maximum degree of  $\mathcal{AG}$ . For IBM Q Tokyo, the maximum degree is 6, and for most grid-like AGs, the maximum degree is 4.

Now, suppose fallback is activated. Since each activation of the fallback reduces by (at least) one the minimum distance between qubits in a CNOT gate in the current front layer (i.e.,  $FB(\tau)$  in Eq. 5), the whole search process activates the fallback procedure at most  $m \times diam$  times. Note that each activation (see Eq. 5) needs to compute the shortest distance between the control and target qubits in a CNOT gate in the front layer of the current logical circuit and there are at most |Q|/2 CNOT gates in the front layer. Using Dijkstra's algorithm with lists,  $FB(\tau)$  can be computed in time  $O(|Q| \cdot |V|^2)$ .<sup>3</sup> Thus the total fallback on-cost is at most  $O(|Q| \cdot |V|^2 \cdot m \cdot diam)$ .

Therefore, the overall time complexity of the search process is  $O(|E|^k \cdot m^2 + |Q| \cdot |V|^2 \cdot m \cdot diam)$ . As  $|Q| \le |V| \le |E| + 1$  and diam is usually very small when compared with m, the overall time complexity is bounded by  $O(|E|^k \cdot m^2)$  if  $k \ge 3$ . In practice, this could be significantly reduced if we use Q-filters as the base in  $|E|^k$  can be significantly reduced.

As for the space complexity, in each state s, we maintain, besides the logical and physical circuits, the dependency graph of the current logical circuit and the set of plausible actions with up to k SWAPs. Thus the space complexity of the algorithm is bounded by  $O(|E|^k + m)$ .

# 4 EVALUATION

In this section, we compare our approach with the SABRE algorithm of Li et al. [15], the Cambridge algorithm of [17], and our qubit transformation algorithm SAHS based on simulated annealing and heuristic search [18], which are the state-of-the-art algorithms for the qubit mapping problem on IBM Q Tokyo (see Fig. 1). Although we focus on a particular NISQ device in the evaluation, our approach is applicable to any undirected architecture graph, including for example Rigetti 16Q Aspen-4<sup>4</sup>. We use Python as our programming language and IBM Qiskit [23] as auxiliary environment.<sup>5</sup> All experiments are conducted in a MacBook Pro with 3.1 GHz Intel Core i5 processor and 8GB memory.

As for benchmark circuits, we consider all publicly available circuits evaluated in [15] or [17]. Note that only CNOT gates are concerned in our comparison. For each individual circuit, we extract all its CNOT gates and use the thus reduced circuit as the input of our qubit mapping algorithm. We then compare the involved algorithms in terms of the number of auxiliary CNOT gates required. One may also use the following relative measure  $R_{\text{CNOT}}$ , first introduced in [17], to compare different algorithms on a particular circuit:

$$R_{\text{CNOT}} = \frac{\text{\#CNOT in the output physical circuit}}{\text{\#CNOT in the input logical circuit}}$$

In order to compare algorithms evaluated over different benchmark sets of circuits, for any benchmark set  $\mathcal{B}$  of quantum circuits, we define the following CNOT index, written  $I_{CNOT}^{\mathcal{B}}$ , of an algorithm relative to  $\mathcal{B}$  as the fraction of the total number of CNOT gates in all output physical circuits over the total number of CNOT gates in all input logical circuits from  $\mathcal{B}$ , i.e.,

$$I_{CNOT}^{\mathcal{B}} = \frac{\sum_{LC \in \mathcal{B}} \#CNOT \text{ in the output physical circuit of } LC}{\sum_{LC \in \mathcal{B}} \#CNOT \text{ in } LC}$$

For convenience, we write  $\mathcal{B}_s$  and  $\mathcal{B}_c$  for the benchmark sets of circuits used in [15] and [17] respectively. Note that  $\mathcal{B}_c$  contains 131 circuits and includes all the 23 circuits in  $\mathcal{B}_s$ . For more precise comparison, we decompose  $\mathcal{B}_c$  into three categories according to the number of CNOTs these benchmark circuits contain: small (0-99), medium (100-999) and large ( $\geq 1000$ ).

For all experiments reported here, we fix the search depth k as 3 and use  $Q_0$ -filter for the first SWAP and  $Q_1$ -filter for all the other SWAPs for filtering actions  $a = (e_1, ..., e_\ell)$  with at most 3 SWAPs. In addition, we also adopt the  $D_0$ -filter to exclude more less significant actions.

## 4.1 Comparison Among Different Initial Mappings

We first compare the two subgraph isomorphism related initial mappings (viz., the topgraph initial mapping  $\tau_{top}$ and the weighted graph initial mapping  $\tau_{wgt}$ ) introduced in Section 3 with the empty mapping and the naive initial mapping (which maps  $q_i$  to  $v_i$  for each  $q_i$  in Q). Table 3 summarises the results for all (small, medium, large) circuits in  $\mathcal{B}_c$ , while we give the detailed results in Tables 7-9 in Section A. For each of these circuits and each initial mapping, the transformation can be completed within about 500 seconds by using our algorithm.

From Table 3, we can see that the two isomorphism subgraph related initial mappings,  $\tau_{top}$  and  $\tau_{wgt}$  are significantly better than the empty initial mapping and the naive initial mapping for small and medium circuits, but the difference is not significant when large circuits are evaluated. This is not a surprise as the search heuristics plays a dominant role if the circuit has a large size. Note that if a logical circuit can be transformed into a physical circuit with zero overhead, our algorithm, when using either the topgraph or weighted graph initial mapping, will very likely detect this.

Since the topgraph initial mapping is slightly better than the other three initial mappings, in the following, when compared with other algorithms, we always use the topgraph initial mapping.

# 4.2 Comparison with SABRE, Cambridge, and SAHS

We then compare our algorithm with SABRE [15] on the small benchmark set  $\mathcal{B}_s$  of circuits used in [15]. We use the topgraph initial mapping  $\tau_{top}$ . The results are reported in Table 2, in which the 'Comparison' column shows the improvement of our algorithm over SABRE in terms of the

<sup>3.</sup> In practice, we precompute the distance between every two nodes of  $\mathcal{AG}$  and store it in a table.

<sup>4.</sup> Note that this device supports CZ instead of CNOT.

<sup>5.</sup> Code available at https://github.com/BensonZhou1991/Qubit-Mapping-Subgraph-Isomorphism

| benchmarks | #circ. | topgr.i.m. | wghtgr.i.m. | empty i.m. | naive i.m. | SAHS   | Cambridge |

|------------|--------|------------|-------------|------------|------------|--------|-----------|

| small      | 63     | 1.2521     | 1.3175      | 1.5041     | 1.8760     | 1.2619 | 1.5103    |

| medium     | 39     | 1.2886     | 1.3034      | 1.4074     | 1.5727     | 1.3101 | 1.6854    |

| large      | 29     | 1.4280     | 1.4366      | 1.4504     | 1.4422     | 1.6151 | 1.8211    |

| all        | 131    | 1.4231     | 1.4324      | 1.4497     | 1.4486     | 1.6047 | 1.8154    |

|            | 1      |            | TAB         | LE 1       |            |        |           |

Summary of the I<sup>B</sup><sub>CNOT</sub>-index of our algorithm with four different initial mapping constructing methods and SAHS and Cambridge

numbers of auxiliary CNOT gates added. Specifically, let  $n_{sabre}$  and  $n_{ours}$  be the numbers of CNOT gates added by SABRE and by ours, respectively. Then the improvement ratio is calculated as  $(n_{sabre} - n_{ours})/n_{sabre}$ . From Table 2 we can see that only two circuits have negative improvement against SABRE. For all circuits with more than 300 CNOT gates, the improvement is at least 48%. In terms of the CNOT index, we have successfully decreased the index  $I_{\rm CNOT}^{\mathcal{B}_{\rm s}}$  from 1+50874/50534=2.0067 to 1+20790/50534=1.4114.

We further compare our algorithm with the Cambridge algorithm of [17] and our SAHS algorithm [18] on the large benchmark set  $\mathcal{B}_c$ , which contains 131 circuits. A summary of the results in terms of the CNOT index is presented in Table 3. As for detailed results, see Tables 7-9 in Section A. It is worth stressing that the results of the Cambridge algorithm is obtained without using postmapping optimisations. Precisely, we have removed the following codes from their algorithm:

- 'Transform.OptimisePhaseGadgets().apply(tkcirc)' and

- 'Transform.OptimisePostRouting().apply(outcirc)'.

Thus the results of their algorithm given in Tables 7-9 are different from those reported in [17, Table VI]. In this sense, Tables 7-9 provide a fair comparison as we do not do postmapping optimisations either.

From Table 3 we can see that, for all 131 circuits in  $\mathcal{B}_c$ , the  $I_{CNOT}^{\mathcal{B}_c}$  index of our algorithm is 1+141252/333811 = 1.4231, while the indices for SAHS and Cambridge are, respectively, 1.6047 and 1.8154. This shows that our algorithm can in average generate significantly better results than Cambridge and SAHS. This is particularly true for large circuits which contain 1000 or more CNOT gates. For small circuits with less than 100 CNOT gates, our algorithm is slightly better than SAHS, 2 points (1.2886 vs. 1.3101) better than SAHS when medium circuits with 100-999 CNOT gates are considered. Both algorithms are significantly better than Cambridge in all three categories.

In the above experiments, we used  $Q_0$ -filter for the first SWAP and  $Q_1$ -filter (see Section 3.4) for all the other SWAPs when filtering actions with up to 3 SWAPs. If we use  $Q_0$ -filter for all SWAPs, then the index becomes 1.4774, which is about 5 points inferior to the index 1.4231 reported in Table 3. In addition, if we weaken  $Q_1$ -filter by using the qubits in the front layer and the lookahead layer, then the index could be further improved to **1.3801** from 1.4231. However, this is achieved at the cost of slower search process: for six large circuits (e.g., 'mlp4\_245' with 16 qubits and 8232 CNOT gates), the compete process requires 900-1600 seconds.

# 4.3 Detailed Empirical Results

In the following, we present the detailed empirical results in Tables 7-9.

# 5 FURTHER DISCUSSION

From the above evaluation, we can see that our algorithm has significant better performance on IBM Q Tokyo than state-of-the-art algorithms. In this section, we give a more detailed discussion on the effectiveness, extensibility and time efficiency of our algorithm. In particular, we report more experiments on three larger architecture graphs.

# 5.1 Extension

Our filtered depth-limited approach actually can adopt heuristic value functions other than Eq. 1. Indeed, we have implemented another value function that based on the function specified in Eq. 4. The new heuristic value function is obtained by replacing "number of gates executable by  $\tau'''$  in Eq. 1 with  $\hat{R}_s(\tau^i) - \hat{R}_s(\tau')$ , i.e., we have

$$\widehat{\mathsf{val}}_s(\tau^i, a) = \frac{\hat{R}_s(\tau^i) - \hat{R}_s(\tau')}{\mathsf{len}(a) \times 3},\tag{6}$$

where  $\tau'$  is the mapping obtained by enforcing SWAPs in action *a* one by one on  $\tau^i$  and  $\text{len}(a) = \ell$  is the number of SWAPs in *a*. Using this value function, we then select any action with the maximal value as our next action. The algorithm adopting this value function has the same computational complexity as the one discussed before while its performance is similar to that of the Cambridge algorithm on IBM Q Tokyo and the benchmark set  $\mathcal{B}_c$ .

#### 5.2 Effectiveness

While it works very good in average and especially on large circuits, our algorithm performs bad on several small or medium circuits. For example, the circuit 'alu-v0\_27' contains 5 qubits and 17 CNOT gates. To execute it on IBM Q Tokyo, our QCT algorithm needs to insert 3 (2, resp.) swaps if the topograph (wgtgraph, resp.) initial mapping is used, while both Cambridge and SABRE only require 1 swap.

This bad performance is perhaps due to three reasons. First, during the search process, our algorithm works in a greedy way and always try to find the best action. This, however, often leads to a series of local optimal transformations, which gives no guarantee to the optimality of the global transformation. Second, there are many different mappings which can embed a given graph into  $\mathcal{AG}$ . Our algorithm selects an arbitrary one. Selecting a good embedding may further improve the performance of our algorithm. Third, our selection of the initial mapping is also greedy (cf. Sec. 3.2). For example, when constructing the topgraph initial mapping, we select a maximal subcircuit  $C_{top}$  of C whose corresponding graph  $\mathcal{G}_{circ}(C_{top})$  is isomorphic to a subgraph of  $\mathcal{AG}$ . The following example shows that, however, this is not always a good choice.

| <u> </u>       | 1     |        | · · · |       | . 1      | , 1      |       |

|----------------|-------|--------|-------|-------|----------|----------|-------|

| Circuit        | qubit | input  | input | SABRE | topgraph | topgraph | Comp. |

| Name           | no.   | gate   | CÑOT  | added | added    | time (s) |       |

| 4mod5-v1_22    | 5     | 21     | 11    | 0     | 0        | 0.01     | 1     |

| mod5mils_65    | 5     | 35     | 16    | 0     | 0        | 0.01     | 1     |

| alu-v0_27      | 5     | 36     | 17    | 3     | 9        | 0.07     | 3     |

| decod24-v2 43  | 4     | 52     | 22    | 0     | 0        | 0.01     | 1     |

| 4gt13_92       | 5     | 66     | 30    | 0     | 0        | 0.01     | 1     |

| ising_model_10 | 10    | 480    | 90    | 0     | 0        | 0.01     | 1     |

| ising_model_13 | 13    | 633    | 120   | 0     | 0        | 0.01     | 1     |

| ising_model_16 | 16    | 786    | 150   | 0     | 0        | 0.01     | 1     |

| qft_10         | 10    | 200    | 90    | 54    | 39       | 0.01     | 0.72  |

| qft_16         | 16    | 512    | 240   | 186   | 153      | 124      | 0.82  |

| rd84_142       | 15    | 343    | 154   | 105   | 72       | 8.72     | 0.69  |

| adr4_197       | 13    | 3439   | 1498  | 1614  | 630      | 37.4     | 0.39  |

| radd_250       | 13    | 3213   | 1405  | 1275  | 555      | 52.8     | 0.44  |

| z4 268         | 11    | 3073   | 1343  | 1365  | 630      | 27.5     | 0.46  |

| sym6_145       | 7     | 3888   | 1701  | 1272  | 513      | 4.8      | 0.40  |

| misex1 241     | 15    | 4813   | 2100  | 1521  | 786      | 40.9     | 0.52  |

| rd73 252       | 10    | 5321   | 2319  | 2133  | 1095     | 23.6     | 0.51  |

| cycle10 2 110  | 12    | 6050   | 2648  | 2622  | 1194     | 23.7     | 0.46  |

| square root 7  | 15    | 7630   | 3089  | 2598  | 1338     | 446.9    | 0.52  |

| sqn_258        | 10    | 10223  | 4459  | 4344  | 1578     | 39.9     | 0.36  |

| rd84 253       | 12    | 13658  | 5960  | 6147  | 2352     | 111.8    | 0.38  |

| co14 215       | 15    | 17936  | 7840  | 8982  | 4257     | 194.6    | 0.47  |

| sym9_193       | 11    | 34881  | 15232 | 16653 | 5589     | 161.1    | 0.34  |

| sum            | -     | 117289 | 50534 | 50874 | 20790    | -        | 0.41  |

|                |       |        | TADI  |       |          |          |       |

TABLE 2

Comparison of our algorithm with SABRE in [15] on IBM Q Tokyo. The numbers in the last column indicate the ratio of our added CNOT gates (with the topgraph initial mapping) against that of SABRE.

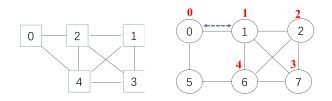

Fig. 5. The circuit graph of 'alu-v0\_27' (left) and a mapping (right).

**Example 7.** Consider the circuit 'alu-v0\_27', which contains 5 qubits and the 17 CNOT gates in

$$C = \left( \langle 3, 4 \rangle, \langle 2, 1 \rangle, \langle 1, 3 \rangle, \langle 2, 1 \rangle, \langle 3, 2 \rangle, \langle 3, 1 \rangle, \langle 2, 1 \rangle, \langle 3, 2 \rangle, \langle 1, 3 \rangle, \langle 2, 0 \rangle, \langle 0, 4 \rangle, \langle 2, 0 \rangle, \langle 4, 2 \rangle, \langle 4, 0 \rangle, \langle 2, 0 \rangle, \langle 4, 2 \rangle, \langle 0, 4 \rangle \right).$$

The circuit graph (Fig. 5 (left)) is not embeddable in  $\mathcal{AG}$ , the architecture graph of IBM Q Tokyo. Let  $C_{top}$  be the sub-circuit of the first 10 gates in C. Then the circuit graph of  $C_{top}$  is the topgraph of C and can be embedded in  $\mathcal{AG}$ . Let  $\tau'$  be such an embedding. After removing gates in  $C_{top}$ , the rest gates (involving only qubit 0, 2, and 4) cannot be solved with one swap from  $\tau'$ . However, letting  $\tau$  be the mapping as showing in the right of Fig. 5, we can see that  $\tau$  solves only the first 9 gates and, after swapping 0 and 1, the rest 7 gates can also be solved.

#### 5.3 Scalability and More on Time Complexity

In Sec. 3.5 we have seen that the search process is polynomial in all relevant parameters. As we go deeper in the search tree, our algorithm is considerably slower than SABRE and Cambridge. The significant decrease of the CNOT index shows that this is, however, worthwhile.

In contrast with the search process, the initial mapping construction process relies on the efficiency of subgraph isomorphism algorithms, which have time complexity exponential in the number of qubits in the circuit. We argue that this is not a serious problem for the following reasons. First, for the QCT problem in the NISQ era, only graphs with up to 1000 nodes are involved. Second, the architecture graphs usually have very simple and regular (e.g., grid-like) topologies, which can be exploited to design customised efficient subgraph isomorphism algorithms. Last but not least, good approximate solutions can also do the job well. This is partially evidenced by the results summarised in Table 3, where it shows that, for large circuits, the transformation results with an empty mapping are only slightly inferior to that using the selected topgraph initial mappings.

To further evaluate the effectiveness and efficiency of our approach, we have added experiments on IBM Q Rochester (53 qubits), Google's Sycamore (53 qubits), and an artificial  $19 \times 19$  grid architecture graph, called Q19×19, which has 361 nodes. As circuits in the benchmark set  $\mathcal{B}_c$  have only up to 16 qubits, we also tested a benchmark of circuits with large number of qubits. The benchmark was used in xx for xx, containing 19 circuits with 20-50 qubits and up to 15000 CNOT gates. The running time of our algorithm on these larger AGs does not get worse. See Table xx.

| benchmarks | #circ. | topgr.i.m. | wghtgr.i.m. | empty i.m. | naive i.m. | SAHS   | Cambridge |

|------------|--------|------------|-------------|------------|------------|--------|-----------|

| smallx     | 63     | 1.2521     | 1.3175      | 1.5041     | 1.8760     | 1.2619 | 1.5103    |

| medium     | 39     | 1.2886     | 1.3034      | 1.4074     | 1.5727     | 1.3101 | 1.6854    |

| large      | 29     | 1.4280     | 1.4366      | 1.4504     | 1.4422     | 1.6151 | 1.8211    |

| alĬ        | 131    | 1.4231     | 1.4324      | 1.4497     | 1.4486     | 1.6047 | 1.8154    |

|            |        |            |             |            |            |        |           |

TABLE 3 Summary of the  $I_{CNOT}^{\mathcal{B}}$ -index of our algorithm with four different initial mapping constructing methods and SAHS and Cambridge

| Circuit<br>name                                | qubit<br>no.     | input<br>CNOT | topgr.<br>added | wgtgr.<br>added | empty<br>added    | naive<br>added | SAHS<br>added | Cambridge<br>added |

|------------------------------------------------|------------------|---------------|-----------------|-----------------|-------------------|----------------|---------------|--------------------|

| ex1_226                                        | 6                | 5             | 0               | 0               | 3                 | 18             | 0             | 0                  |

| graycode6_47                                   | 6                | 5             | 0               | 0               | 0                 | 9              | 0             | 0                  |

| xor5_254                                       | 6                | 5             | 0               | 0               | 3                 | 18             | 0             | 0                  |

| 4gt11_84                                       | 4                | 9             | 0               | 0               | 9                 | 12             | 0             | 0                  |

| ex-1_166                                       | 3                | 9             | 0               | 0               | 6                 | 6              | 0             | 0                  |

| 4mod5-v0_20                                    | 5                | 10            | 0               | 0               | 9                 | 9              | 0             | 9                  |

| 4mod5-v1_22                                    | 5<br>3           | 11            | 0               | 0               | 9<br>9            | 12             | 0             | 9                  |

| ham3_102<br>mod5d1_63                          | 5                | 11<br>13      | 0               | 0<br>0          | 3                 | 6<br>12        | 0             | 0<br>0             |

| 4gt11_83                                       | 5<br>5           | 13<br>14      | 0               | 0               | 0                 | 12             | 0             | 0<br>12            |

| 4mod5-v0 19                                    | 5                | 16            | 0               | 0               | 0                 | 18             | 0             | 9                  |

| $4 \mod 5 - v_0 - 19$<br>$4 \mod 5 - v_1 - 24$ | 5                | 16            | 0               | 0               | 15                | 21             | 0             | 12                 |

| mod5mils_65                                    | 5                | 16            | 0               | Ő               | 15                | 21             | 0             | 9                  |

| rd32-v0_66                                     | 4                | 16            | Ő               | õ               | 18                | 18             | Ő             | Ó                  |

| rd32-v1_68                                     | 4                | 16            | 0               | 0               | 18                | 18             | 0             | 0                  |

| 3_17_13                                        | 3                | 17            | 0               | 0               | 9                 | 9              | 0             | 0                  |

| alu-v0_27                                      | 5                | 17            | 9               | 6               | 12                | 18             | 6             | 3                  |

| alu-v1_29                                      | 5                | 17            | 9               | 6               | 12                | 24             | 6             | 3                  |

| alu-v2_33                                      | 5                | 17            | 9               | 6               | 12                | 18             | 6             | 9                  |

| 4gt11_82                                       | 5                | 18            | 3               | 3               | 3                 | 27             | 3             | 12                 |

| alu-v1_28                                      | 5                | 18            | 9               | 6               | 21                | 18             | 6             | 3                  |

| alu-v3_35                                      | 5                | 18            | 9               | 6               | 12                | 24             | 6             | 3                  |

| alu-v4_37                                      | 5                | 18            | 9               | 6               | 12                | 18             | 6             | 3                  |

| decod24-v2_43<br>decod24-v0 38                 | $\frac{4}{4}$    | 22<br>23      | 0               | 0<br>0          | 18<br>27          | 15<br>15       |               | 0<br>0             |

| miller_11                                      | 3                | 23            | 0               | 0               | 6                 | 9              | 0             | 0                  |

| alu-v3_34                                      | 5                | 23            | 9               | 6               | 27                | 27             | 6             | 3                  |

| mod5d2_64                                      | 5                | 25            | 18              | 9               | 18                | 36             | 12            | 12                 |

| 4gt13_92                                       | 5                | 30            | 0               | Ó               | 30                | 42             | 0             | 18                 |

| 4gt13-v1_93                                    | 5<br>5           | 30            | Õ               | Õ               | 33                | 27             | Õ             | 18                 |

| 4mod5-bdd_287                                  | 7                | 31            | 6               | 18              | 9                 | 36             | 6             | 15                 |

| 4mod5-v0_18                                    | 5                | 31            | 9               | 12              | 30                | 36             | 9             | 9                  |

| 4mod5-v1_23                                    | 5                | 32            | 9               | 21              | 30                | 36             | 9             | 12                 |

| decod24-bdd_294                                | 6                | 32            | 15              | 27              | 24                | 24             | 15            | 21                 |

| one-two-three-v2_100                           | 5                | 32            | 9               | 9               | 18                | 30             | 9             | 9                  |

| one-two-three-v3_101                           | 5                | 32            | 15              | 18              | 24                | 36             | 6             | 15                 |

| rd32_270                                       | 5                | 36            | 18              | 24              | 39<br>24          | 30             | 12            | 18                 |

| 4gt5_75                                        | 5<br>7           | 38<br>38      | 9<br>24         | 12<br>15        | 24                | 51<br>36       | 15<br>24      | 15<br>45           |

| alu-bdd_288<br>alu-v0_26                       | 5                | 38            | 12              | 9               | 39<br>30          | 36             | 9             | 43<br>21           |

| decod24-v1_41                                  | 5                | 38            | 3               | 21              | 21                | 45             | 15            | 18                 |

| 4gt5_76                                        | 5<br>5           | 46            | 21              | $\frac{21}{36}$ | $\frac{21}{48}$   | 48             | 15            | 27                 |

| 4gt13_91                                       | 5                | 49            | 6               | 6               | 15                | 45             | 15            | 6                  |

| alu-v4_36                                      | 5                | 51            | 6               | 15              | 30                | 30             | 15            | 36                 |

| 4gt13_90                                       | 5                | 53            | 9               | 9               | 18                | 48             | 27            | 9                  |

| 4gt5_77                                        | 5                | 58            | 9               | 18              | 18                | 45             | 9             | 36                 |

| one-two-three-v1_99                            | 5                | 59            | 24              | 33              | 42                | 48             | 12            | 39                 |

| rd53_138                                       | 8                | 60            | 30              | 42              | 30                | 42             | 27            | 39                 |

| decod24-v3_45                                  | 5<br>5<br>5<br>5 | 64            | 15              | 24              | 36                | 72             | 15            | 39<br>27           |

| one-two-three-v0_98                            | 5                | 65            | 18              | 27              | 48                | 63<br>60       | 24<br>27      | 27                 |

| 4gt10-v1_81<br>aj-e11_165                      | 5                | 66<br>69      | 15<br>33        | 18<br>36        | 36<br>42          | 60<br>33       | 18            | 33<br>24           |

| 4mod7-v0_94                                    | 5                | 72            | 12              | 27              | 33                | 51             | 12            | 39                 |

| 4mod7-v1_96                                    | 5                | 72            | 21              | 21              | 48                | 45             | 18            | 42                 |

| alu-v2_32                                      | 5                | 72            | 15              | 45              | 69                | 45             | 15            | 39                 |

| mod10_176                                      | 5                | 78            | 15              | 24              | 63                | 66             | 24            | 36                 |

| 4gt4-v0_80                                     | 6                | 79            | 15              | 39              | 48                | 69             | 24            | 78                 |

| cnt3-5_179                                     | 16               | 85            | 3               | 30              | 72                | 87             | 15            | 87                 |

| 4gt12-v0_88                                    | 6                | 86            | 21              | 15              | 69                | 66             | 21            | 21                 |

| ising_model_10                                 | 10               | 90            | 0               | 0               | 18                | 27             |               | 0                  |

| qft_10                                         | 10               | 90            | 45              | 33              | 57                | 96<br>60       | 36            | 57                 |

| sys6-v0_111                                    | 10               | 98<br>00      | 54              | 81<br>20        | 63                | 60<br>48       | 45            | 111                |

| 4_49_16<br>sum                                 | 5                | 99<br>2428    | 18<br>618       | 30<br>849       | $\frac{42}{1602}$ | 48<br>2133     | 36<br>636     | <u>69</u><br>1239  |

| I-index                                        |                  | 2420          | 1.255           | 1.350           | 1.660             | 1.879          | 1.262         | 1.510              |

| 1 11/06A                                       |                  |               | 1.200           | 1.550           | 1.000             | 1.077          | 1.202         | 1.010              |

| Circuit                                                | qubit | input | topgr. | wgtgr. | empty | naive | SAHS  | Cambridge |  |  |

|--------------------------------------------------------|-------|-------|--------|--------|-------|-------|-------|-----------|--|--|

| name                                                   | no.   | CNOT  | added  | added  | added | added | added | added     |  |  |

| TABLE 4: Comparison on IBM Q Tokyo with small circuits |       |       |        |        |       |       |       |           |  |  |

|                            | 1.1      |                    | t and and       |                 |                |                | 0.4.110       | Complexides        |

|----------------------------|----------|--------------------|-----------------|-----------------|----------------|----------------|---------------|--------------------|

| Circuit                    | qubit    | input<br>CNOT      | topgr.<br>added | wgtgr.<br>added | empty<br>added | naive<br>added | SAHS<br>added | Cambridge<br>added |

| name<br>4gt12-v1 89        | no.<br>6 | $\frac{1001}{100}$ | 57              | 18              | 30             | 81             | 24            | <u>93</u>          |

| 0410184 169                | 14       | 100                | 6               | 27              | 30<br>75       | 93             | 12            | 93<br>75           |

| 4gt4-v0 79                 | 6        | 104                | 12              | 12              | 30             | 93<br>87       | 12            | 96                 |

| hwb4 49                    |          | 105                | 36              | 42              | 50<br>54       | 63             | 33            | 45                 |

| mod10 171                  | 5<br>5   | 107                | 39              | 42<br>27        | 27             | 60             | 24            | 60                 |

|                            | 6        | 108                | 15              | 15              | 33             | 93             | 15            | 99                 |

| 4gt4-v0_78<br>4gt12-v0 87  | 6        | 109                | 6               | 6               | 33<br>24       | 93<br>69       | 6             | 123                |

| 4gt4-v0_72                 | 6        | 112                | 45              | 39              | 51             | 93             | 42            | 90                 |

| 4gt12-v0_72<br>4gt12-v0_86 | 6        | 115                | 43<br>9         | 39<br>9         | 27             | 93<br>75       | 42<br>9       | 123                |

| 4gt4-v1_74                 | 6        | 110                | 39              | 27              | 75             | 93             | 78            | 123                |

|                            | 13       | 119                | 0               | 0               | 36             | 93<br>45       | 0             | 0                  |

| ising_model_13             |          |                    | 30              |                 |                | 45<br>87       | 33            | 0<br>75            |

| mini-alu_167               | 5        | 126                |                 | 33              | 69<br>70       |                |               |                    |