# Design of Miniaturized On-Chip Passive Circuits in Silicon-Based Technology for 5G Communications

## by Zeyu Ge

Thesis submitted in fulfilment of the requirements for the degree of

# **Doctor of Philosophy**

under the supervision of

Dr Xi Forest Zhu

University of Technology Sydney, Australia

Associate Professor Roberto Gómez-García University of Alcala, Spain

Faculty of Engineering & IT

University of Technology Sydney

07/2021

Certificate of Authorship/Originality

CERTIFICATE OF ORIGINAL AUTHORSHIP

I, Zeyu Ge declare that this thesis, is submitted in fulfilment of the requirements for the award

of Doctor of Philosophy, in the Faculty of Engineering & IT at the University of Technology

Sydney.

This thesis is wholly my own work unless otherwise referenced or acknowledged. In addition, I

certify that all information sources and literature used are indicated in the thesis.

This document has not been submitted for qualifications at any other academic institution.

This research is supported by the Australian Government Research Training Program.

Production Note:

Signature: Signature removed prior to publication.

Date: July 2021

# **ACKNOWLEDGEMENT**

First and foremost, I would like to give my sincere thanks to my supervisor Dr. Forest Zhu and my co-supervisor Associate Prof. Roberto Gómez-García. They have taught me well with their knowledge throughout the period of this research. Without their enlightening advice, instructions, and corrections of my work, I would not have completed my thesis. Their suggestions and continuous support assuredly guided me in researching my postgraduate goals.

I would also like to thank my SEDE colleagues, Lang Chen, Lisheng Chen, Jefferson Hora, who helped so much during my design and test periods, for all their kindness and assistance. I appreciate having such wonderful friends in the same supervised team. They have become reliable connections for the rest of my life.

My wife Xinyin, my parents and my parents-in-law, gave me strong support both emotionally and financially. My wife's sacrifice of her own precious time and career enabled me to have less stress and more time to do my research.

Moreover, the following institutions and faculties should be acknowledged. Firstly, I thak the University of Technology Sydney, for giving me the opportunity to study. Secondly, appreciation goes to Andar Technologies in Melbourne for the switch testing. Thirdly, UTS Tech Lab was like a big warm family and I enjoyed working its staff like one big family.

Last but not least, I would give thanks to all my friends and family members, especially my young cousin, for all their encouragement and support.

# TABLE OF CONTENTS

| Certificate of Authorship/Originality                                                 | 2  |

|---------------------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENT                                                                       | 3  |

| TABLE OF CONTENTS                                                                     | 4  |

| LIST OF FIGURES                                                                       | 6  |

| LIST OF TABLES                                                                        | 9  |

| Abstract                                                                              | 10 |

| Chapter 1 Introduction                                                                | 12 |

| 1.1 Background                                                                        | 12 |

| 1.1.1 5G and Millimeter-Wave                                                          | 12 |

| 1.1.2 Filtering Technology Development                                                | 14 |

| 1.1.3 Advanced Semiconductor Technologies                                             | 16 |

| 1.1.4 Miniaturized Passive Devices                                                    | 17 |

| 1.2 Challenges and Motivations                                                        | 18 |

| 1.3 Contributions                                                                     | 20 |

| 1.4 Organization of the Thesis                                                        | 21 |

| Chapter 2: Literature Review.                                                         | 23 |

| 2.1 Theoretical Basics                                                                | 23 |

| 2.1.1 The Basic Technical Indicators of the Filter                                    | 23 |

| 2.1.2 Design Methodologies for On-Chip mm-wave Filters                                |    |

| 2.1.3 Manufacturing Technologies                                                      | 25 |

| 2.2 Review of Related Passive Research.                                               |    |

| 2.2.1 Interdigital Structure                                                          | 28 |

| 2.2.2 Stepped Impedance Technique                                                     | 33 |

| 2.2.3 Slow-Wave Structures                                                            | 37 |

| 2.2.4 Coplanar Waveguide (CPW) Structures                                             | 38 |

| 2.2.5 Shielded Coplanar Waveguide                                                     | 40 |

| 2.2.6 Meander-Liner Resonator                                                         | 41 |

| 2.2.7 Closed- and Open-Loop Structures                                                | 43 |

| 2.3 Trends and Issues of the State-of-the-Art Designs.                                | 44 |

| 2.3.1 Issues with Wide-Band BPF Designs                                               | 44 |

| 2.3.2 Issues with BSF Designs                                                         | 45 |

| Chapter 3: On-Chip Millimeter-Wave Integrated Absorptive Bandstop Filter in (Bi)-CMOS |    |

| Technology                                                                            | 47 |

| 3.1 Introduction                                                                      | 47 |

| 3.2 Design of On-Chip Passive-Integrated Millimeter-Wave Absorptive BSF               | 49 |

| 3.3 Experiment Results.                                                               | 55 |

| 3.4 Furtherwork                                                                 | 58  |

|---------------------------------------------------------------------------------|-----|

| 3.5 Conclusions                                                                 | 60  |

| Chapter 4: Millimeter-Wave Wide-Band Bandpass Filter in CMOS Technology Using a |     |

| Two-Layered Highpass-Type Approach with Embedded Upper Stopband                 | 62  |

| 4.1 Introduction                                                                | 62  |

| 4.2 On-Chip Passive-Integrated Millimeter-Wave Wide-Band BPFs                   | 64  |

| 4.2.1 Structure, Operational Principle and Parametric Analysis                  | 64  |

| 4.2.2 Simplified Equivalent Lumped-Element Circuit Model                        | 68  |

| 4.2.3 Extension of the Designed BPF presented in Section 4.2.1                  | 71  |

| 4.3 Experimental Results                                                        | 76  |

| 4.3.1 Fabrication, Simulation and Measurement                                   | 76  |

| 4.3.2 Comparison with the State-of-the-Art designs                              | 80  |

| 4.4 Conclusions                                                                 | 81  |

| Chapter 5: RF CMOS Broad-Band Bandpass Filters with 3-D Inductors               | 83  |

| 5.1 Introduction                                                                | 83  |

| 5.2 UWB Bandpass Filters with 3-D Inductors                                     | 85  |

| 5.2.1 Four-3-D-Inductor BPF Cells designing                                     | 85  |

| 5.2.2 Equivalent Lumped-Element Circuit                                         | 87  |

| 5.3 Experimental Results                                                        | 92  |

| 5.4 Conclusions                                                                 | 96  |

| Chapter 6: Conclusions and Future Works                                         | 97  |

| 6.1 Conclusions                                                                 | 97  |

| 6.2 Future Work                                                                 | 98  |

| Abbreviations                                                                   | 100 |

| Ribliography                                                                    | 104 |

# LIST OF FIGURES

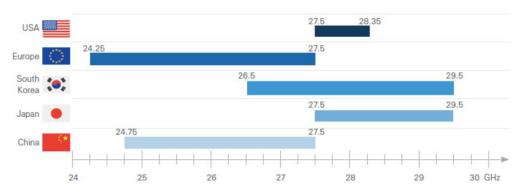

| Figure 1.1. The pre-defined mm-wave spectrum for 5G NR                                                              | 13      |

|---------------------------------------------------------------------------------------------------------------------|---------|

| Figure 2.1. Metal stack-up in a 0.13-µm SiGe (Bi)CMOS                                                               | 27      |

| Figure 2.2. Schematic of the presented 5th-order symmetric interdigital BPF in [30]                                 | 29      |

| Figure 2.3. Die microphotograph of the designed BPF in Fig. 2.2                                                     | 28      |

| Figure 2.4. 3D view of the presented interdigital resonator and its equivalent circuit mo-                          | del     |

| in [31]                                                                                                             | 30      |

| Figure 2.5. Layout and die microphotograph of the designed BPF in Fig. 2.4                                          | 31      |

| Figure 2.6. Different resonator structures with loaded ECC [43]                                                     |         |

| Figure 2.7. Implementation BPF using ECC method [43]                                                                |         |

| Figure 2.8. Die microphotograph [43]                                                                                | 29      |

| Figure 2.9. The top-view of the presented 4 <sup>th</sup> -order cross-coupled SIR-MH BPF [33]                      | 34      |

| Figure 2.10. Die photograph of the 4th-order cross-coupled SIR-MH Bandpass Filter [3                                |         |

|                                                                                                                     | _       |

| Figure 2.11. The designed BPF in [9], (a) the 3-D view, and (b) die microphotograph [3                              | _       |

| Figure 2.12. The 2-D view of the designed BPF using stepped-impedance resonator in [                                | [35].   |

| Figure 2.13. The 3-D view of the designed BPF shown in Fig. 2.12 [35]                                               |         |

| Figure 2.15. The top- and 3-D views for the designed filter in [36]                                                 | 38      |

| Figure 2.16. Illustration of the conventional combline type BPF [37]                                                |         |

| Figure 2.17. The top-view of the designed BPF shown in Fig. 2.16                                                    | 39      |

| Figure 2.18. The 3-D view of the 2 <sup>nd</sup> combline-based BPF presented in [38]                               | 38      |

| Figure 2.19. (a) Metal stack-up of a BiCMOS 9MW technology (b) the 3-D view of the                                  |         |

| S-CPW-based design [39]                                                                                             | 41      |

| Figure 2.20. Die microphotograph of the designed 1st-order resonator shown in Fig. 2.19                             |         |

| Figure 2.21. The top- and the cross-section-views of the broadside-coupled resonator                                |         |

| presented in [41]                                                                                                   | 41      |

| Figure 2.22. A BPF designed in [42], (a) 2D view of the three layers of the presented                               |         |

| edge-coupled resonator, (b) the top view of the designed BPF with dimensions                                        | 43      |

| Figure 2.23. The designed filter with illustration of [44]                                                          |         |

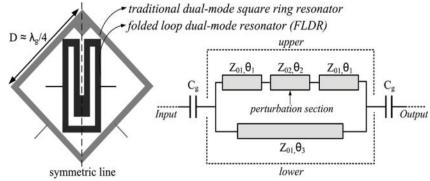

| Figure 2.24. The structure of the folded loop dual mode resonator with its transmission                             |         |

| model [44]                                                                                                          |         |

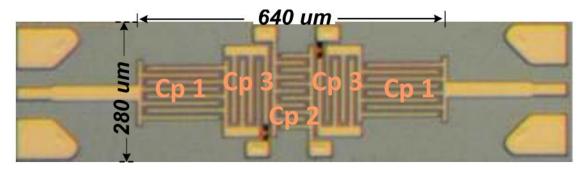

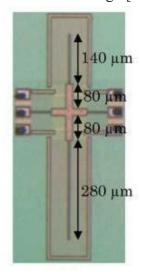

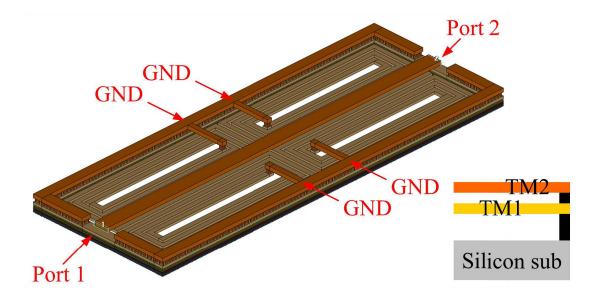

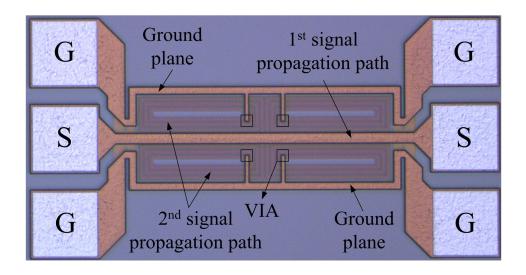

| Figure 3.1. Designed on-chip passive-integrated mm-wave absorptive BSF. (a) Layout                                  |         |

| (3-D view). (b) Layout (2-D view with indication of dimensions in μm). (c)                                          |         |

| Equivalent lumped-element circuit ( $Z_0$ : reference impedance; $f_0$ : BSF center frequence                       | ency:   |

| $R_{\rm p}$ , $L_{\rm p}$ , and $C_{\rm p}$ : resistance, inductance, and capacitance of the lossy parallel-type    |         |

| lumped-element resonators; J variables: 90°-admittance-inverter constants)                                          | 52      |

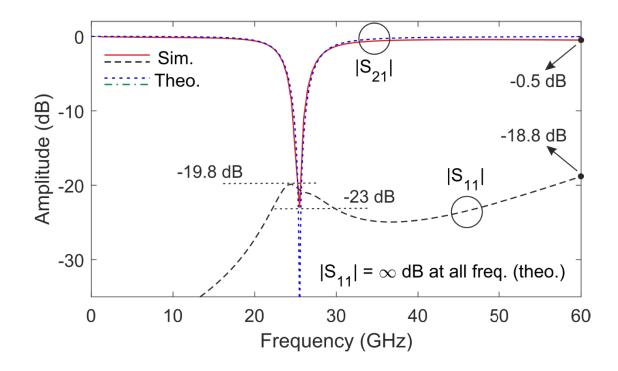

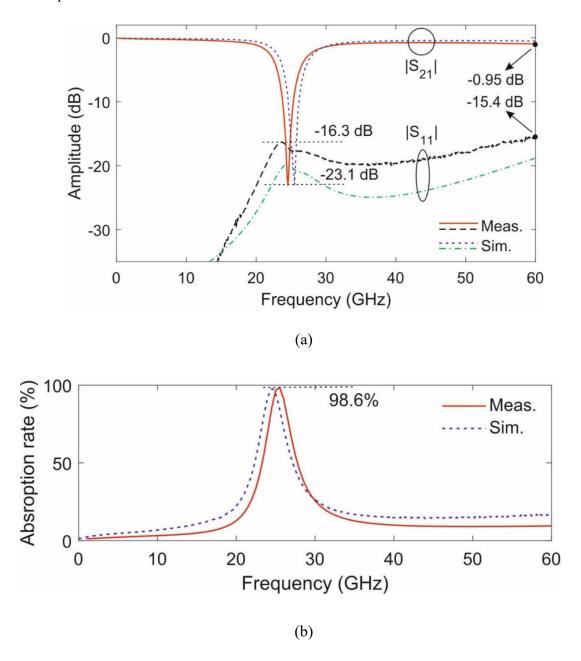

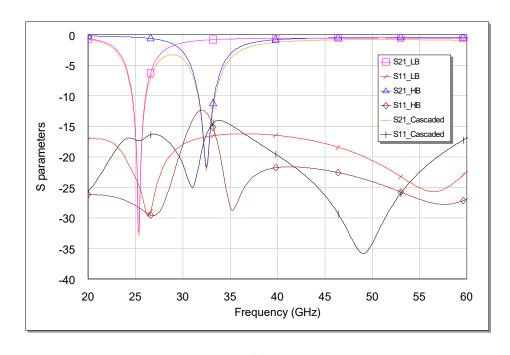

| Figure 3.2. EM-simulated [layout in Figure 3.1(a) and (b) with dimensions therein                                   |         |

| indicated] and theoretical [equivalent lumped-element circuit in Figure 3.1(c) for 2                                | $Z_0 =$ |

| 50 Ω, $f_0 = 25.5$ GHz, and BW <sub>3dB</sub> = 4.58 GHz: $J_0 = J_1 = 0.02$ S, $J_2 = 0.01$ S, $R_p = 100$         |         |

| $L_p = 56.05$ pH, and $C_p = 0.693$ pF] power transmission ( S <sub>21</sub>  ) and reflection ( S <sub>11</sub>  ) | ,       |

| responses of the designed absorptive BSF53                                                                       |

|------------------------------------------------------------------------------------------------------------------|

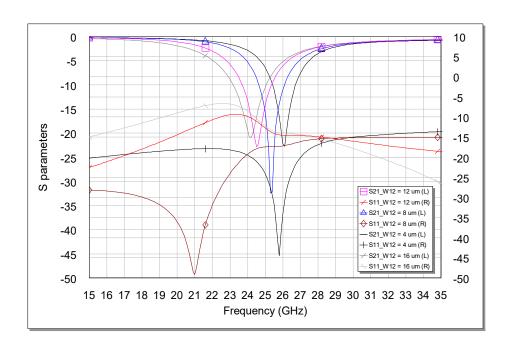

| Figure 3.3. EM-simulated S-parameters of the designed BSF with different values of W12.                          |

| Note: the left and right Y-axes are referred to $S_{21}$ and $S_{11}$ , respectively                             |

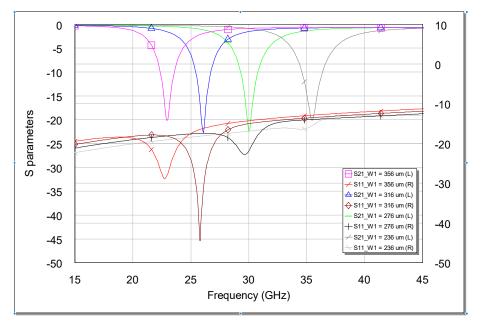

| Figure 3.4. EM-simulated S-parameters of the designed BSF with different values of W1.                           |

| Note: the left and right Y-axes are referred to $S_{21}$ and $S_{11}$ , respectively                             |

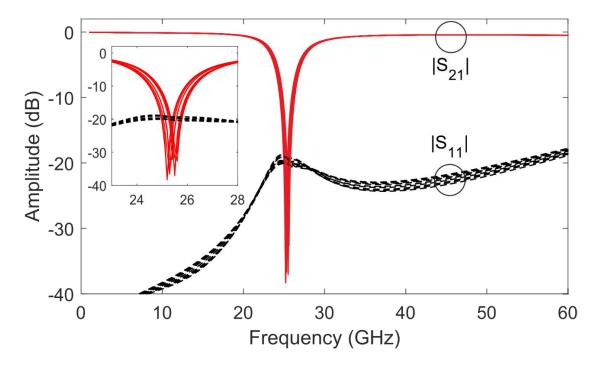

| Figure 3.5. Sensitivity analysis of the designed on-chip passive-integrated mm-wave                              |

| absorptive BSF in terms of EM-simulated power transmission ( $ S_{21} $ ) and reflection                         |

| $( S_{11} )$ responses (variation of 5% of line widths and spacing with regard to the values                     |

| indicated in Fig. 3.1 (b))                                                                                       |

| Figure 3.6. Measurement results of the designed BSF, (a) simulated and measured power                            |

| transmission ( $ S_{21} $ ) responses of the designed absorptive BSF, and (b) simulated and                      |

| measured power-absorption rates of the designed absorptive BSF. Note that for a                                  |

| classic reflective-type BSF the power-absorption rate would be theoretically equal to                            |

| 0% at any frequency56                                                                                            |

| Figure 3.7. Die microphotograph of the designed BSF in Figure 3.5                                                |

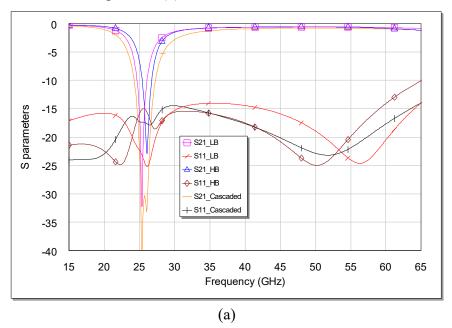

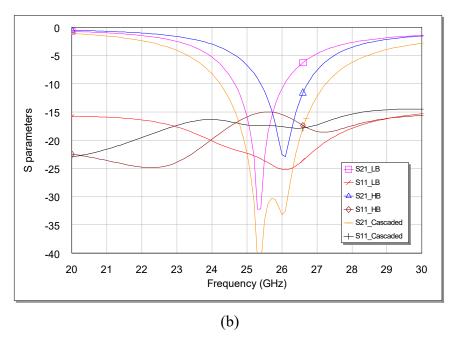

| Figure 3.8. EM simulated S-parameters for two cascaded BSFs. Note: the operation                                 |

| frequencies of these two BSFs are close to each other                                                            |

| Figure 3.9. EM simulated S-parameters for two cascaded BSFs. Note: the operation                                 |

| frequencies of these two BSFs are far from each other                                                            |

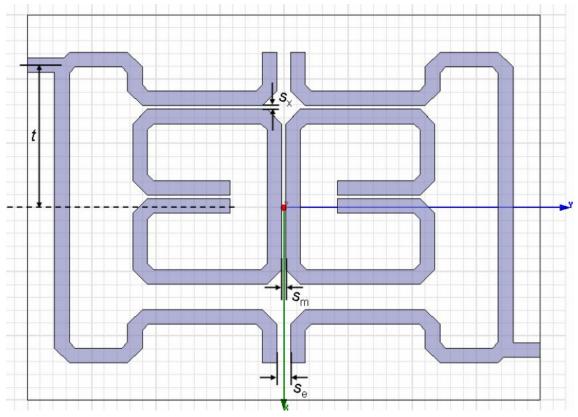

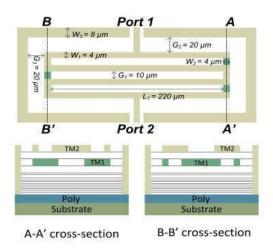

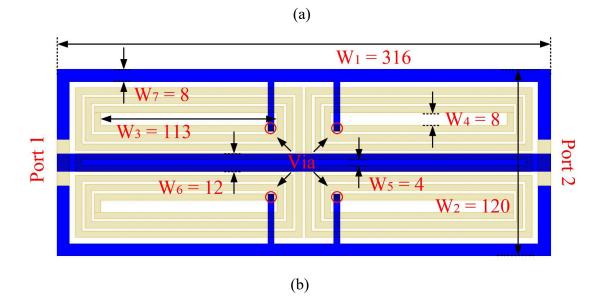

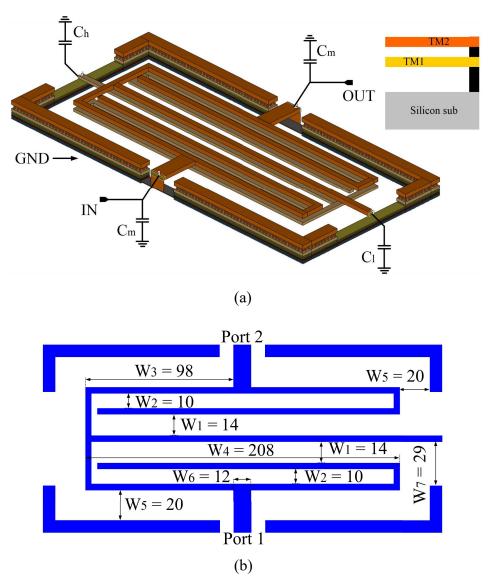

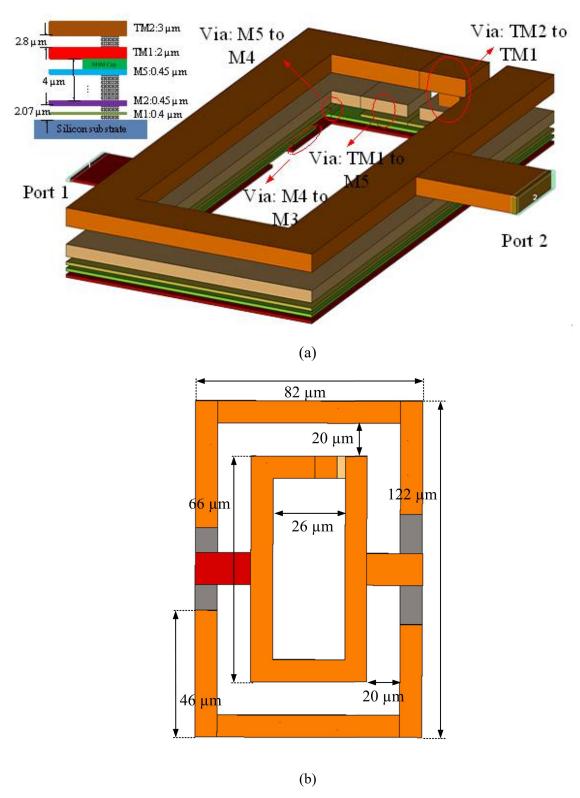

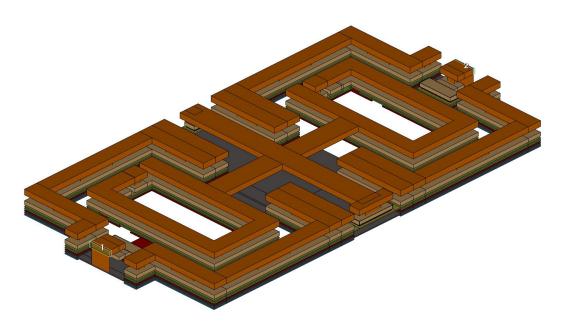

| Figure 4.1. Designed on-chip CMOS passive-integrated mm-wave wide-band BPF. (a)                                  |

| Layout (3-D view). (b) Layout (2-D view of the top layer with indication of                                      |

| dimensions in µm)65                                                                                              |

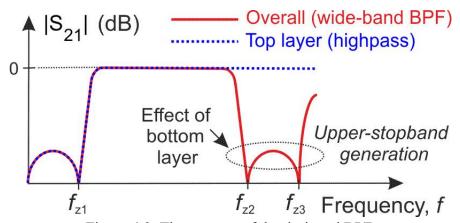

| Figure 4.2. The concept of the designed BPF                                                                      |

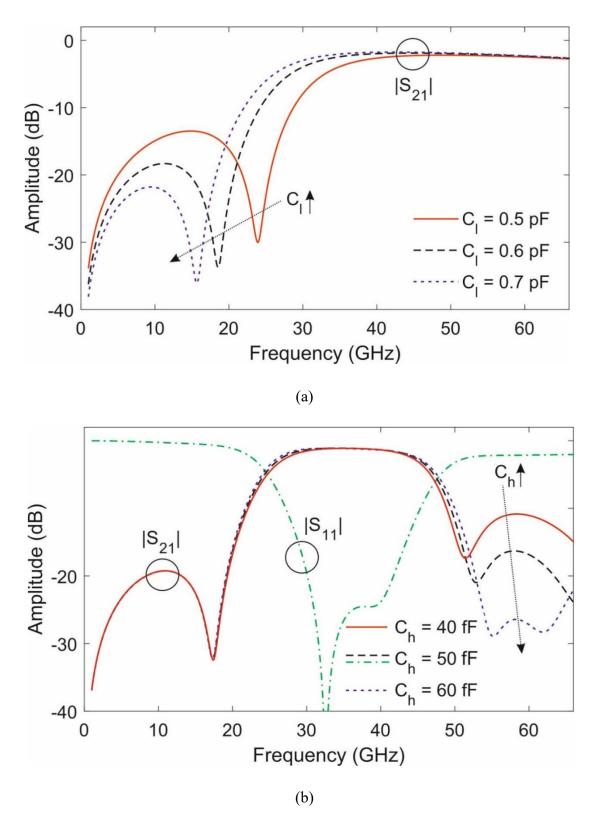

| Figure 4.3. (a) EM-simulated power transmission response ( $ S_{21} $ ) of the top-layer structure               |

| for different values of $C_l$ : lower-TZ control ( $C_m = 0.16 \text{ pF}$ ). (b) EM-simulated power             |

| transmission response ( $ S_{21} $ ) and input-reflection responses of the overall wide-band                     |

| BPF for different values of $C_h$ : upper-TZ control ( $C_m = 0.16 \text{ pF}$ and $C_l = 0.6 \text{ pF}$ ). The |

| values of the physical dimensions in all cases are as indicated in Figure 4.1(b) 67                              |

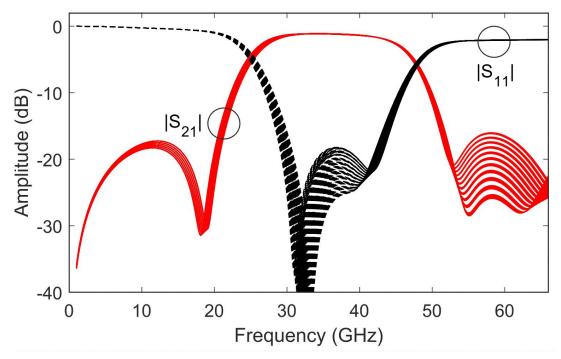

| Figure 4.4. Sensitivity analysis of the designed on-chip CMOS mm-wave wide-band BPF                              |

| in terms of EM-simulated power transmission ( $ S_{21} $ ) and reflection ( $ S_{11} $ ) responses               |

| [variation of 5% of line widths and of 10% of capacitance values with regard to the                              |

| values indicated in Figure 4.1(b)]68                                                                             |

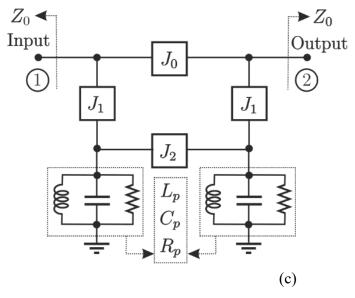

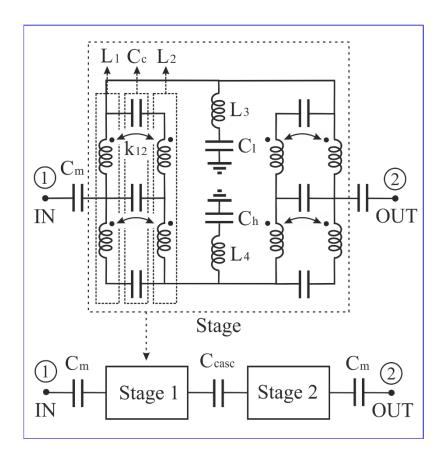

| Figure 4.5. Equivalent lumped-element circuit model of the passive-integrated mm-wave                            |

| wide-band BPF in Figure 4.1 and application to an in-series-cascade two-stage BPF                                |

| design70                                                                                                         |

| Figure 4.6. Comparison in terms of power transmission ( $ S_{21} $ ) and input-reflection ( $ S_{11} $ )         |

| responses between the EM-simulated results in Figure 4.1 (b) ( $C_h = 50$ fF) and its                            |

| equivalent lumped-element circuit model in Figure 4.5 ( $C_m = 0.2 \text{ pF}$ , $C_c = 55 \text{ fF}$ , $C_l =$ |

| 1.1 pF, $C_h = 60$ fF, $L_1 = L_2 = 0.16$ nF, $k_{12} = 0.5$ , $L_3 = 0.1$ nH, and $L_4 = 0.08$ nH)              |

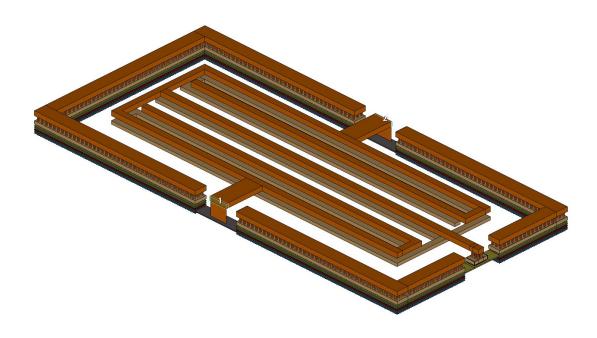

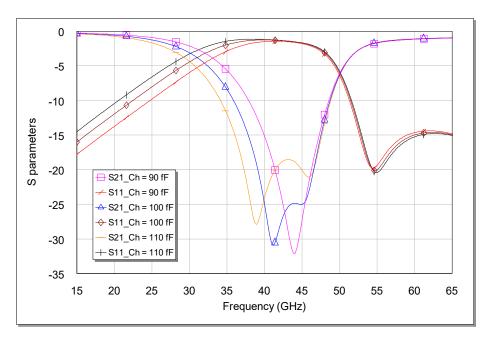

| Figure 4.7. The 3-D view of the Design 2                                                                         |

| Figure 4.8. Simulated frequency responses of Design 2 with different values of Ch applied.                       |

| 72                                                                                                               |

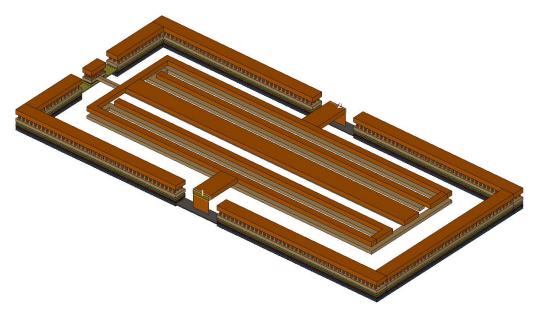

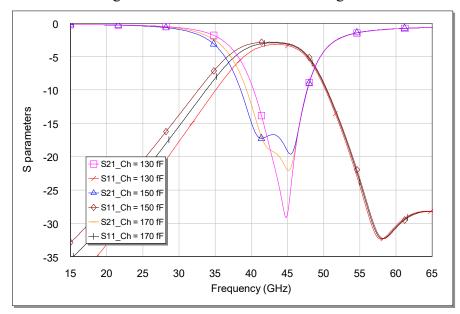

| Figure 4.9. The 3-D view of the Design 3                                                                         |

| Figure 4.10. Simulated frequency responses of Design 3 with different values of Ch applied                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

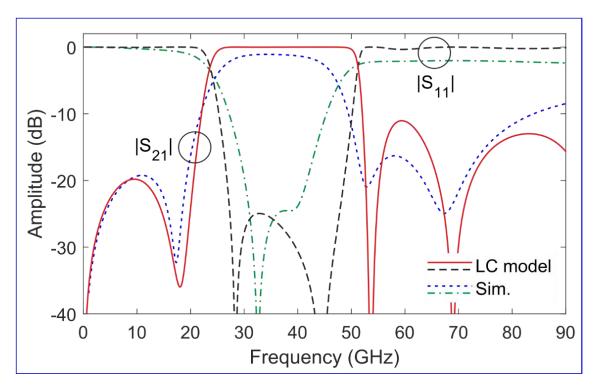

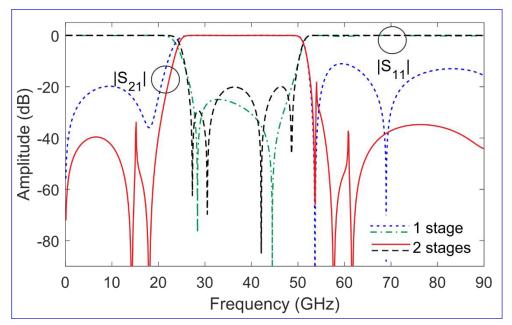

| Figure 4.11. Comparison in terms of power transmission ( $ S_{21} $ ) and input-reflection ( $ S_{11} $ ) responses between the ideal lumped-element single-stage and two-stage designs in Figure 4.9. (single-stage design: same parameters as in Figure 4.6; two-stage design: $C_m = 0.3 \text{ pF}$ , $C_c = 53 \text{ fF}$ , $C_l = 1.6 \text{ pF}$ , $C_h = 63 \text{ fF}$ , $C_{\text{casc}} = 0.2 \text{ pF}$ , $L_1 = 0.2 \text{ nF}$ , $L_2 = 0.154 \text{ nF}$ , $L_1 = 0.53$ , $L_2 = 0.1 \text{ nH}$ , and $L_4 = 0.089 \text{ nH}$ ) |

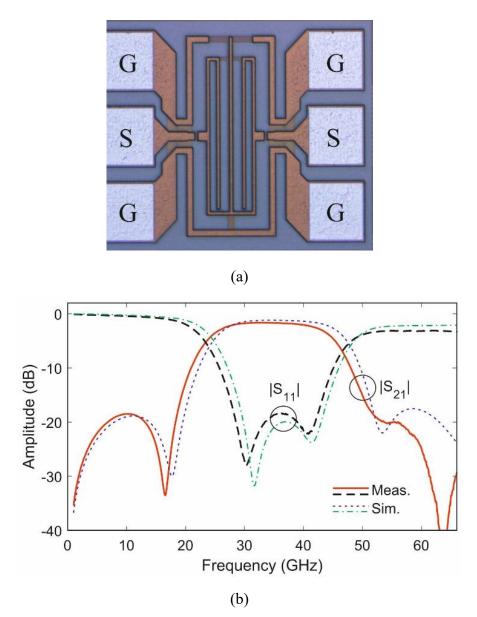

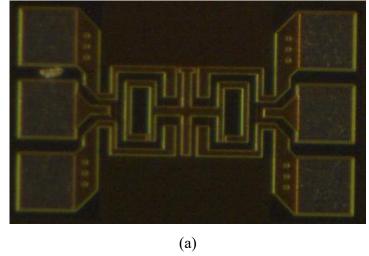

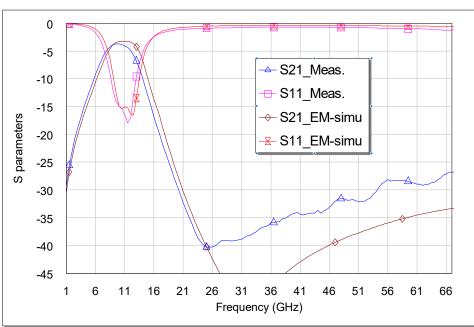

| Figure 4.12. Manufactured on-chip CMOS mm-wave wide-band BPF prototype (Design 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (a) Die microphotograph. (b) Simulated and measured power transmission ( $ S_{21} $ ) and                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

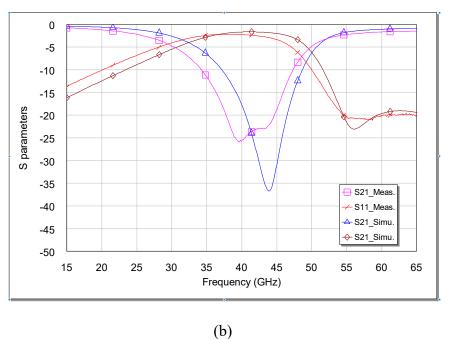

| input-reflection ( $ S_{11} $ ) responses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.13. Manufactured on-chip CMOS mm-wave resonator prototype, Design 2. (a) Die microphotograph. (b) Simulated and measured power transmission ( $ S_{21} $ ) and                                                                                                                                                                                                                                                                                                                                                                            |

| input-reflection ( $ S_{11} $ ) responses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

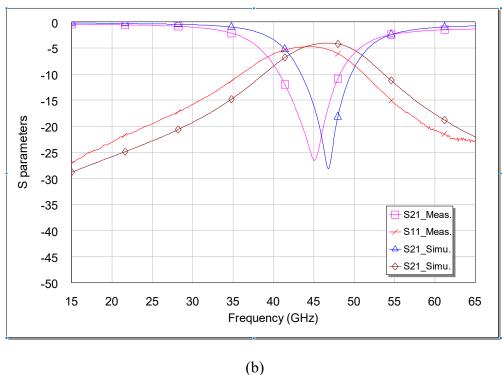

| Figure 4.14. Manufactured on-chip CMOS mm-wave resonator prototype, Design 3. (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Die microphotograph. (b) Simulated and measured power transmission ( $ S_{21} $ ) and                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| input-reflection ( $ S_{11} $ ) responses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

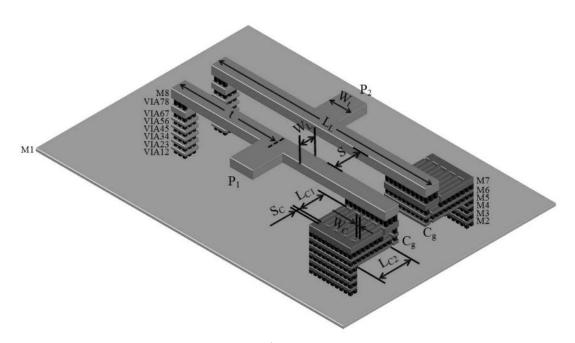

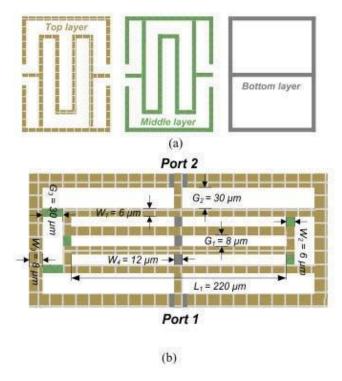

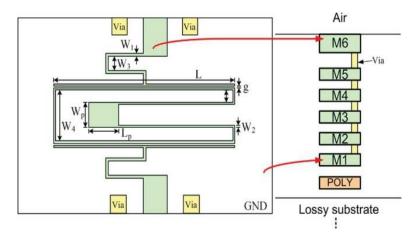

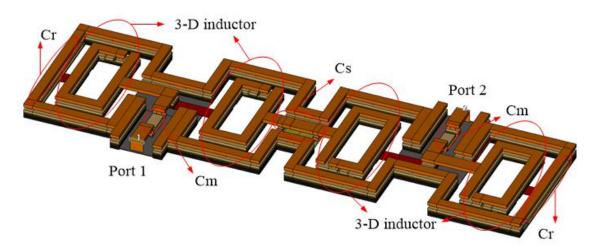

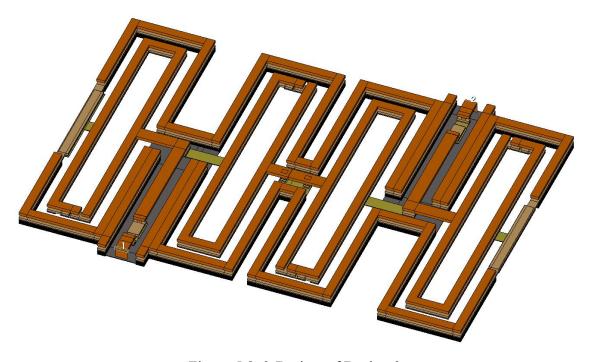

| Figure 5.1. Geometrical view of the 3-D inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.2. Series-cascading inductors in Figure 5.1 with MIM capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

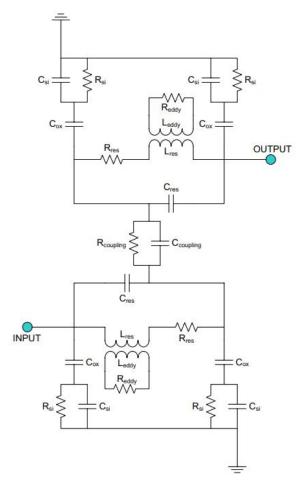

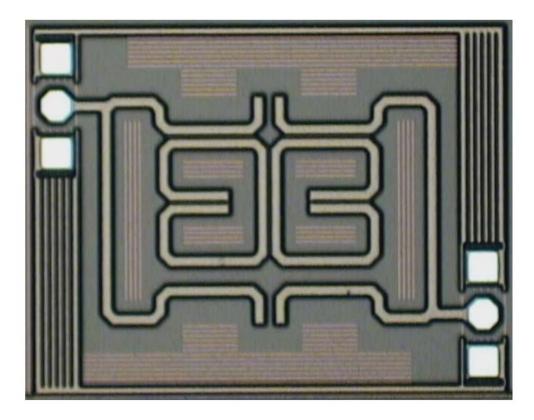

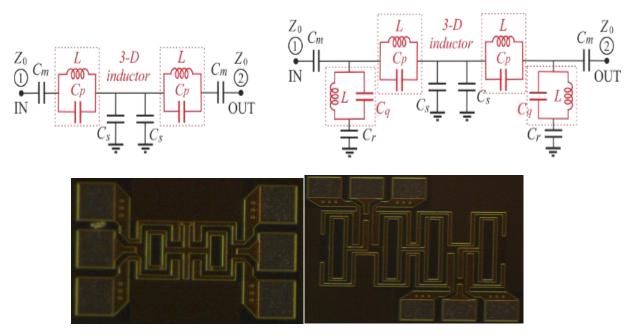

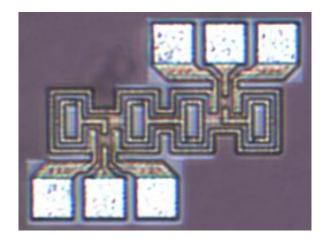

| Figure 5.3. Lumped-element model and microphotograph of the developed BPF chips with                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3-D inductors (red color: 3-D inductors with parasitic capacitances $C_p$ and $C_q$ ). and                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Filter I./ Filter II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

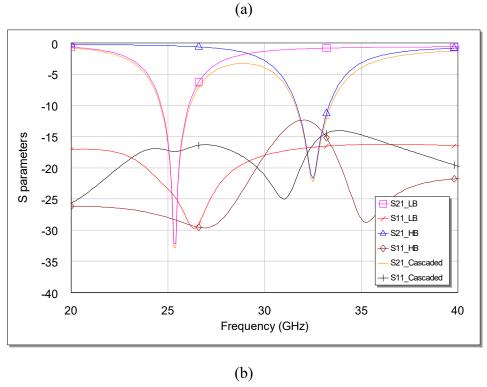

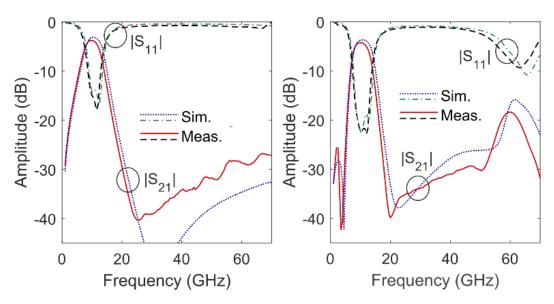

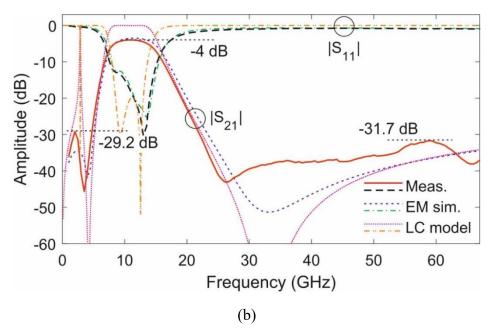

| Figure 5.4. Simulated and measured power transmission ( $ S_{21} $ ) and reflection ( $ S_{11} $ )                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| responses of the developed RF CMOS wide-band BPF chips with 3-D inductors for sdFilter I. and Filter II                                                                                                                                                                                                                                                                                                                                                                                                                                            |

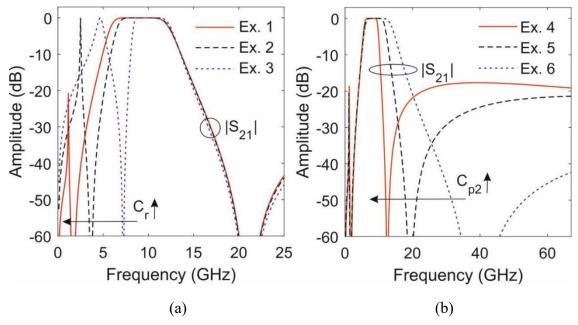

| Figure 5.5. TZ control in ( $ S_{21} $ ) of the lumped-element circuit in Figure 5.3. (a) Lower-TZ                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| control (b) Upper-TZ control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

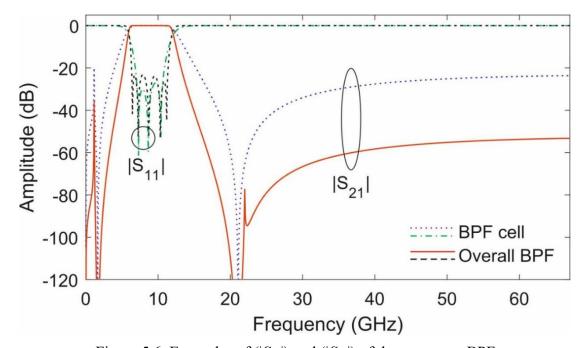

| Figure 5.6. Examples of $( S_{21} )$ and $( S_{11} )$ of the two-stage BPF90                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 5.7. 3-D view of Design 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.8. 3-D view of Design 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

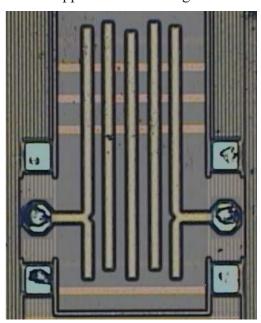

| Figure 5.9. Design 1. (a) Fabricated device (b) $( S_{21} )$ and $( S_{11} )$ comparison between                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| designed and experimental results93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

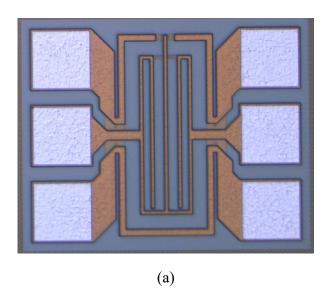

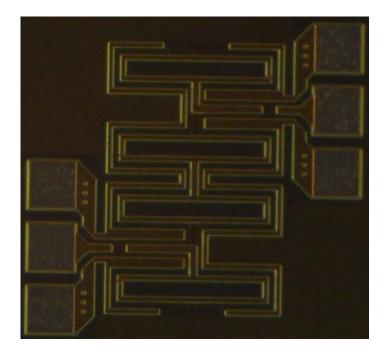

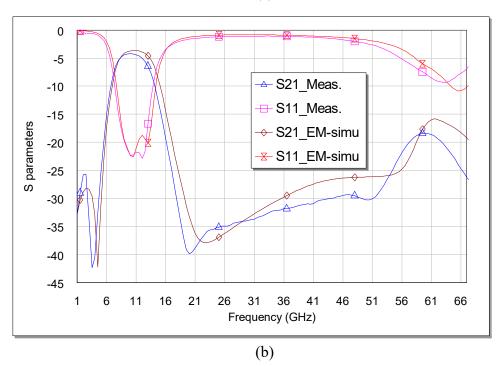

| Figure 5.10. Design 2. (a) Die microphotograph (b) EM-simulated, and measured power                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| transmission ( $ S_{21} $ ) and reflection ( $ S_{11} $ ) responses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 5.11. Design 3. (a) Die microphotograph (b) EM-simulated, and measured power                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| transmission ( $ S_{21} $ ) and reflection ( $ S_{11} $ ) responses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# LIST OF TABLES

| Table 4.1 Performance comparisons with state-of-the-art on-chip BPFs | 81 |

|----------------------------------------------------------------------|----|

| Table 5.1 Comparisons with state-of-the-art BPFs                     | 96 |

## **Abstract**

In any given wireless communication system, the RF filter is an indispensable device. This is especially true for the RF front-end module, which is designed to process the selecting frequency band for different RF signals, and reduce any spurious items in the transmitter and receiver chain and interference signals outside the whole transceiver system. As far as on-chip filtering solutions are concerned, recently devised solutions mainly concentrate on different types of semiconductor processes, namely gallium arsenide (GaAs), and silicon-based ones, such as CMOS and silicon germanium (SiGe). In this research, some fundamental design challenges, especially device miniaturization, will be fully addressed through some novel design methodologies. To explain the low-cost requirements for both prototyping and mass production, a silicon-based technology is used. Consequently, the designs presented in this thesis may be suitable for some high-performance on-chip transceiver systems. In this thesis, designed miniaturized on-chip passive filters in silicon-based technology will be presented. Both BSF and BPFs are implemented and characterized in the mm-wave frequency region. Three unique design approaches will be presented.

The first approach is used to design an on-chip absorptive BSF in a 0.13-µm complementary metal-oxide-semiconductor CMOS technology. Taking advantage of metal stack-up provided in this technology, this design utilizes a two-path transversal configuration in a multi-layer structure. It consists of a direct transmission line (TL) for the main path and two lossy edge-grounded spiral-shaped resonators. The TL is implemented in the top-most metal layer, namely TM2, while the resonators are implemented in a layer below TM2, known as TM1. They are coupled with each other through a broadside-coupled structure. Using this approach, a 24.5-GHz BSF is designed and it has a 10-dB-attenuation-referred absolute bandwidth of 1.54 GHz and maximum attenuation 23.1 dB. The maximum power attenuation level in the pass band region is 0.95 dB at 60 GHz and the size excluding pads is 0.316 × 0.12 mm². A good

agreement between simulated and measured results is obtained. The performance of this design can be considered for some systems which are isolator-less mm-wave transceivers.

The second approach serves to design a wideband BPF also based on a broadside-coupled structure. The design strategy for this work is that a highpass-type filtering response is obtained through a structure that is implemented by TM2, and an upper stopband frequency response is achieved by the bottom layer when the two structures are coupled. Consequently, a composite overall quasi-elliptic-type wide-band BPF functionality can be obtained. Using this approach for BPF design, a wideband 34.5-GHz BPF is devised. It has a 3-dB absolute bandwidth equal to 21.1 GHz and the minimum in-band insertion loss is 1.6 dB which is 0.264 × 0.124 mm² in size. This design is suitable for miniaturized broad-band RF transceivers when compared with previously published literature.

The final part of this work is an investigation of wideband BPF design using 3-D lumped inductors. In contrast to conventional studies that have been published in the literature, the approach presented here utilizes parasitic capacitances from the implemented 3-D inductor to introduce a transmission-zero (TZ) at upper stopband. For the purpose of proof-of-concept, a BPF prototype is designed and implemented. The on-wafer measurements show that the designed filter operates at center frequency with a 68.5% 3-dB bandwidth. Due to the proposed 3-D inductors, the overall size of the prototype excluding measurement pads is only 0.054 mm<sup>2</sup>.

# **Chapter 1 Introduction**

With progress being made in the miniaturization of today's monolithic microwave integrated circuit (MMIC) transceiver systems, devices of a considerably compact size and high performance built on integrated circuits, also known as chipsets, are becoming increasingly accepted as an ideal solution. They offer new kind of wireless communications that can meet the emerging challenges, such as low cost and wideband requirements. Section 1.1 introduces the background of the thesis for both the mm-wave frequency range illustration and compact size of system advantages. Section 1.2 looks at the challenges and motivations behind this thesis from the technology and application points of view. Section 1.3 explains the main objectives and scope of this thesis. For the last, Section 1.4 describes how this thesis is structured.

# 1.1 Background

## 1.1.1 5G and Millimeter-Wave

The 5th-Generation New Radio (5G NR) networks are introducing the latest wireless revolution which supports not only significantly faster mobile broadband speeds but also much lower latencies than previous generations. These unique features make many emerging applications feasible. It is now possible to autonomous vehicles which are fully equipped with ultra-wideband and high-speed communication devices, which could safely steer through and maintain awareness of the traffic around them using the 1-ms latency provided by 5G networks. Moreover, billions of Internet-of-Things (IoTs) devices may be adding their data contributions to 5G networks within the next decade, giving people instant access to information about different items and environments around them. Currently, 5G NR mainly employs sub-6 GHz which significantly limits its performance. To reach its full potential, one of the cornerstone technologies required is to develop low-cost and miniaturized RF front-end modules (FEMs) operating at millimeter-wave (mm-wave) frequencies [1-20].

The global 5G system integration market size is expected to reach US\$43.7 billion by 2027 [21]. Some countries have pre-defined some spectra for the usage of 5G NR, which is shown in Figure 1.1. The implementation of new 5G NR standards and the use of mm-wave spectrum is expected to be revolutionary and will provide seamless connectivity for an increasing number of users and networked devices. As 5G mm-wave starts to be deployed in low-cost, small-cell networks using massive MIMO antennas to deliver as much as 20 Gbps download rates to users, the great promise of 5G NR mm-wave will become apparent. At that point, there is likely to be an explosion in the number of new applications and deployment scenarios that exploit the new technology.

Figure 1.1. The pre-defined mm-wave spectrum for 5G NR. [1]

Additionally, the 5G NR technology will help to safeguard Australian businesses in a fast-growing and rapidly changing digital world. The mm-wave technology will be found everywhere – from the eyes of autonomous vehicles, to ultra-high-speed backhaul links that can match the performance of optical fibers at a fraction of the cost, ultimately providing hundreds of sensors per person, and making the tasks of daily life easier. Therefore, this project will significantly benefit end-users in deploying mm-wave technology for not only wireless industries, but also advanced manufacturing such as Industry 4.0.

Currently, integrated circuits (ICs) are the core components for not only microwave and mm-wave communication systems, but also radar sensing systems. High-performance ICs are playing a critical role in current technology development. People from both academia and industry are looking for solutions to improve the

performance of RF devices operating in the 5G mm-wave bands, especially the increasing demands for device miniaturization and integration. In this scenario, designing high-performance RFIC for a qualified 5G NR mm-wave transceiver is required and must attain a higher level. Moreover, given the diversity of today' applications, some specific RF on-chip devices are needed to accommodate different kinds of application scenarios. Returning to the topic of this thesis, on-chip integrated RF filters, especially with the mm-wave frequency range, new design approaches and innovative electromagnetic (EM) structures are required for on-chip filtering solution implemented in low-cost silicon-based technology.

# 1.1.2 Filtering Technology Development

Over a century ago in 1915, the German scholar K.W. Wagner designed the first "Wagner filter" with inductors and capacitors as the unit structure [22]. Building on this, the American scientist G. A. Canbell used the image parameter method to conduct a theoretical analysis of the filter design. This invention directly promoted the birth of the first multiplexing system worldwide in 1916. In 1937, W. P. Mason and R. A. Sykes used the *ABCD* matrix to successfully extract the phase parameters and attenuation characteristics of the filter [23]. By the 1950s, the theory and practical application of passive filters had gradually matured. In recent years, with the emergence of many different new materials and the continuous updating of various integration processes, the development of microwave filters has significantly improved. This is especially the case with the emergence of personal computers. The subsequent appearance of various electromagnetic simulation software has reduced the difficulty of filter designs.

Furthermore, a few milestones in the history of filter design should be acknowledged. The American scientist S. B. Cohn deduced the theory of direct coupling resonant cavity filter based on the low-pass prototype structure in 1957 [24]. In 1966, the American scientist Kurzrok and his team introduced cross-coupling into the multi-cavity, and successfully designed the multi-cavity filter [25]. In 1997, the

insertion loss of the filter was introduced and used with polynomial function to characterize filters so that a frequency response could be obtained. In 1999, Cameron invented the cross-coupling method to generate transmission zeros [26]. This analytical synthesis method can achieve the asymmetry in frequency response. In 2000, Amari proposed the non-resonant node technology and used an optimized method to extract the coupling matrix [27]. The biggest advantage of this technology is that the generation of transmission zeros (TZs) does not require cross-coupling of diagonal components. Instead it requires horizontal and vertical components to produce the transmission zero point.

In modern applications, different kinds of RF filter are used to build different systems. Cavity filters are widely used in communication equipment such as base stations because of their very low insertion loss, extremely high Q value and good out-of-band suppression. However, such designs are very difficult to be miniaturized and integrate them with other technologies. Conversely, the low-temperature co-fired ceramic (LTCC) technology can achieve miniaturized designs which are able to be "integrated" with other technologies [28]-[29]. Therefore, it has attracted worldwide attention from industry and academia. However, there are still some disadvantages such like complex processing techniques, large in-band insertion loss and high cost. To further reduce fabrication cost and minimize the physical sizes of the designed filters, development of fully-integrated filters, also known as on-chip filters, has been ongoing in the last decade [30]-[63]. Taking advantage of Moore's law, there are usually multiple metal layers which could be used in any modern silicon-based technologies. In particular, there is at least one thick metal layer that is designed for low-loss microwave circuits [64]-[70]. Moreover, unlike the conventional approach for microwave planar circuits design that usually use distributed elements, such as transmission lines and open/shot stubs, there are lump elements. These include, for example, capacitors and inductors and even transformers, could be used for filter design, which could significantly reduce the physical dimensions of the microwave filter.

Advances in semiconductor and integrated circuit (IC) technologies will play significant roles in developing the complex hardware of these emerging technologies. It is of great interest to establish a low-cost integrated circuit solution for 5G systems, Internet-of-Things module, big data networks technologies and mm-wave enabled radio circuits [71]-[80]. The components for mm-wave enabled circuits and systems are both active and passive, and furthermore traditionally expensive and cumbersome in size. These have garnered the attention of many firms in the semiconductor industry who are developing high-frequency devices, and they need to create a cost-effective, high-performance device with a smaller footprint. The emergence of low-cost mm-wave devices has evolved through research carried out throughout the world. Recent developments of silicon-based technology allow the implementation of low-cost chips which are suitable for a broad consumer market. For instance, the combination of cost-effective CMOS technology that can now operate in the mm-wave frequency band, allowing the design of a high-gain, phase array antenna, strengthens the viability of mm-wave radio communication [71]-[74].

## 1.1.3 Advanced Semiconductor Technologies

The IC fabrication is a complex and expensive process. The choice of a specific fabrication technology will depend on a number of specification requirements including cost, availability and circuit component capabilities. The technology scaling is another critical factor for IC design. In 1965, Gordon Moore, the co-founder of Intel Corporation, predicted that the number of transistors that would fit in on an integrated circuits chip will double every year. This forecast has held true for more than 50 years [64]-[70]. The key technology concerning this development reflects on the further evolution in the complexity of ICs by building systems in which all the individual components are assembled in circuit blocks. Included here are radio-frequency front-end, RAM/DRAM memory and digital logic, which are incorporated into a single chip substrate. Moore's Law was an elegant prediction of how an IC has become

smaller and cheaper over the years. Moreover, the law has been used by industries for several decades as they set targets for the development, marketing and sale of their new products. Evidently, the law serves as a driving force for social change and economic growth [66].

Nowadays, semiconductor businesses have successfully demonstrated technology scaling down to the sub-micron level. This has allowed both analog and digital circuits to be integrated on the same substrate [81]-[83]. This began during the 1920s when the active devices could operate at several hundreds of gigahertz in a silicon-based process. It is also around this time when foundries added the specialized feature of utilizing the thick metal layer for the back-end-of-line (BEOL) process [84]-[85]. The introduction of the new material during the BEOL process can help to improve chip performance, especially regarding the RF circuits. Innovations were made to the materials used for both the metal wires and the dielectric insulation in order to meet conductivity requirements and reduce the dielectric permittivity [85].

The twentieth century has witnessed a tremendous amount of technological change and growth, touching and improving the daily lives of people around the world. A good example of this version of Moore's law is the statement that appeared in one prominent business and technology journal, which states that: "Moore's law, celebrated as the defining rule of the modern world, states that the computer chip performance doubles every eighteen months" [15]. However, recently it is thought that Moore's law is expected to no longer be the main driving force for improving IC performance.

#### 1.1.4 Miniaturized Passive Devices

Towards to the end of Moore's law, the full potential of active devices has almost been reached. It is unclear how to further improve the overall performance of RFICs, while the operation frequency being pushed to the mm-wave region. We believe that a possible way to support the high-performance mm-wave RFIC design is to use passive-inspired strategies. In this thesis, we therefore focus on passive devices design and implementation for mm-wave applications. Passive devices are the main components used in RFICs such as inductors, capacitors and transformers. As their name implies, passive devices are electrical components that do not need any form of electrical power to operate, unlike active devices. Passive devices do not provide gain or amplification but instead, they provide attenuation as they always have gains of less than unity. Passive devices can increase current or voltage by an LC circuit, a series or parallel combination of inductor and capacitor, where they can store electrical energy from a resonant frequency. They can be designed individually or co-designed with other components to build and control complex signals and systems [89]-[96].

It is well known that IC design offers a significant advantage of developing a compact, lightweight design with enhanced performance, high reliability and cheaper manufacturing cost. These are the same for microwave and mm-wave ICs but sometimes the cost of fabrication is compromised. Thus, device miniaturization is very important. Microwave and millimeter-wave circuits can be implemented using either planar or non-planar technologies. Some examples of non-planar circuits are waveguides; these are often used for an application with a high-quality factor, low loss, and high power. On the other hand, planar circuits are popular due to their ease in integration. With the increase in frequencies in mm-wave applications, all metal lines are treated as either distributed- or lumped-elements.

# 1.2 Challenges and Motivations

This thesis aims to address the challenges incorporated in developing an integrated solution for the emerging technologies on the mm-wave application and the trend toward miniaturization. This thesis aims to explain the recent trend in the industry to design smaller, faster and less expensive electronic passive devices that function very reliably. They should be able to integrate both passive and active components on the same substrates. This thesis presents a methodology that could offer a promising

solution not only in device miniaturization but also a way to minimize the fabrication and packaging cost, which are also key advantages. Also, it diminishes the complexity of the system using higher functional passive silicon integration [80]-[89]. This offers excellent potential for future wireless communication systems including millimeter-wave and 5G networks.

As mentioned earlier, challenges including high performance, miniaturization and low cost have become the basic requirements of new wireless communication equipment. Furthermore the filtering performance of the RF front-end plays a vital role in the quality of the entire communication system. Millimeter-wave filters affect the channel selection, image suppression, noise attenuation, and High-Q oscillators. Therefore, how to design and process a fit filter product according to the given technical indicators in a short time is a challenge that researchers need to face. With the continuous innovation of new materials, new processes and semiconductor technologies, especially the emergence of a series of new technologies represented by LTCC, high temperature superconductors (HTS), and micro-electro-mechanical systems (MEMS), the filters of microwave frequency band have made great progress. At the same time, the existence of electromagnetic simulation software such like ANSYS HFSS, CST and Keysight ADS, has massively reduced the design/invention period of the filter made higher performance requirements achievable.

As a frequency selection component, the filter is expected to be able to transmit signals without distortion in a specific frequency range, and completely suppress useless signals and the interference coming out of the channel. In fact, this kind of filter with ideal channel characteristics is difficult to realize in practice. However, in the filter designing process, the characteristics of the filter should be as close as possible to achieve the ideal characteristics. Normally, the challenges of filter design are mainly focused on the passband bandwidth, insertion loss, return loss, out-of-band suppression, and the physical sizes of filters.

As is now widely known, 5G communication equipment is now moving in the direction of miniaturization and multiple frequency bands. Especially with the rapid development of mobile terminal equipment, more and more functions need to be fully integrated into one "smart" communication device. For example the size of the microwave filter has more stringent requirements. Also, with the introduction of more different communication standards, multi-band and ultra-wideband communications systems have progressed rapidly to satisfy access to information anytime and anywhere.

## 1.3 Contributions

The contributions this thesis makes to the knowledge on this subject are as follows:

- A mm-wave passive-integrated bandstop filter (BSF) using 0.13-µm SiGe with absorptive (reflectionless) behavior is reported. It can avoid the creation of RF-power reflections for filtered signals. It has a structure consisting of a two-path transversal configured into a multi-layer structure. This structure comprises separate parts, a direct transmission line for the main top layer metal and two lossy edge-grounded spiral-shaped resonators for the secondary bottom layer that are coupled between them and the top metal layer. This proposed design has a bandstop filtering (BSF) frequency response. The center frequency is located at 25.5 GHz. It can absorb the non-transmitted RF signal within its stopband region instead of returning it back to its input terminal. With this design, some RF front-end applications in mm-wave transceivers that require no earlier active stage can be realized to have less isolation and more energy-efficient [103].

- A novel mm-wave silicon-passive-integrated wide-band BPF based on a two-layered implementation is designed and demonstrated when 130-nm CMOS technology is used. This on-chip RF filter consists of a compact-size composite highpass approach in the top layer and is suitable for some broad-band

applications. An upper stopband is created by the bottom layer part coupled to the top layer to obtain a composite overall quasi-elliptic-type wide-band BPF functionality. The out-of-band TZs at both passband sides to the overall frequency response can obtain sharp-rejection filtering capabilities. The center frequency is located at 34.5 GHz while the 3-dB absolute bandwidth is 21.1 GHz which equates to 61.2% in relative terms. When compared with the other previously published wideband BPFs, this filter features a lower in-band insertion loss, compact die size, and a higher in-band power matching [104].

• A group of broadband RF bandpass filter (BPF) is designed in the bulk CMOS technology. The design is conducted by cascading a lowpass and a highpass filtering stage together. To minimize the footprint, 3-D inductors are extensively used whose parasitic capacitances are carefully exploited. In particular, the 3-D inductors turn the basic inductors into an LC tank, which enables an upper transmission zero (TZ) for the designed BPF to improve the selectivity and out-of-band power-rejection levels of the filters. The 3-dB fractional bandwidth is 68.5% for the RF bandpass filter design and is proof at the center frequency of 11 GHz. As the experimental results show, the minimum attenuation of the upper stopband is 31.7 dB for the test frequency range. It refers the filtering ability of the design BPF.

# 1.4 Organization of the Thesis

The thesis is structured as follows. In Chapter 2, the studies that have been done on this topic and the significance of microwave filters are evaluated. Starting from the low-pass prototype filter to the high-pass filter, the frequency conversion technologies are reviewed from the bandpass to the bandstop structure. The status of research into the filter is further indicated by reviewing the development of its foundry processes.

In Chapter 3, a millimeter-wave on-chip BSF with absorptive/reflectionless behavior is presented. Using such absorptive capability, the designed BSF could avoid the creation of RF-power reflections for filtered signals which can deteriorate earlier active stages in integrated RF front-end chains. It exploits a two-path transversal configuration in a multi-layer structure. Specifically, it is composed of a direct transmission line for the main path (top layer) and two lossy edge-grounded spiral-shaped resonators for the secondary path (bottom layer) that are coupled between them and to the main path. Thus, a sharp second-order stopband is created through destructive signal-interference effects between the two signal paths with intrinsic RF-power absorption within the volume of the lossy resonators.

In Chapter 4, an on-chip millimeter-wave (mm-wave) broad-band BPF developed in CMOS technology is reported. It is based on a two-layered implementation in which the circuit structure patterned in the top layer exhibits a highpass-type filtering response, whereas an upper stopband is created by the bottom-layer cell when coupled to the top-layer one to obtain a composite overall quasi-elliptic-type wide-band BPF functionality. The locations of the transmission zeros (TZs), which confer sharp-rejection capabilities to the total BPF, can be flexibly adjusted with the values of the capacitors that are employed in both layers. An equivalent lumped-element circuit model of the proposed wide-band BPF approach is also provided and applied to multi-stage BPF arrangements for higher-selectivity designs.

In Chapter 5, another RF broad-band BPF in bulk CMOS technology is reported. The reported solutions are mostly aimed at further reducing the physical footprint of the on-chip filter by means of different design strategies to generate cost-effective highly-integrated RF systems. Among these RF techniques, the employment of alternative 3-D inductor implementations, in which their parasitic capacitance is properly exploited to use them as *LC* tanks in more-compact BPF schemes that are prescient of some capacitors.

Finally, in Chapter 6 the conclusions of this thesis are drawn and further research avenues are suggested.

# **Chapter 2: Literature Review**

In any radio frequency system, the role of the filter is to transmit and attenuate the signal at a specific frequency. Thus, it has become an indispensable part of the wireless communication system. This chapter will mainly introduce the theoretical basis, related background of the on-chip filter, the comparison of the research status of different filters, and the previous literature.

In this thesis, some related literature is reviewed. The main features of those previous published works are summarized and to prepare the comparisons of the works in this thesis. In section 2.1, some theoretical basics are introduced. Section 2.2 summarizes the fabrication processes. Section 2.3 presents a review of related researches with the technical specifications. At last, the summary is given in Section 2.4.

## 2.1 Theoretical Basics

## 2.1.1 The Basic Technical Indicators of the Filter

Theoretically speaking, the insertion loss in the pass band of the ideal filter is zero, the attenuation of the stop band is infinite, and the roll-off slope of the transition band is 90 degrees. However, the actual filter performance cannot achieve these results. There are many technical parameters in the actual filter characterization, such as center frequency, bandwidth, insertion loss, stopband suppression, return loss, etc. All of these design parameters are linked to each other. The designer can achieve a better filtering outcome by continuously improving the basic parameters of the filter.

The basic technical indicators of the filter are listed below:

- Insertion Loss (IL): Under ideal conditions without any losses, the filter inserted into a system will not produce any attenuation at in-band. In reality, the filter consumes a certain amount of power in the radio frequency system. Insertion loss is defined as the ratio of the incident power to the power output by the filter load. As far as filter design in concerned, the smaller the insertion loss of the device can be, the better it will perform.

- Bandwidth: The bandwidth (BW) of the filter is simply the difference between the upper and lower cut-off frequencies. The cut-off frequency is usually defined with a 3-dB attenuation with in-band frequency response. Additionally, the parameter of fractional bandwidth (FBW) is employed for filter design, which is simply the ratio between center frequency and the BW. Based on the calculated values for FBW, the filter can be divided into a narrowband filter and a wideband filter.

- Ripple: Ripple describes the fluctuation amplitude of the signal in the passband

of the filter. It can be defined as the difference between the maximum and

minimum of the filter's amplitude-frequency response.

- Rejection: Rejection is an indicator that reflects the filter's ability to suppress

out-of-band interference signals or useless signals. The greater the out-of-band

suppression can be; the better filter performance it will achieve.

- Shape factor: Describes the degree of curve transformation of the filter transition. The larger the rectangular coefficient with the steeper the roll-off of the filter transition can be, the better the frequency selectivity it will achieve. Its expression is  $SF = \frac{BW\_3dB}{BW\_20dB}$ .

- Return loss (RL): Because the working principle of the filter is to let the signal

in the pass band pass, so that the signal in the stop band is reflected back to the signal source. This index is mainly used to describe the situation where the incident power is reflected back to the signal source. It is defined as the ratio of incident power to reflected power.

## 2.1.2 Design Methodologies for On-Chip mm-wave Filters

Passive components usually refer to and are not limited to commonly well-known capacitors, and inductors but also include most non-switching analog devices. The concept of integrated passive devices involves the fabrication of passive circuits on a common substrate instead of them having their own individual packages. In this thesis, we are primarily focused on resonator and filter designs. There are three different design methodologies for passive components as mentioned, and they are as follows. Firstly, the distributed-element-based designs, which utilizes the classical microwave theories, such as transmission line. For the second type, this is the lumped-element-based designs, which utilizes on-chip discrete passive components, such as inductor, capacitor and transformer. The third type combines the advantages of distributed- and lumped-element-based approaches, namely hybrid-element-based design. One typical design example for this kind of design is to utilize lumped-element capacitors, such as metal-insulator-metal (MIM) caps, to replace distributed-element capacitors. Consequently, the overall physical dimensions of the filter could be significantly reduced.

# 2.1.3 Manufacturing Technologies

The arrival of the 5G era has resulted in the structural growth of data transmission, and it is changing people's daily lives. In order to manage the transmission of massive data, system it requires not only new complex modulation methods, but also a wide radio frequency spectrum to support high-speed broadband communications. Therefore, frequency bands in the mm-wave regions have been widely used to support the required

high-speed transmission. Traditionally, most mm-wave filters are manufactured using PCB technology such like the LTCC and SIW technology. This is despite the traditional manufactured millimeter waves bandpass filters perform well, low insertion loss and high frequency selectivity. The miniaturization of mm-wave filters is also limited due to the influence of the narrowest metal line in the above processes. With the development of semiconductor lithography technology, manufacturing accuracy has reached the micron and nanometer levels that provide the basis for further miniaturization of mm-wave bandpass filters. In contrast, in order to get the system to consume less power, more and more devices are integrated on the chip to form a system on chip (SoC). Therefore, the advantages of on-chip mm-wave filters have become increasingly prominent.

Among the many chip processing technologies, it is particularly important to select the appropriate manufacturing technology. Especially, for large-scale commercial chips, tape-out prices have a particularly large impact on market competitiveness. Therefore, the processing technology needs to be chosen to minimize the cost of tape out while meeting the design indicators. The following figure shows the tape-out prices of various processing technologies and foundry factories. On the premise of satisfying designed results, one of the studies in this thesis adopts the most economical 0.13-µm SiGe processing technology to fabricate the filter.

As compared, some main used fabrication processes are listed in this section:

• Gallium Arsenide (GaAs) and Gallium Nitride (GaN) technologies. As processes for designing millimeter wave circuits, they have also become hot topics of current research. Dr. Yang and colleagues used edge cross-finger coupling to design two low-loss and high-selectivity filters [43]. The lumped parameter circuit helped to analyze the transmission zero point and resonance characteristics of the filters and received good frequency selection characteristics. In [105], two dual-mode resonators are used for coupling. A

second-order filter is constructed with slot electrical coupling for feeding which achieves low insertion loss and good design selection. However, the fabricating cost of GaAs and GaN technology is far higher than that of CMOS technology. Consequently, they are not suitable for integration with baseband processers at present, which restricts their use in millimeter wave circuits.

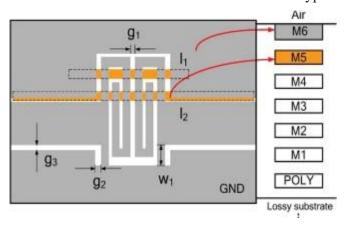

• Silicon germanium (SiGe) is widely used in the design of millimeter wave circuits due to its high compatibility and low processing cost. The highest cut-off frequency of the SiGe technology used in this thesis is 200 GHz [89]. However, this technology also has certain limitations, for example, it is difficult to transfer the design method on the PCB board to the IC design. The high loss of the dielectric substrate and the low quality factor of the device, the fixed thickness of the dielectric layer and the strict design specifications are different from PCB to integrated circuits. These technical limitations still cannot hinder the development of RFIC.

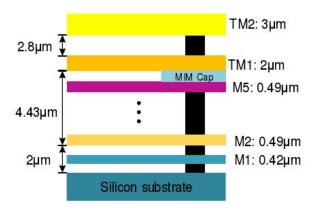

Figure 2.1. Metal stack-up in 0.13-µm SiGe (Bi)CMOS

## 2.2 Review of Related Passive Researches

As far as on-chip filter is concerned, some kinds of classical EM structures have been published in the literature. In this section different EM structures will be described, and challenges for further improving the performance of designed on-chip filter will be summarized.

# 2.2.1 Interdigital Structure

As the modern communication systems now have some new modulation versions like the Orthogonal Frequency Division Multiplexing(OFDM), RF filters are made to be qualified to those high speed and frequency applications. Some know-how structures for new filtering passive devices will be reviewed in this section.

## CMOS 5-order symmetric Interdigital BPF

Miniaturization is always the core issue for integrating the passive components on a CMOS structure. Bo Yang and team devised a fabricated structure working at a center frequency of 55GHz as a bandpass filter [30]. A coupling part is added between the two resonators in the filter. Then the designed interdigital filter is working well as a compact size instead. The figure below is the schematic of the design principle.

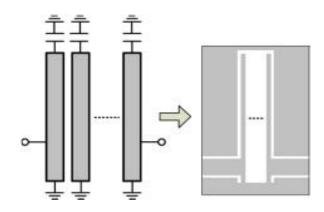

Figure 2.3. Schematic of the coupling structure [30].

Then, with this methodology, authors designed and fabricated a bandpass filter as this structure with CMOS substrate for the RF front end module (FEM). As tested, the operating frequency is located at 55.3GHz deliberately. However, the bandwidth of the final solid result is only 3.25% which is not quite suitable for those applications working at mm-wave frequency ranges.

Figure 2.4. Die photo of the designed filter following the structure in Figure 2.2.[30]

#### U-Shaped Interdigital Resonator

In the article presented by Islam Mansour et al. [31], a U-shaped resonator is designed with a U-shaped inductor and finger capacitors to build a Ku-band voltage controlled oscillator (VCO). For this design to be feasible, the fabricated integrated circuit has a compact size of 0.0015 mm<sup>2</sup> on its resonator part. Q factor reaches 2.06 due to this structure exhibiting low resistance. The frequency range of this notch filter is from 68 GHz to 88 GHz for the VCO operation. Respectively, this U-shaped filter is suitable for some specific structures with small size and broad band requirements. Also, this passive device in the article employs the 180 nm CMOS technology along

with its whole structure. It means that this filter could be integrated into some other silicon based mm-wave structures.

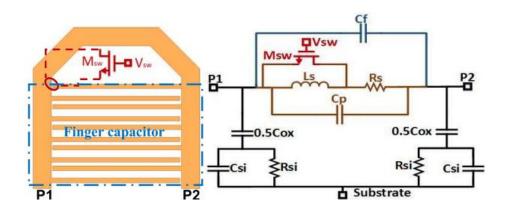

Figure 2.5. U-shaped interdigital resonator and its equivalent circuit model in [31].

## • Integrated BPF using Interdigital Capacitors

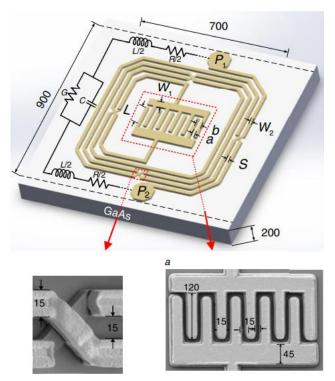

Z. Chuluunbaatar and colleagues brought out a novel structure using interdigital capacitors operating on the sub-6 frequency range. Since its purpose was to be utilized in the WiMax systems, this BPF is fabricated with the GaAs technology. Thus, its center frequency is 2.31 GHz and the total chip size is up to 900  $\mu$ m  $\times$  700  $\mu$ m [32]. To meet the requirements of filtering implementation, an integrated passive device is widely used to form a BPF. The structure depicted in the following figure is made of a spiral-shaped inductor with an interdigital capacitor inside. Compared to others, this design has good features of size, insertion loss and fabrication cost as its metal layers. However, the GaAs technology limits its operational frequency range to the mm-wave frequency bands.

Figure 2.6. Layout of the BPF with its equivalent circuit and die photo with physical details in [32].

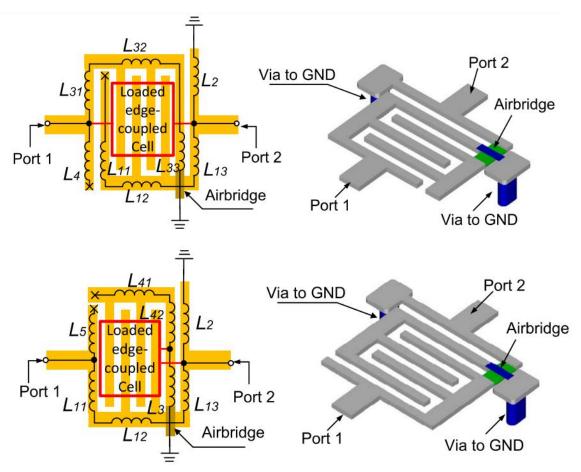

Dr. Yang Yang and his team also implemented the interdigital structure with the GaAs-based technology to design a bandpass filter in [43]. They built a unique LC circuit with edge-coupled cells (ECCs). Compared with the silicon-based designs, GaAs on-chip passive integrated circuits have a big advantage concerning the miniaturization task. Furthermore, this proposed filter is operating at the center frequency of 23.5 GHz with a significant 3-dB bandwidth of 22.2%. Using this technique, the loaded ECCS can be converted into a resonator and shrink the chip size as much as possible. The size of the fabrication reached 0.18 mm² with a commercial technology, 0.1- µ m Gallium Arsenide.

Figure 2.7. Different resonator structures with loaded edge-coupled cells [43].

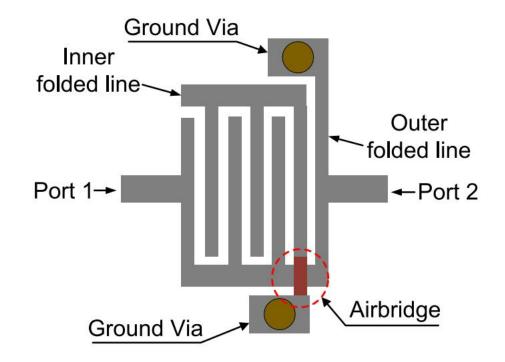

Figure 2.8. Implementation of the interdigital resonator [43].

Figure 2.9. Die microphotograph [43].

## 2.2.2 Stepped Impedance Technique

The so-called stepped impedance technique is another well-established one in the literature. In this sub-section, an overview of integrated filters design using this technique will be given.

## Meandering Hairpin Resonator

In 2008, Bo Yang and his colleagues working at University of Melbourne published an article about the meandering hairpin resonator [33]. This device is operating at the center frequency of 60GHz with a 8.5GHz bandwidth. Figure 2.9 depicts a 4th-order Stepped Impedance Resonator(SIR) bandpass filter which is formed by two miniaturized meandering hairpin (MH) resonators and two stepped impedance resonators. It was fabricated on IBM 0.13 µ m CMOS technology, and miniaturized to a size as small as 0.346 m<sup>2</sup>.

Recalling the theoretical parameter described in [106], the n<sup>th</sup>-order BPF could be switched up and down with the known Q-value of the input and output loaded resonators. In the design done by [33] the fabricated circuits are shown below in Figure 2.10.

Figure 2.10. The design of the presented 4<sup>th</sup>-order cross-coupled SIR-MH filter [33].

Figure 2.11. Die photograph of the designed Bandpass Filter in [33].

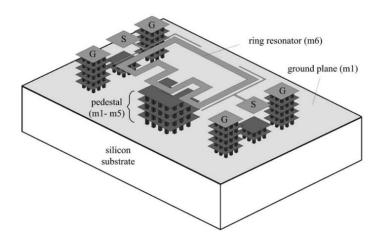

## • Stepped Impedance Technique with Grounded Pedestal

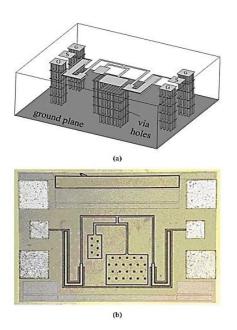

Shuen-Chien Chang and his team brought another stepped impedance structure to form a CMOS based millimeter-wave band pass filter. To be integrated in the transceiver system, the chip size should be miniaturized as small as possible. With this design, the filter reached the size of  $0.37 \times 0.2 \, \text{mm}^2$ . It brought a new solution to the devices operating between 40 and 78 GHz.

Figure 2.12. The designed bandpass filter [34].

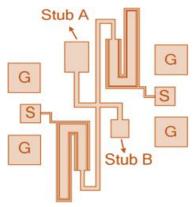

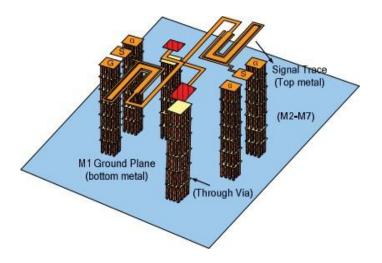

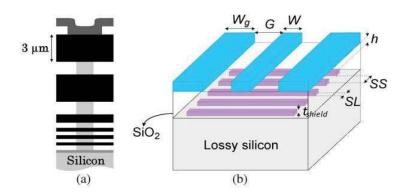

A similar design technique is used in the paper presented in [35], and it is illustrated in Figure 2. 12 with a different design structure. A stepped-impedance cross-resonator using M2 to M7 forms the ground. The two open stubs with the grounded pedestal are designed to further improve the TZs found below and above the passband. The TZ will vary depending on the number of metal layers stacked on top of each other to form the pedestal. The height of the metal stacked up will have an effect on the impedance of the system. Therefore, the TZ can be effectively controlled by the level of the pedestal. The design in [35] resonates at 77 GHz with insertion loss less than 3 dB and return loss of greater than 40 dB. The 3-D view of the layout is illustrated in Figure 2.13.

Figure 2.13. The 2-D view of the designed BPF using stepped-impedance resonator in [35].

Figure 2.14. The 3-D view of the designed BPF shown in Figure 2.12 [35].

#### Stepped-Impedance-Based Resonator

Another design example presented in [34] uses an open resonator. One shortcoming of this design structure is that the TZ does not exist. In order to address this issue, an open stub is shunted at the center position of two TZs. This structure creates a virtual short at the center of the resonator at the fundamental odd-mode frequency, thus providing TZs at the desired frequency. Figure 2.14 illustrates the design presented in [34]. As can be seen, it is implemented using an open-ended stub. Based on the simulation results the height and width ratio is proportional to the resonance frequency. Thus, a shorter resonator length is favorable in order to achieve the desired target frequency.

Figure 2.14. The designed BPF, (a) the 3-D view of the BPF, (b) die photo of the design.

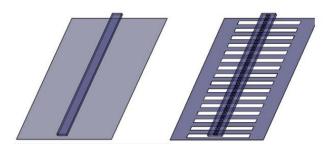

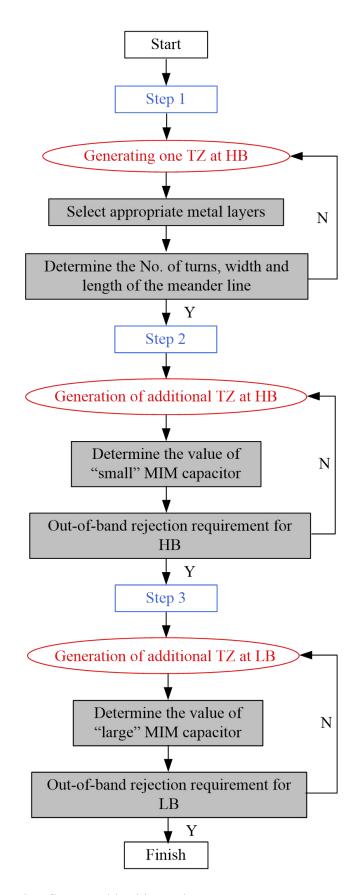

#### 2.2.3 Slow-Wave Structures