$C02029: Doctor\ of\ Philosophy$

CRICOS Code: 2018

12345 PhD Thesis: Electrical Engineering

Oct 2022

# Transformer-less Grid-Tied AC Module Systems Suitable for Single-Phase Renewable Energy-Based Applications

Reza Barzegarkhoo

School of Electrical and Data Engineering Faculty of Engineering and IT. & IT University of Technology Sydney NSW - 2007, Australia

## Transformer-less Grid-Tied AC Module Systems Suitable for Single-Phase Renewable Energy-Based Applications

A thesis submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

by

### Reza Barzegarkhoo

to

School of Electrical and Data Engineering

Faculty of Engineering and Information Technology

University of Technology Sydney

NSW - 2007, Australia

March 2023

#### **ABSTRACT**

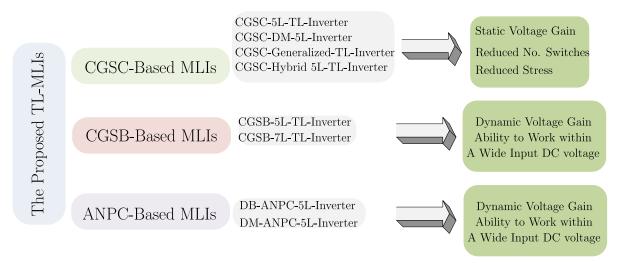

rid-tied converters/inverters with a transformerless (TL) circuit configuration are an efficient power electronics interface between the power grid and renewable energy resources, e.g., photovoltaic (PV) arrays, batteries, and fuel cells. Such a tremendous inclination to use the TL converters originates from their appropriate power density and higher rate of overall efficiency with a lower overall manufacturing cost in comparison to their transformer-based counterparts. However, detaching the galvanic isolated transformer from the converter and the grid and using the commercially available two or three-level voltage source inverters lead the following challenges/concerns: 1) Variable common mode voltage (CMV) and in turn the ground leakage current problem, 2) the need for another power processing stage to meet the minimum requirement of the grid voltage amplitude while utilizing a relatively low value of the dc input voltage, and 3) power quality enhancement issue. The aim of this thesis is to investigate the above-mentioned constrains/challenges among various developed versions of the existing TL inverters, and accordingly propose several new circuit configurations to address such issues. All the proposed converters/inverters are able to generate a multilevel staircase output voltage waveform using a single dc source leading to improve the injected power quality and reduce the need for large bulky interfaced filters. To alleviate the effect of high frequency CMV in grid-connected PV systems and to nullify the concern of leakage current, the design configuration of all the proposed topologies is either based on a common-ground circuit architecture or a mid point-clamping technique. Through the incorporation of switched-capacitor and/or switched-boost technique, all the proposed structures possess either a static or dynamic voltage conversion gain, which make them an attractive choice when the input dc source is variable and low. Extending the operating range of the grid-connected TL converters for a wide range of the input dc voltage, reduction on voltage/current stress profile of the switches, circuit extension capability to generate larger number of output voltage levels, and reduced number of required power electronics elements, i.e., switches, gate drivers, inductors, and capacitors are some other important characteristics of the proposed topologies. Since the major goal of each of the proposed TL-based grid-tied inverters/converters is to inject a tightly controlled current to the grid, the performance of all the proposed structures is governed within a closed-loop control platform. Comparative study and the design guidance of the proposed converters are developed. And finally, several simulation and experimental results are presented to prove the feasibility and correct operation of each of the proposed converters.

### **AUTHOR'S DECLARATION**

Reza Barzegarkhoo declare that this thesis, submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy, in the Electrical and Data Engineering, Engineering and IT at the University of Technology Sydney, Australia, is wholly my own work unless otherwise referenced or acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis. This document has not been submitted for qualifications at any other academic institution. This research is supported by the Australian Government Research Training Program.

Production Note:

SIGNATURE: Signature removed prior to publication.

[Reza Barzegarkhoo]

DATE: 20th March, 2023

PLACE: Sydney, Australia

#### **DEDICATION**

#### To my family, friends, and my beloved home country, Iran...

Hereby, I would like to dedicate this dissertation to my family first. During such a tough period and in specific when the COVID-19 pandemic emerged, I never had a chance to visit my family in Iran. However, I could feel their endless emotions, unconditional love, and continuous encouragement when I was struggling with each piece of this thesis content. I also would like to present this dissertation to my beloved sister and the little member of our family, Peransa, my sister daughter, who was born during the latest months of my PhD.

There is no doubt that without the technical support and important advice of my closed friends and the collaborators from different corner of the word, this thesis could not have such a nice outcome. With their help and support, more than 20 articles in different well-known journals and conference proceeding were published from this thesis content, which can perfectly show the importance of collaboration with developed/fresh ideas. I would like to particularly express my gratitude to my friend, Mr. Majid Farhangi who gave me his tremendous support in the UTS Power Electronics Lab.

Last but not least, I would like to dedicate all the efforts done to compile this research during my PhD to all the Iranian people living in my beloved home country. As a persian guy, I tried to do my best during my stay abroad to show our nice culture, friendly behavior, and research/team work capability to the rest of the world. I would like to dedicate this work to all the talented young researchers who are living in Iran and have this aspiration to move towards the PhD to flourish their research potential.

### **ACKNOWLEDGMENTS**

would express my deepest gratitude to my principal supervisor Dr. Yam Siwakoti for his guidance and encouragement during my study. I also would like to thank my co-supervisor, Dr. Ricardo P. Aguilera for his thorough help and advice throughout this research.

In addition, I would like to express my gratitude to the University of Technology Sydney for the provided financial support.

#### LIST OF PUBLICATIONS

#### **JOURNAL ARTICLES**

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, F. Blaabjerg, and Y. P. Siwakoti, "A Novel Active Neutral Point-Clamped Five-Level Inverter With Single-Stage Integrated Dynamic Voltage Boosting Feature," in IEEE Transactions on Power Electronics, doi: 10.1109/TPEL.2023.3257959.

- R. Barzegarkhoo, M. Forouzesh, S. S. Lee, F. Blaabjerg and Y. P. Siwakoti, "Switched-Capacitor Multilevel Inverters: A Comprehensive Review," in IEEE Transactions on Power Electronics, vol. 37, no. 9, pp. 11209-11243, Sept. 2022, doi: 10.1109/TPEL.2022.3164508.

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, Y. P. Siwakoti and J. Pou, "Nine-Level Nine-Switch Common-Ground Switched-Capacitor Inverter Suitable for High-Frequency AC-Microgrid Applications," in IEEE Transactions on Power Electronics, vol. 37, no. 5, pp. 6132-6143, May 2022, doi: 10.1109/T-PEL.2021.3131847.

- R. Barzegarkhoo, S. A. Khan, Y. P. Siwakoti, R. P. Aguilera, S. S. Lee and M. N. H. Khan, "Implementation and Analysis of a Novel Switched-Boost Common-Ground Five-Level Inverter Modulated With Model Predictive Control Strategy," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 10, no. 1, pp. 731-744, Feb. 2022,

- R. Barzegarkhoo, S. S. Lee, S. A. Khan, Y. P. Siwakoti and D. D. -C. Lu, "A Novel Generalized Common-Ground Switched-Capacitor Multilevel Inverter Suitable for Transformerless Grid-Connected Applications," in IEEE Transactions on Power Electronics, vol. 36, no. 9, pp. 10293-10306, Sept. 2021.

- R. Barzegarkhoo, Y. P. Siwakoti, R. P. Aguilera, M. N. H. Khan, S. S. Lee and F. Blaabjerg, "A Novel Dual-Mode Switched-Capacitor Five-Level Inverter With

- Common-Ground Transformerless Concept," in IEEE Transactions on Power Electronics, vol. 36, no. 12, pp. 13740-13753, Dec. 2021.

- R. Barzegarkhoo, S. S. Lee, Y. P. Siwakoti, S. A. Khan and F. Blaabjerg, "Design, Control, and Analysis of a Novel Grid-Interfaced Switched-Boost Dual T-Type Five-Level Inverter With Common-Ground Concept," in IEEE Transactions on Industrial Electronics, vol. 68, no. 9, pp. 8193-8206, Sept. 2021.

- R. Barzegarkhoo, Y. P. Siwakoti and F. Blaabjerg, "A New Switched-Capacitor Five-Level Inverter Suitable for Transformerless Grid-Connected Applications," in IEEE Transactions on Power Electronics, vol. 35, no. 8, pp. 8140-8153, Aug. 2020.

- R. Barzegarkhoo, Y. P. Siwakoti, N. Vosoughi and F. Blaabjerg, "Six-Switch Step-Up Common-Grounded Five-Level Inverter With Switched-Capacitor Cell for Transformerless Grid-Tied PV Applications," in IEEE Transactions on Industrial Electronics, vol. 68, no. 2, pp. 1374-1387, Feb. 2021.

- R. Barzegarkhoo, H. Mojallali, S. H. Shahalami, and Yam. P. Siwakoti "A Novel Common-Ground Switched-Capacitor Five-Level Inverter with Adaptive Hysteresis Current Control for Grid-Connected Applications," IET Power Electron, vol. 14, no. 12, pp. 2084-2098, Sep. 2021.

- R. Barzegarkhoo, M. Farhangi, R. P. Aguilera, S. S. Lee, F. Blaabjerg, and Y. P. Siwakoti, "Common-Ground Grid-Connected Five-Level Transfomerless Inverter with Integrated Dynamic Voltage Boosting Feature," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 10, no. 6, pp. 6661-6672, Dec. 2022.

- S. S. Lee, Y. P. Siwakoti, **R. Barzegarkhoo**, and K. -B. Lee, "Switched-Capacitor-Based Five-Level T-Type Inverter (SC-5TI) With Soft-Charging and Enhanced DC-Link Voltage Utilization," in IEEE Transactions on Power Electronics, vol. 36, no. 12, pp. 13958-13967, Dec. 2021, doi: 10.1109/TPEL.2021.3088443.

- S. S. Lee, Y. P. Siwakoti, **R. Barzegarkhoo**, and F. Blaabjerg, "A Novel Common-Ground-Type Nine-Level Dynamic Boost Inverter," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 10, no. 4, pp. 4435-4442, Aug. 2022, doi: 10.1109/JESTPE.2021.3104939.

- M. Farhangi, R. Barzegarkhoo R. P. Aguilera, S. S. Lee, D. Lu, and Y. P. Si-wakoti, "A Single-Source Single-Stage Switched-Boost Multilevel Inverter: Operation, Topological Extension, and Experimental validation" in IEEE Transactions

- on Power Electronics, vol. 37, no. 9, pp. 11258-11271, Sept. 2022, doi: 10.1109/T-PEL.2022.3163762.

- S. A. Khan et al., "Topology, Modeling and Control Scheme for a new Seven-Level Inverter With Reduced DC-Link Voltage," in IEEE Transactions on Energy Conversion, vol. 36, no. 4, pp. 2734-2746, Dec. 2021.

- S. S. Lee, Y. Yang, Y. P. Siwakoti, and **R. Barzegarkhoo** "Improved Cascaded H-Bridge Multilevel Inverters with Voltage-Boosting Capability" Electronics, vol. 10, no. 22, page.2801, Dec.2021.

- S. S. Lee, Y. P. Siwakoti, **R. Barzegarkhoo** and K. -B. Lee, "Switched-Capacitor-Based Five-Level T-Type Inverter (SC-5TI) With Soft-Charging and Enhanced DC-Link Voltage Utilization," in IEEE Transactions on Power Electronics, vol. 36, no. 12, pp. 13958-13967, Dec. 2021.

- M. N. H. Khan et al., "A Common Grounded Type Dual-Mode Five-Level Transformerless Inverter for Photovoltaic Applications," in IEEE Transactions on Industrial Electronics, vol. 68, no. 10, pp. 9742-9754, Oct. 2021.

#### CONFERENCE PROCEEDING PAPERS

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, Y. P. Siwakoti, and M. Liserre "Active-Neutral-Point-Clamped Five-Level Inverter With Single-Stage Dynamic Voltage Boosting Capability," IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG 2022).

- Y. Syasegov, R. Barzegarkhoo, S. U. Hassan, Y. P. Siwakoti, and L. Li "A 5-level Mid Point-Clamped Heric Inverter," IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG 2022).

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera and Y. P. Siwakoti, "A Novel Seven-Level Switched-Boost Common-Ground Inverter With Single-Stage Dynamic Voltage Boosting Gain," 2022 International Power Electronics Conference (IPEC-Himeji 2022- ECCE Asia), 2022, pp. 873-877, doi: 10.23919/IPEC-Himeji2022-ECCE53331.2022.9807006.

- M. Farhangi, R. Barzegarkhoo, S. S. Lee, D. Lu and Y. Siwakoti, "An Interleaved Switched-Boost Common-Ground Five-Level Inverter," 2022 International Power

Electronics Conference (IPEC-Himeji 2022- ECCE Asia), 2022, pp. 867-872, doi: 10.23919/IPEC-Himeji2022-ECCE53331.2022.9807154.

- S. S. Lee, Y. P. Siwakoti, **R. Barzegarkhoo**, and K. -B. Lee, "A Five-Level Unity-Gain Active Neutral-Point-Clamped Inverter Designed Using Half-Bridges," 2022 International Power Electronics Conference (IPEC-Himeji 2022- ECCE Asia), 2022, pp. 859-866, doi: 10.23919/IPEC-Himeji2022-ECCE53331.2022.9806830.

- R. Barzegarkhoo, M. Farhangi, R. P. Aguilera, Y. P. Siwakoti and S. S. Lee, "Switched-Boost Common-Ground Five-Level (SBCG5L) Grid-Connected Inverter With Single-Stage Dynamic Voltage Boosting Concept," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 1014-1019.

- R. Barzegarkhoo, Y. P. Siwakoti and R. P. Aguilera, "A New Common-Ground Switched-Boost Five-Level Inverter Suitable for both Single and Three-Phase Grid-Tied Applications," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 1179-1183.

- R. Barzegarkhoo, Y. P. Siwakoti and F. Blaabjerg, "Model Predictive Control of a Five-level Active Boost Neutral Point Clamped (5L-ABNPC) Inverter for Transformerless Grid-Connected PV Applications," 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), 2020, pp. 209-213.

- R. Barzegarkhoo, Y. P. Siwakoti, T. Long and F. Blaabjerg, "Five-Level Grid-Tied Inverter Employing Switched-Capacitor Cell with Common-Grounded Feature," 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 3298-3303.

- M. Farhangi, Y. P. Siwakoti, **R. Barzegarkhoo**, S. U. Hasan, D. Lu and D. Rogers, "A Compact Design Using GaN Semiconductor Devices for a Flying Capacitor Five-Level Inverter," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 2475-2479.

- M. Farhangi, Y. P. Siwakoti, **R. Barzegarkhoo**, S. U. Hasan, D. Lu and D. Rogers, "A Compact Design Using GaN Semiconductor Devices for a Flying Capacitor Five-Level Inverter," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021.

• Y. P. Siwakoti, T. Long, **R. Barzegarkhoo**, and F. Blaabjerg, "A Dual Mode 5-Level Inverter with Wide Input Voltage Range," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 3609-3615.

#### AWARDS AND ACHIEVEMENTS

- A recipient of the prestigious Green Talent Award 2021 from the German Federal Ministry of Education and Research (BMBF). "Selected as one of 25 green-talent awardees in 2021 among more than 450 international applicants".

- A recipient of the best paper award selected by the IEEE Industrial Electronics Society (IES) in 2022.

- A recipient of the best paper award selected by the 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG 2022), Kiel, Germany.

- A recipient of the IEEE Industrial Electronics Society Inter Chapter Paper competition with the theme of Smart Connected Community in 2021.

- Winners of the best showcase award among all the PhD candidates in School of Electrical and Data Engineering, University of Technology Sydney (UTS), Australia, Oct 2021, and Nov 2020.

- Winner of the best showcase award among all the PhD candidates in the Faculty of Engineering and IT, University of Technology Sydney (UTS), Australia, Nov 2020.

- A commendation by Faculty of Engineering and IT of UTS for the HDR 2022 team awards.

- Student Travel award to attend in ECCE 2021, Vancouver, Canada and PEDG 2022, Kiel, Germany.

- Distinguished Reviewer of IEEE Transactions on Industrial Electronics in 2020.

- Star Reviewer of IEEE journal of Emerging and Selected Topics in Power Electronics in 2022.

## TABLE OF CONTENTS

| Li | st of | Public | eations                                                          | ix   |

|----|-------|--------|------------------------------------------------------------------|------|

| Li | st of | Figure | es                                                               | xix  |

| Li | st of | Tables | \$<br>\$                                                         | xxix |

| A  | crony | /ms    |                                                                  | XXX  |

| 1  | Intr  | oducti | ion                                                              | 1    |

|    | 1.1   | Recen  | t Advances on Grid-Tied Transformerless Inverters                | . 1  |

|    |       | 1.1.1  | Freewheeling-Based TL-Inverters                                  | . 4  |

|    |       | 1.1.2  | Mid Point-Clamped TL-Based MLIs                                  | . 7  |

|    |       | 1.1.3  | CG-Based TL-MLIs                                                 | . 9  |

|    |       | 1.1.4  | Challenges Over the SC-based MLIs                                | . 13 |

|    | 1.2   | An Ov  | verview of Major Closed-Loop Control Techniques for Single-Phase |      |

|    |       | Grid-7 | Fied TL-Inverters                                                | . 16 |

|    | 1.3   | An Ou  | atlook of the Thesis Contribution                                | . 20 |

| 2  | Con   | nmon-( | Ground Switched-Capacitor-Based MLIs                             | 23   |

|    | 2.1   | CGSC   | -Based 5L Inverters                                              | . 23 |

|    |       | 2.1.1  | First Topology                                                   | . 23 |

|    |       | 2.1.2  | Second Topology                                                  | . 25 |

|    | 2.2   | CGSC   | -Based Generalized TL-MLIs                                       | . 27 |

|    | 2.3   | DM-C   | GSC-Based 5L Inverter                                            | . 32 |

|    | 2.4   | CGSC   | -Based 9L Inverter                                               | . 35 |

|    |       | 2.4.1  | Modulation and Control Scheme                                    | . 40 |

|    |       | 2.4.2  | Design Guidelines                                                | . 45 |

|    |       | 2.4.3  | Comparative Study                                                | . 47 |

|    |       | 2.4.4  | Open-Loop Experimental Results                                   | . 49 |

| Bi | ibliog | graphy  |                                                               | 145 |

|----|--------|---------|---------------------------------------------------------------|-----|

| 5  | Con    | clusio  | n                                                             | 139 |

|    |        | 4.2.7   | Single- and Three-Phase Experimental Results                  | 135 |

|    |        | 4.2.6   | Single-Phase Simulation Results                               | 132 |

|    |        | 4.2.5   | Comparative Study                                             | 131 |

|    |        | 4.2.4   | Design Guidelines                                             | 129 |

|    |        | 4.2.3   | Proposed DM-ANPC-5L-Type-III converter                        | 129 |

|    |        | 4.2.2   | Proposed DM-ANPC-5L-Type-II converter                         | 128 |

|    |        | 4.2.1   | Proposed DM-ANPC-5L-Type-I Converter                          |     |

|    | 4.2    |         | nily of DM-ANPC-5L-TL Inverters                               |     |

|    |        | 4.1.4   | Experimental Results                                          |     |

|    |        | 4.1.3   | Comparative Study                                             |     |

|    |        | 4.1.2   | Passive Elements Design                                       |     |

|    |        | 4.1.1   | Modulation and Control Strategy                               |     |

|    | 1,1    | -       | nic Voltage Gain                                              | 102 |

| •  | 4.1    |         | sed Dual-Boost ANPC-5L linverter with Integrated Single-Stage | 101 |

| 4  | Mid    | l Point | -Clamped-Based MLIs                                           | 101 |

|    | 3.3    | Propos  | sed CGSB7L-TL Inverter with Single-Stage Dynamic Gain         | 96  |

|    |        | 3.2.5   | Verification Results                                          | 89  |

|    |        | 3.2.4   | Comparative Study                                             | 88  |

|    |        | 3.2.3   | Design Guidelines                                             | 86  |

|    |        |         | verter: Second Topology                                       | 85  |

|    |        | 3.2.2   | Modulation and Control Strategy of the Proposed CGSB-5L in-   |     |

|    |        | 3.2.1   | Proposed QSBCG5L-TL Inverter                                  |     |

|    | 3.2    |         | -Based 5L Inverter: Second topology                           |     |

|    | 3.1    |         | -Based 5L Inverter: First topology                            |     |

| 3  | Con    | nmon-(  | Ground Switched-Boost-Based MLIs                              | 73  |

|    |        | 2.5.3   | Verification Results                                          | 68  |

|    |        | 2.5.2   | Comparative Study                                             | 66  |

|    |        | 2.5.1   | CCS-MPC Strategy Applied to the Proposed CGSB5L-TL inverter   | 61  |

|    | 2.5    | CG-Ba   | ased 5L Inverter: A hybrid SC and SB topology                 | 54  |

|    |        | 2.4.6   | PLECS Simulation Results                                      | 53  |

|    |        | 2.4.5   | Closed-Loop Experimental Results                              | 51  |

## LIST OF FIGURES

| Figu | URE Pa                                                                                                                                                                                                                                                                                                    | ıge |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

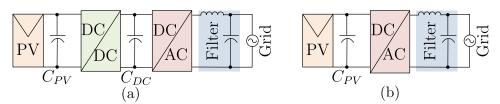

| 1.1  | The overall configuration of power conversion system based on (a) two-stage platform, (b) single-stage platform [2]                                                                                                                                                                                       | 3   |

| 1.2  | Examples of transformer-included inverter solutions based on (a) Line-frequency (LF) transformer, (b) embedded High-frequency transformer [2]. $\dots$ .                                                                                                                                                  | 3   |

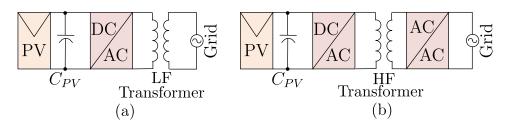

| 1.3  | Categorization of the TL-based grid-tied inverters.                                                                                                                                                                                                                                                       | 4   |

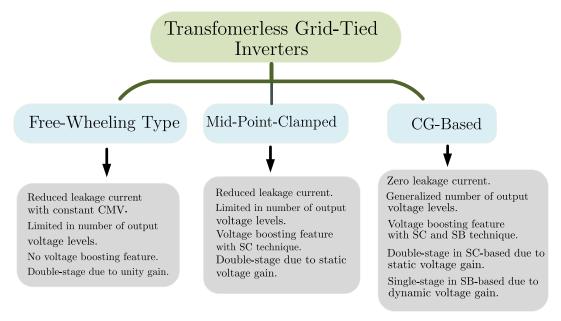

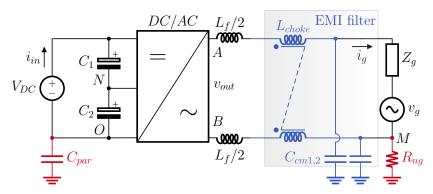

| 1.4  | Common-mode model for single-phase grid-connected inverter: (a) Full model, (b) simplified model [10]                                                                                                                                                                                                     | 4   |

| 1.5  | A simplified structure of the grid-connected TL inverter with CM-filter                                                                                                                                                                                                                                   | 5   |

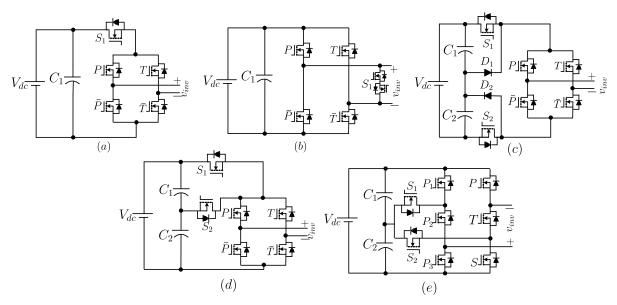

| 1.6  | Full-bridge based topologies for TL grid-tied inverters (a) H5 [12] (b) HERIC [13] (c) H6 with DC bypass [14] (d) OH5 [17], and (e) PN-NPC [18]                                                                                                                                                           | 6   |

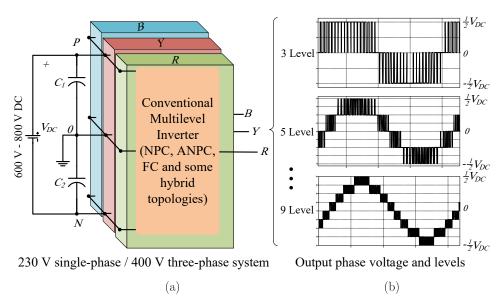

| 1.7  | Circuit illustration of conventional TL-inverters with mid point-clamped technique [25]                                                                                                                                                                                                                   | 7   |

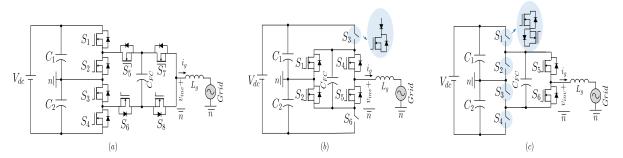

| 1.8  | ABNPC-based TL inverters (a) 5L-ABNPC [25], (b) 7L-ABNPC [29], (c) 9L-ABNPC [29], (d) 4L-ABNPC [30], and (e) 5L-ABNPC [32]                                                                                                                                                                                | 9   |

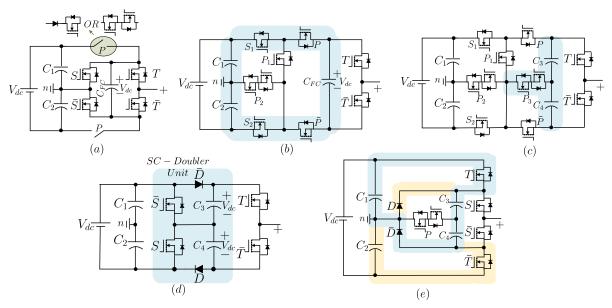

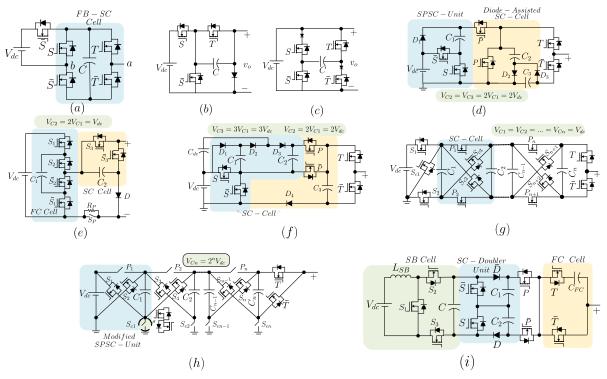

| 1.9  | Different CGSC-Based TL MLIs presented in (a) [33], (b) and (c) [35], (d) [36], (e) [39], (f) [40], (g) [41], (h) [42], and (i) [43]                                                                                                                                                                      | 11  |

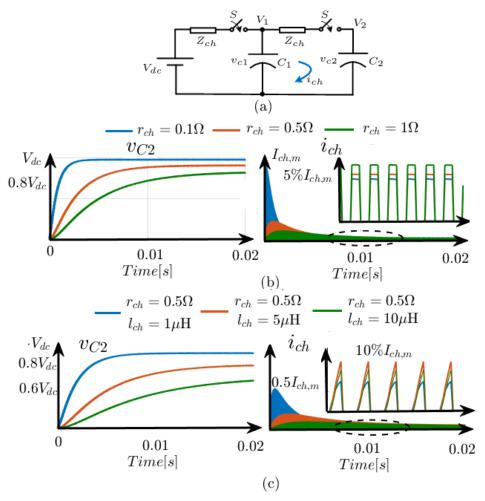

| 1.10 | (a) A typical capacitive charging path circuit for SC-based converters, (b) the voltage of the capacitor and the charging current of the loop for a pure SC-based converter, and (c) the voltage of the capacitor and the charging current of the loop for the SC-based converter with QSC operation [28] | 14  |

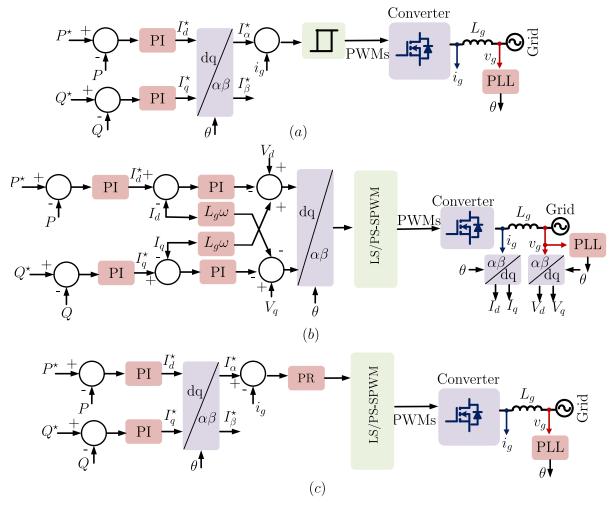

| 1.11 | Simplified block-diagram of (a) HCC, (b) VOC and (c) PR-based control of single-phase grid-tied converters [58]                                                                                                                                                                                           | 17  |

| 1.12 | Overall Outlook of the Thesis Contribution                                                                                                                                                                                                                                                                | 20  |

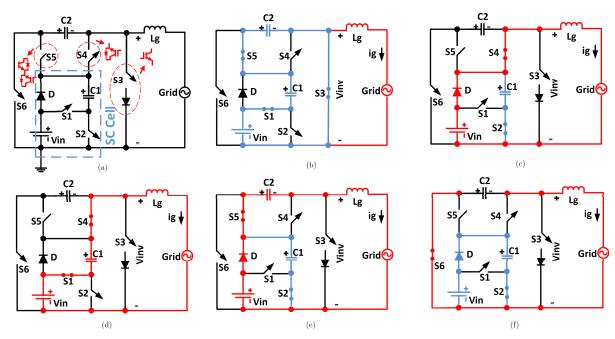

| 2.1 | The proposed five-level SC-based TL-inverter (a) the main circuit configuration (b) the current flowing path of the zero level (c) the current flowing path of the first positive output voltage level (d) the current flowing path of the top positive output voltage level (e) the current flowing path of the first negative output voltage level (f) the current flowing path of the top negative output voltage level [70]                                                                                                                                                                               | 24 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | The current flowing paths of the proposed inverter at (a) the zero-level of the output voltage in the positive half-cycle (b) the first positive level of the output voltage (c) the top positive level of the output voltage (d) the zero-level of the output voltage in the negative half-cycle of (e) the first negative level of the output voltage, and (f) the top negative level of the output voltage [71, 72]                                                                                                                                                                                        | 26 |

| 2.3 | The proposed 5L-CGSC-TL inverter (Generalized Topology) (a) the main circuit schematic and the current flowing path at (b) the zero-level, (c) the first positive-level, (d) the top positive level, (e) the first negative-level, (f) the top negative-level of the output voltage [73]                                                                                                                                                                                                                                                                                                                      | 28 |

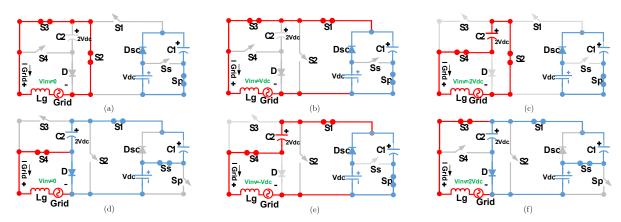

| 2.4 | (a) The proposed CGSC7L-TL inverter (b) the proposed generalized CGSC-TL inverter [73]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 |

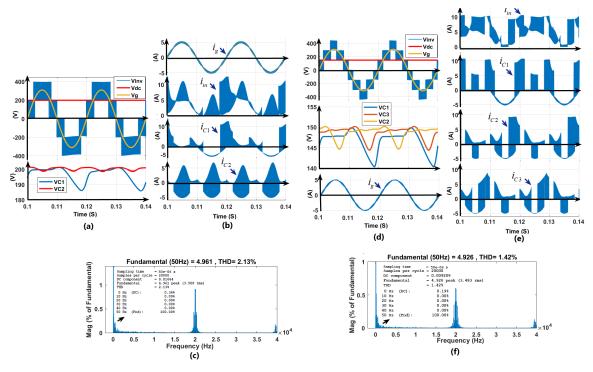

| 2.5 | Simulation results showing: (a) 5L-inverter output with the grid and dc source voltages alongside the capacitors voltages (b) the injected grid-current with the input dc source and the capacitors currents of the proposed 5L-CGSC-TL inverter (c) the injected grid current spectrum for the proposed 5L-CGSC-TL inverter (d) 7L-inverter output with the grid and dc source voltages alongside the capacitors voltages, (e) the input dc source current and the capacitors currents of the proposed 7L-CGSC-TL inverter, (f) the injected grid current spectrum for the proposed 7L-CGSC-TL inverter [73] | 32 |

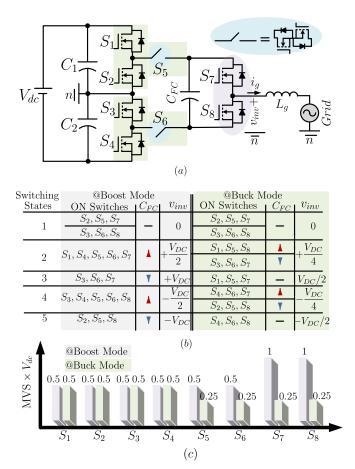

| 2.6 | The proposed DMSC5L-TL inverter topology [74]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 |

| 2.7 | Different current flowing paths of the proposed DMSC5L-TL grid-connected inverter in boost mode operation (a) at the zero level of the output voltage in the positive half cycle (b) at the first positive level of the output voltage (c) at the top positive level of the output voltage (d) at the zero level of the output voltage in negative half cycle (e) at the first negative level of the output                                                                                                                                                                                                   |    |

|     | voltage (f) at the top negative level of the output voltage, [74]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34 |

| 2.8  | Different current flowing paths of the proposed DMSC5L-TL grid-connected                                                                                         |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | inverter in buck mode operation (a) at the zero level of the output voltage                                                                                      |    |

|      | in the positive half cycle (b) at the first positive level of the output voltage                                                                                 |    |

|      | (c) at the top positive level of the output voltage (d) at the zero level of the                                                                                 |    |

|      | output voltage in negative half cycle (e) at the first negative level of the output                                                                              |    |

|      | voltage (f) at the top negative level of the output voltage [74]                                                                                                 | 34 |

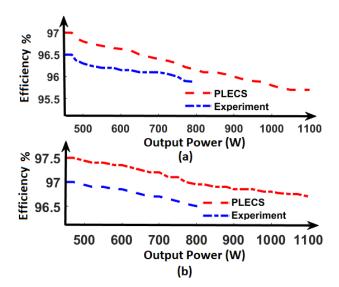

| 2.9  | Efficiency versus output active power curve of the proposed DMSC5L-TL                                                                                            |    |

|      | inverter (a) for the boost mode of operation (b) for the buck mode of operation                                                                                  |    |

|      | [74]                                                                                                                                                             | 35 |

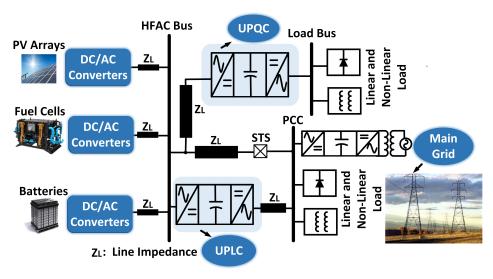

| 2.10 | Typical configuration of a power electronics-based HFac microgrid [75]                                                                                           | 36 |

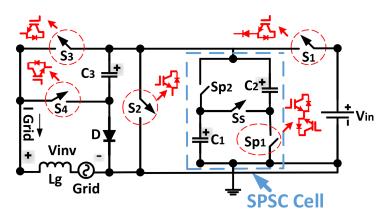

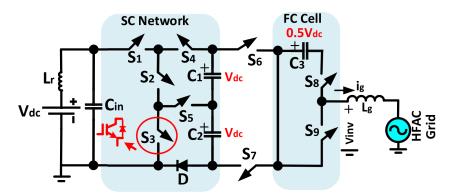

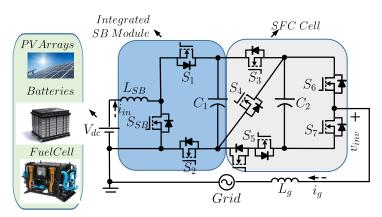

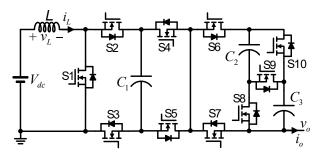

| 2.11 | Proposed 9L9S-CGSC-TL inverter [75]                                                                                                                              | 37 |

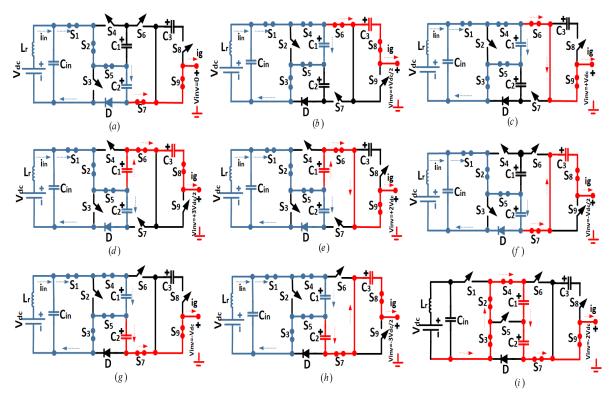

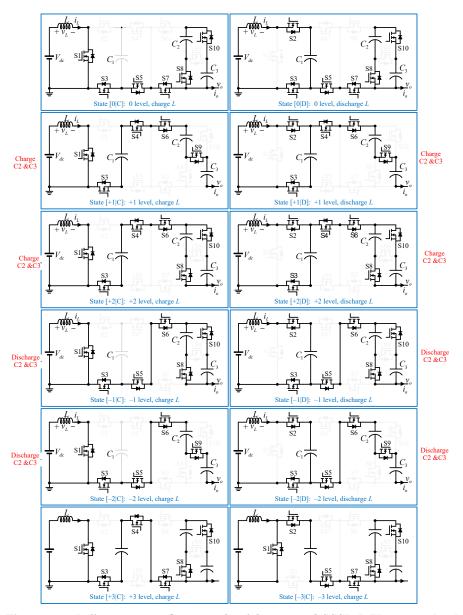

| 2.12 | Different current flowing paths of the proposed 9L9S-CGSC-TL inverter. (a)                                                                                       |    |

|      | Zero-level of the output voltage in both half-cycle, (b) $v_{inv} = \frac{V_{dc}}{2}$ , (c) $v_{inv} = V_{dc}$ ,                                                 |    |

|      | (d) $v_{inv} = \frac{3V_{dc}}{2}$ , (e) $v_{inv} = 2V_{dc}$ , (f) $v_{inv} = \frac{-V_{dc}}{2}$ , (g) $v_{inv} = -V_{dc}$ , (h) $v_{inv} = \frac{-3V_{dc}}{2}$ , |    |

|      | and (i) $v_{inv} = -2V_{dc}$ [75]                                                                                                                                | 38 |

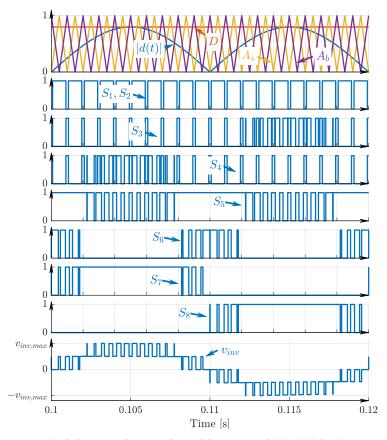

| 2.13 | (a) Closed-loop control configuration, and (b) modulated waveforms and PWM                                                                                       |    |

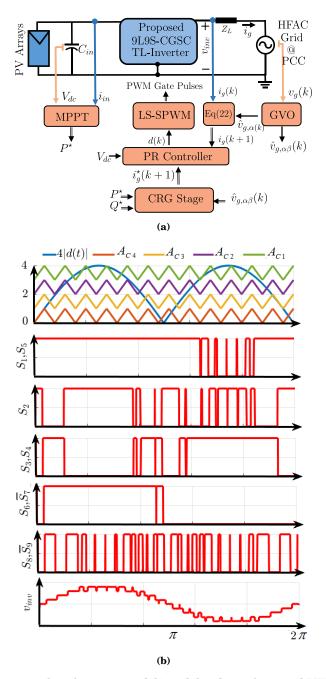

|      | gate switching pulses of the proposed 9L9S-CGSC-TL inverter [75]                                                                                                 | 41 |

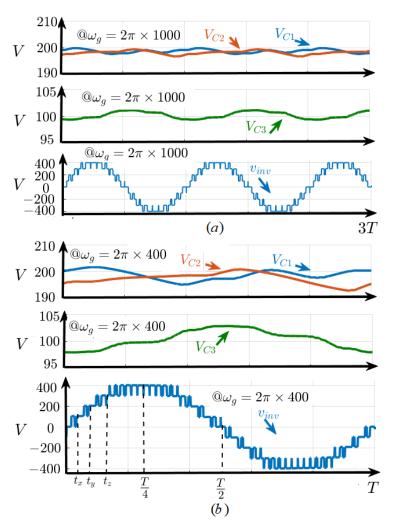

| 2.14 | Voltage ripple across the capacitors with the 9L output voltage of the inverter                                                                                  |    |

|      | at (a) 1-kHz, and (b) 400-Hz fundamental frequency and 20-kHz switching                                                                                          |    |

|      | frequency [75]                                                                                                                                                   | 46 |

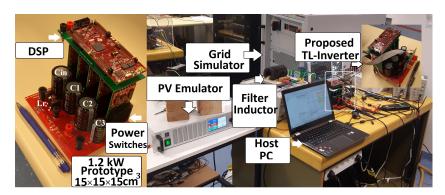

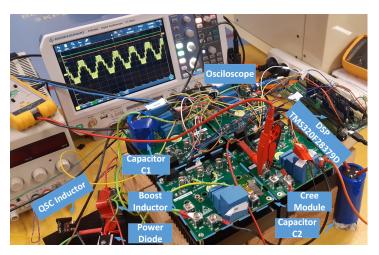

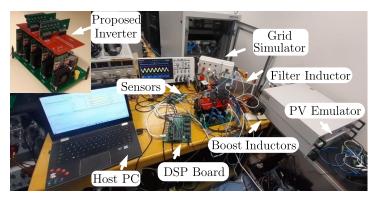

| 2.15 | Picture of the 1.2-kW prototype with the measurement setup [75]                                                                                                  | 49 |

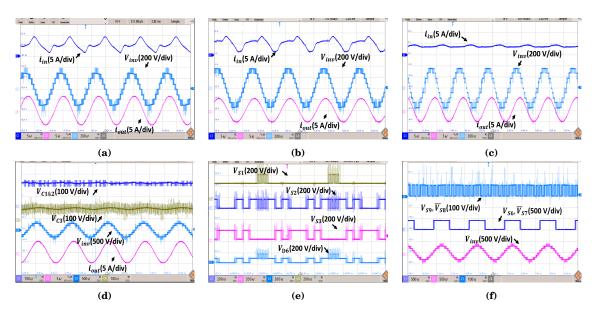

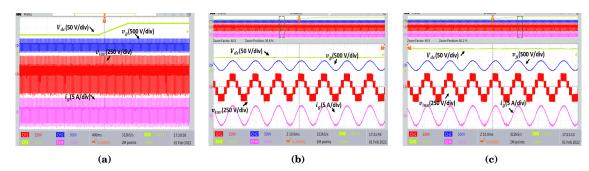

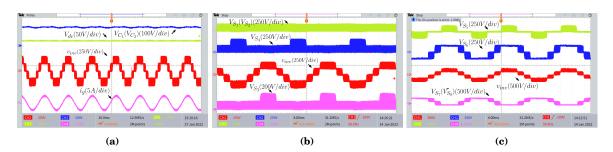

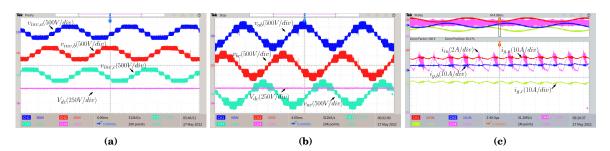

| 2.16 | Experimental waveforms of the proposed 9L9S-CGSC-TL inverter in open-                                                                                            |    |

|      | loop condition. (a) The peak value of the modulation index equals to 0.85 and                                                                                    |    |

|      | $V_{dc}$ = 200 V for 400-Hz load; (b) the peak value of the modulation index equals                                                                              |    |

|      | to 1 and $V_{dc}$ = 180 V for 400-Hz load; (c) the peak value of the modulation                                                                                  |    |

|      | index equals to 1 and $V_{dc}$ = 190 V for 1-kHz load; (d) the voltages across the                                                                               |    |

|      | capacitors; (e) and (f) MVSs across the switches [75]                                                                                                            | 50 |

| 2.17 | Experimental waveforms of the proposed inverter in the closed-loop grid-tied                                                                                     |    |

|      | condition. (a) With zero current injection; (b) 1.2-kW full power injection; (c)                                                                                 |    |

|      | dynamic condition from 1.2-kW injected power to zero power; (d) dynamic                                                                                          |    |

|      | condition from zero injected power to 1.2-kW active power; (e) 1.2-kVA reactive                                                                                  |    |

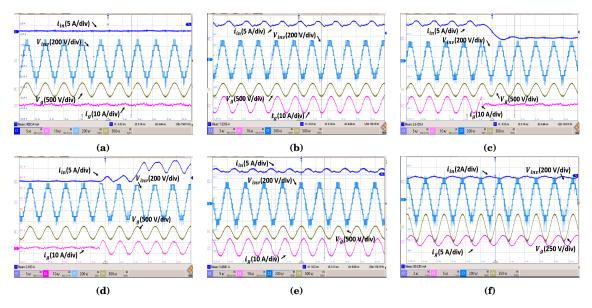

|      | power support mode; and (f) 0.5-kVA reactive power support mode [62]                                                                                             | 51 |

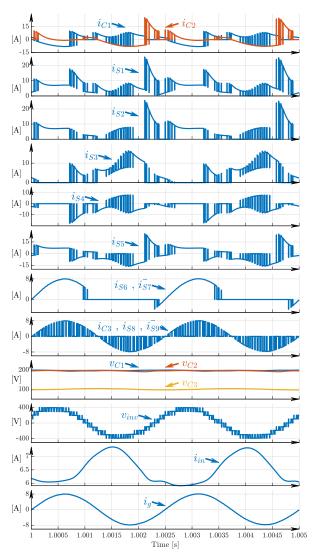

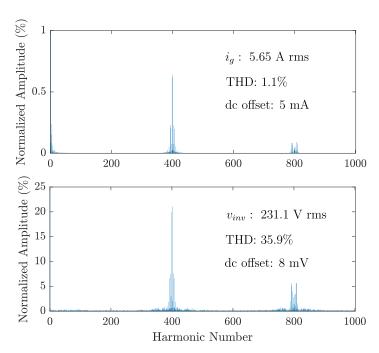

| 2.18 | Details of the simulation results at 1.2 kW injected power [75]                                                                                                  | 52 |

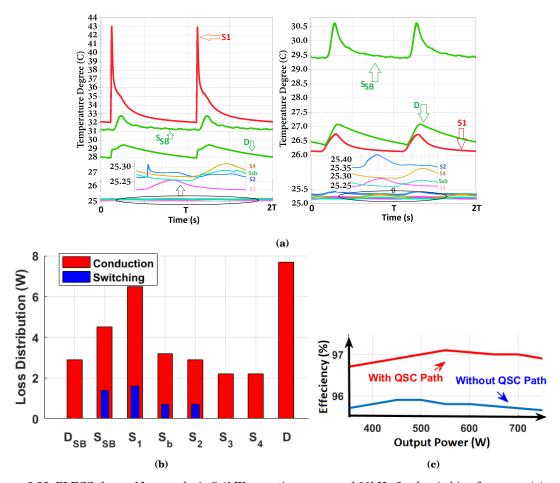

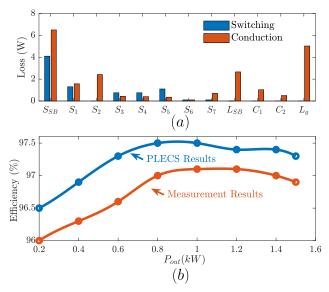

| 2.19 | Loss and efficiency analysis [75]                                                                                                                                | 53 |

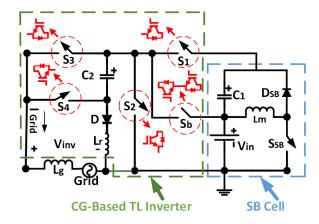

| 2 20 | The proposed CGSB5L-TL inverter topology [96]                                                                                                                    | 53 |

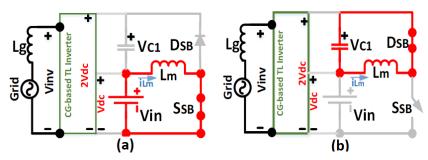

| 2.21 | Equivalent circuit of the proposed CGSB5L-TL inverter when (a) $S_{SB}$ is ON, and (b) $S_{SB}$ is OFF [96]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

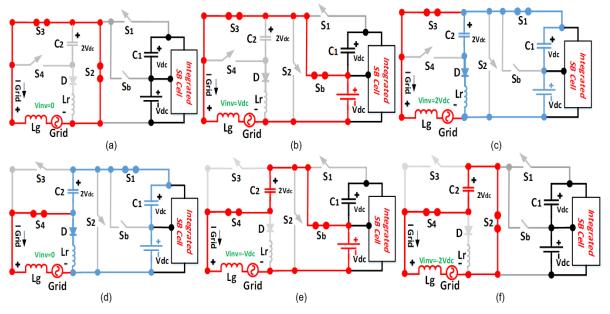

| 2.22 | Current flowing paths of the proposed SBCG5L-TL inverter showing the (a) zero-level of the output voltage in the positive half-cycle (b) first positive level of the output voltage (c) top positive level of the output voltage (d) zero-level of the output voltage in the negative half-cycle (e) first negative level of the output voltage, and (f) top negative level of the output voltage [96]                                                                                                                                                                                                                                                                                                                                                                                                                  | 55 |

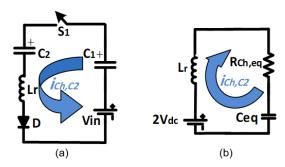

| 2.23 | Description of the QSC operation (a) main QSC path of the proposed topology (b) equivalent RLC circuit of QSC path [96]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58 |

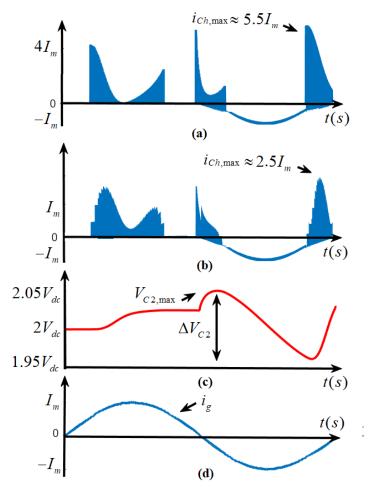

| 2.24 | Typical waveforms of (a) current passing through $C_2$ without QSC path, (b) current passing through $C_2$ with QSC path ( $L_r=22\mu H$ ), (c), the voltage across $C_2$ with QSC path (d) the injected grid current with QSC path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59 |

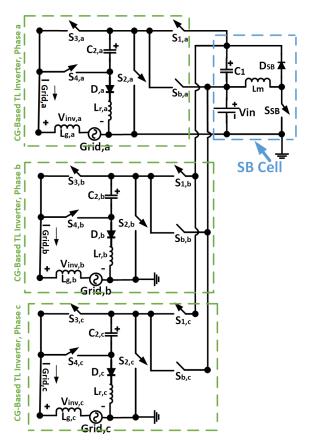

| 2.25 | Three-phase extension of the proposed CGSB5L-TL inverter [96]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61 |

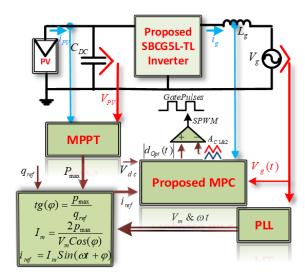

| 2.26 | Overall control diagram of the proposed CGSB5L-TL inverter with a grid-connected system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62 |

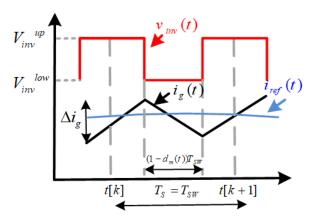

| 2.27 | The proposed CCS-MPC description with a fixed switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63 |

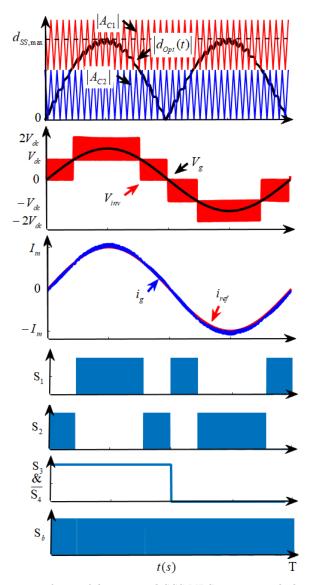

| 2.28 | Typical modulation waveforms of the proposed CCS-MPC strategy with the final gate switching pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64 |

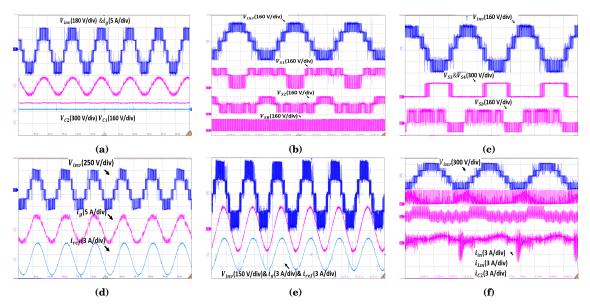

| 2.29 | A picture of the built prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69 |

| 2.30 | Measured waveforms of the inverter showing: (a) the inverter output voltage (180V/div), the injected grid current (5A/div), and the involved capacitors voltage (300V/div) and (160V/div) (b) the inverter output voltage (160V/div) and the MVS waveforms of $S_1$ , $S_2$ and $S_{SB}$ (160V/div), (c) the inverter output voltage (160V/div) and the MVS waveforms of $S_3$ and $S_4$ (300V/div) and $S_b$ (160V/div) (d) the inverter output voltage (250V/div), the injected grid current (5A/div) , and the reference current (3A/div) at the unity PF condition (e) the inverter output voltage (150V/div), the injected grid current (3A/div) , and the reference current (3A/div) at lagging PF condition (f) the inverter output voltage (300V/div), the input current, the SB cell inductor current, and the |    |

|      | current passing through $C_2$ (3A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69 |

| 2.31 | Measured waveforms of the inverter showing from top to bottom: input do voltage (200V/div& 160V/div), inverter output voltage (100V/div), injected grid current (10A/div), and grid voltage (500V/div) (a) step-up change in the dc input voltage (from 180V to 240V); (b) step-down in the current reference (from 10A to 5A at unity PF); and (c) step-uo in the current reference (from 5A to 10A at non-unity PF).                            | 70 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.32 | Three-phase measured waveforms of the proposed SBCG5L-TLinverter showing: (a) the phase to ground 5L inverter output voltage (200V/div); (b) the 9L phase to phase voltages (500V/div); (c) the injected grid current per each phase (5A/div) at unity PF                                                                                                                                                                                         | 71 |

| 2.33 | PLECS thermal/loss analysis @ 1kW operating power and 20kHz fixed switching frequency (a) steady state operating junction temperature of the semiconductors without the presence of the QSC path (left hand side) and with the presence of QSC path (right hand side) (b) conduction and switching losses distributions among the semiconductor devices, and (c) the efficiency curve versus the output power                                     | 71 |

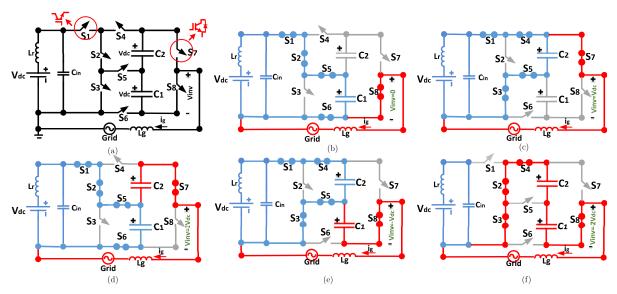

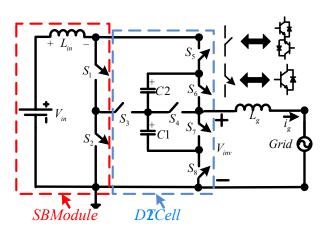

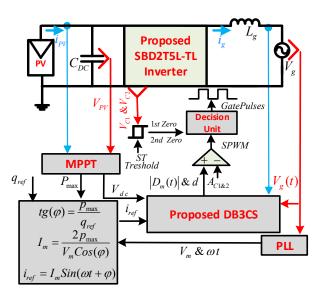

| 3.1  | The overall structure of the proposed SBD2T5L-TL inverter [105]                                                                                                                                                                                                                                                                                                                                                                                   | 74 |

| 3.2  | Different current flowing paths of the proposed SBD2T5L-TL inverter (a) the first redundant state at the zero level of the output voltage (b) the second redundant state at the zero level of the output voltage (c) at the first positive level of the output voltage (d) at the top positive level of the output voltage (e) at the first negative level of the output voltage, and (f) at the top negative                                     |    |

| 3.3  | level of the output voltage [105]                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

| 0.0  | inverter [105]                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77 |

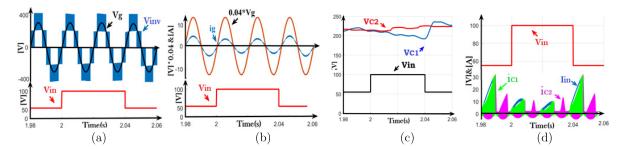

| 3.4  | Simulation results once a upward and downward step change (from 50 V to 100 V and vice versa) is applied in the input voltage: (a) 5L inverter, $\ddot{A}$ 0s output voltage with the grid/input voltage (b) the injected grid current with the grid voltage and the input voltage (c) the voltage across $C_1$ and $C_2$ with the input voltage, and (d) the input current along with the capacitors passing current and the input voltage [105] | 77 |

| 3.5  | Proposed CGSB5L-TL inverter                                                                                                                                                                                                                                                                                                                                                                                                                       | 80 |

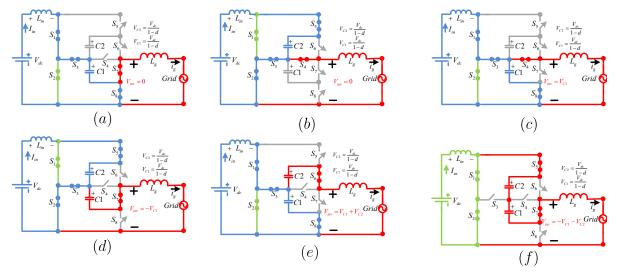

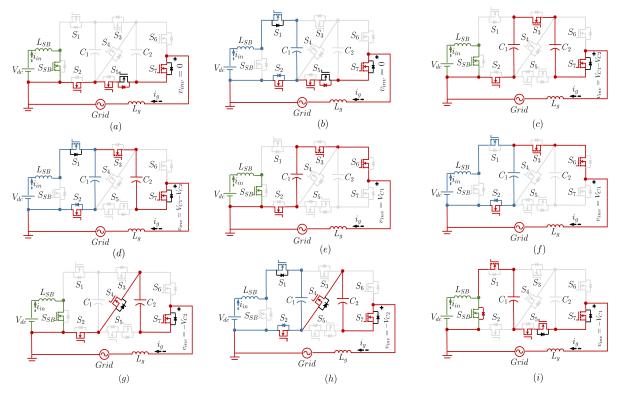

| 3.6  | Different current flowing paths of the proposed CGSB5L-TL inverter at the (a)                               |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | zero-level of the output voltage in both half-cycle in Sub-Mode I (b) zero-level                            |    |

|      | of the output voltage in both half-cycle in Sub-Mode II (c) $v_{inv} = V_{C_1} - V_{C_2}$ in                |    |

|      | Sub-Mode I, (d) $v_{inv} = V_{C_1} - V_{C_2}$ in Sub-Mode II, (e) $v_{inv} = V_{C_1}$ in Sub-Mode I,        |    |

|      | (f) $v_{inv} = V_{C_1}$ in Sub-Mode II, (g) $v_{inv} = -V_{C_2}$ in Sub-Mode I, (h) $v_{inv} = -V_{C_2}$ in |    |

|      | Sub-Mode II, and (i) $v_{inv} = -V_{C_1}$ in Sub-Mode                                                       | 80 |

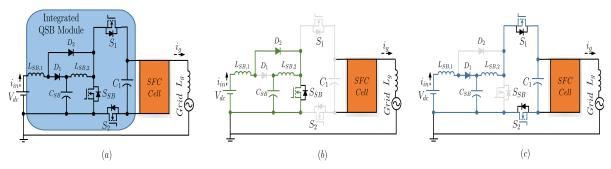

| 3.7  | Proposed QSBCG5L-TL inverter, (a) main circuit configuration, (b) operation                                 |    |

|      | in Sub-Mode I, (c) operation in Sub-Mode II [106]                                                           | 82 |

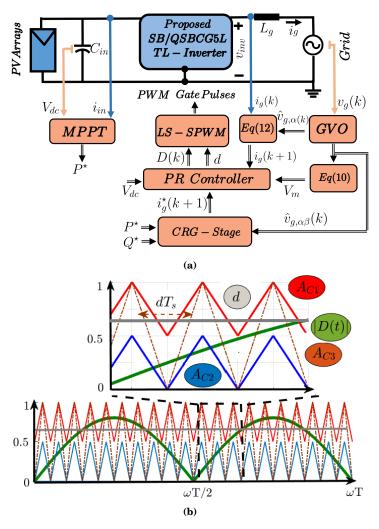

| 3.8  | (a) Closed-loop control configuration of the proposed CGSB5L-TL inverter,                                   |    |

|      | and (b) maximum boost LS-SPWM scheme [106]                                                                  | 84 |

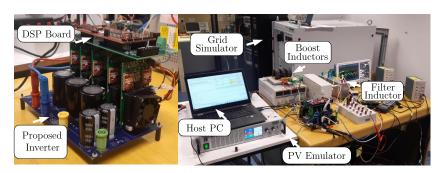

| 3.9  | Proposed CGSB5L-TL inverter prototype with the measurement setup [106].                                     | 90 |

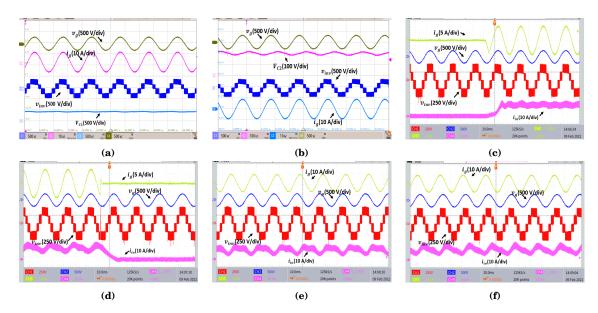

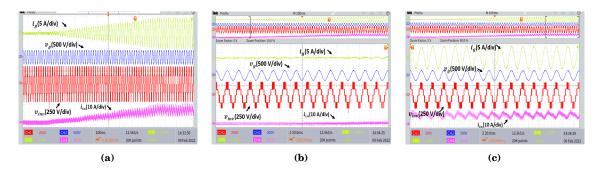

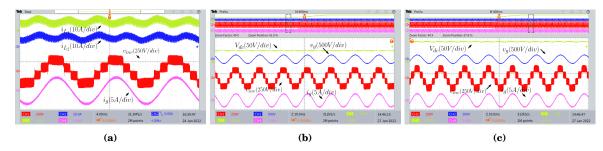

| 3.10 | Experimental waveforms of the proposed CGSB5L-TL inverter in the closed-                                    |    |

|      | loop grid-tied condition showing the grid voltage, the injected grid current,                               |    |

|      | and the 5L inverter output voltage (a) with the presence of the voltage across                              |    |

|      | $C_1$ at 1.5 kW injected power, (b) with the presence of the voltage across $C_2$                           |    |

|      | at 1.5 kW injected power, (c) with the presence of the input current when the                               |    |

|      | injected power is changed from zero to 1.1 kW, (d) with the presence of the                                 |    |

|      | input current when the injected power is changed from 1.1 kW to zero, (e)                                   |    |

|      | with the presence of the input current and under a lagging reactive power                                   |    |

|      | support mode, and (f) with the presence of the input current and under a                                    |    |

|      | leading reactive power support mode [106]                                                                   | 91 |

| 3.11 | Experimental waveforms of the proposed CGSB5L-TL inverter output voltage                                    |    |

|      | with (a) MVS across $S_3$ , and $S_4$ , (b) MVS across $S_5$ , $S_1$ , and $S_{SB}$ , and (c) MVS           |    |

|      | across $S_6, S_7,$ and $S_2$ [106]                                                                          | 91 |

| 3.12 | Grid-connected experimental result at 1 kW injected power, (a) under a dy-                                  |    |

|      | namic test in input dc voltage changing within a ramp trend from 70 V to 130                                |    |

|      | V, (b) a zoom shot of the result when the input dc voltage is at 70 V, and (c) a                            |    |

|      | zoom shot of the result when the input dc voltage is at 130 V [106]. $\ \ldots \ \ldots$                    | 92 |

| 3.13 | Grid-connected experimental result at 1.1 kW injected power, (a) under a                                    |    |

|      | dynamic test when the peak of the reference current is changed from zero to 7                               |    |

|      | A, (b) a zoom shot of the result when the peak of the reference current is zero,                            |    |

|      | and (c) a zoom shot of the result when the peak of the reference current is 7 A                             |    |

|      | [106]                                                                                                       | 92 |

| 3.14 | Grid-connected experimental result showing the leakage current propagation                                  |    |

|      | of the proposed SBCG5L-TL inverter in presence of 1.2 kW injected power [106].                              | 92 |

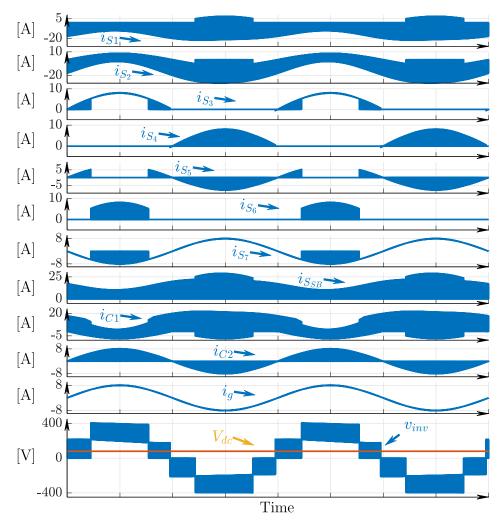

| 3.15 | Simulation results showing the current stress profile of the integrated switches               |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | and capacitors in the proposed SBCG5L-TL inverter under 1.2 kW injected                        |     |

|      | power to the grid [106]                                                                        | 93  |

| 3.16 | FFT analysis of the grid current and the inverter output voltage at 1.2 kW                     |     |

|      | injected power [106]                                                                           | 94  |

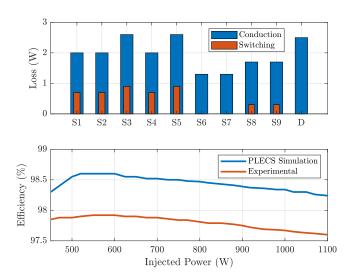

| 3.17 | (a) Loss analysis of the proposed CGSB5L-TL inverter at the rated power, and                   |     |

|      | (b) efficiency results extracted by the PLECS and measurement [106]                            | 94  |

| 3.18 | The proposed CGSB7L-TL inverter [109]                                                          | 96  |

| 3.19 | Different current flowing paths of the proposed CGSB7L-TL inverter [109]                       | 97  |

| 3.20 | Simulation results of the proposed CGSB7L-TL inverter at (a) $D=0.7$ , (b)                     |     |

|      | D = 0.8 [109]                                                                                  | 98  |

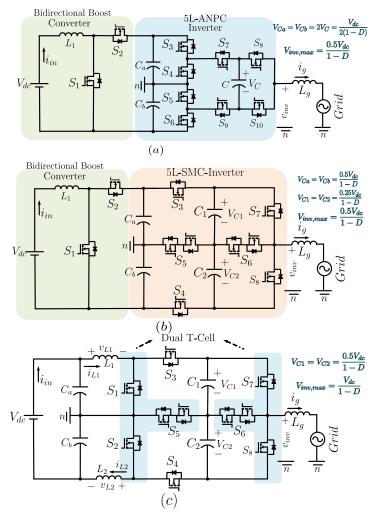

| 4.1  | Grid-connected system based on (a) conventional two-stage platform with                        |     |

|      | front-end dc-dc boost converter and a back-end ANPC-5L inverter, (b) conven-                   |     |

|      | tional two-stage platform with front-end dc-dc boost converter and a back-end                  |     |

|      | SMC-5L inverter and (c) the proposed single-stage DB-ANPC-5L inverter [111].                   | 103 |

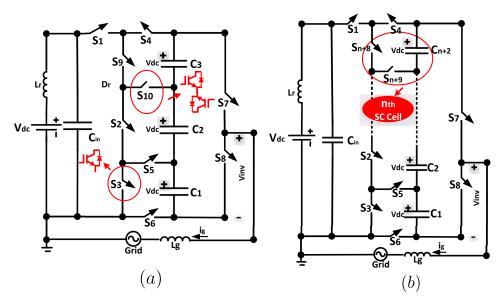

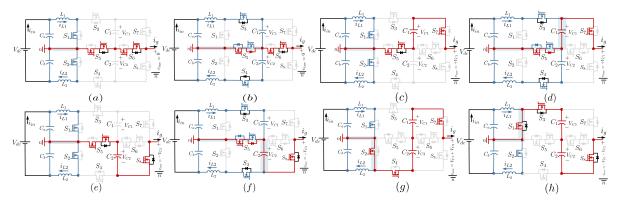

| 4.2  | Different current flowing paths of the proposed DB-ANPC-5L inverter at                         |     |

|      | (a) $v_{inv} = 0$ and charging operation of the boost inductors, (b) $v_{inv} = 0$ and         |     |

|      | charging operation of the capacitors, (c) $v_{inv} = +V_{C1}$ and charging operation of        |     |

|      | the boost inductors, (d) $v_{inv}$ = + $V_{C1}$ and charging operation of the capacitors,      |     |

|      | (e) $v_{inv} = -V_{C2}$ and charging operation of the boost inductors, (f) $v_{inv} = -V_{C2}$ |     |

|      | and charging operation of the capacitors, (g) $v_{inv} = +V_{C1} + V_{C2}$ and charging        |     |

|      | operation of the boost inductors, and (h) $v_{inv} = -V_{C1} - V_{C2}$ and charging            |     |

|      | operation of the boost inductors [111]                                                         |     |

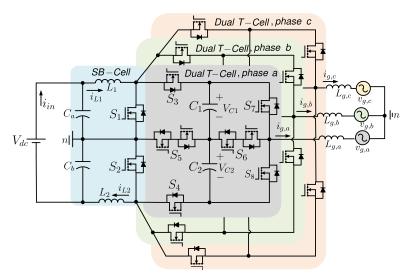

| 4.3  | Three-phase extension of the proposed DB-ANPC-5L inverter [111]                                | 104 |

| 4.4  | A comparative study of the working region between the proposed DB-ANPC-                        |     |

|      | 5L inverter and the conventional two-stage ANPC/SMC-5L-based converters,                       |     |

|      | (a) dc duty cycle, $D$ versus the overall voltage conversion gain, (b) the ratio               |     |

|      | between $V_{inv,max}/V_{dc}$ and the overall voltage conversion gain [111]                     | 107 |

| 4.5  | Modulation and gate pulses of the proposed DB-ANPC-5L inverter                                 | 109 |

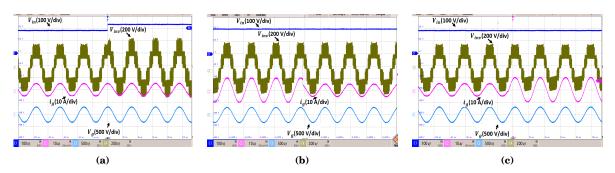

| 4.6  | Proposed DB-ANPC-5L inverter prototype with the measurement setup [111].                       | 113 |

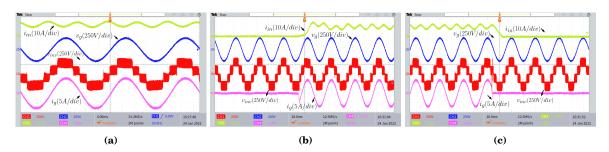

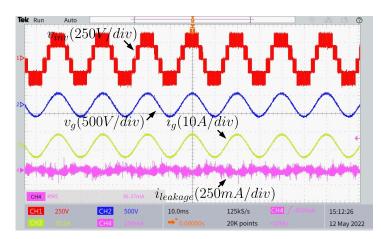

| 4.7  | Experimental results showing from up to bottom: the input current, the grid                    |     |

|      | voltage, the inverter output voltage, and the injected grid current, (a) at                    |     |

|      | 1.3 kW injected power, (b) under a dynamic test from zero to 1 kW power                        |     |

|      | injection, (c) under a dynamic test from 1 kW to zero power injection [111].                   | 113 |

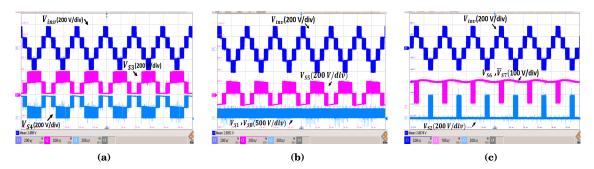

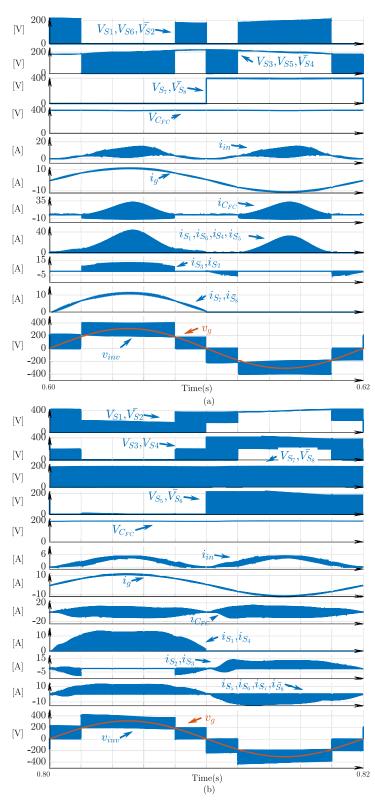

| 4.8  | Experimental results showing (a) lagging power factor ( $P^*$ = 800 W, $Q^*$ = -800 VAR) (b) leading power factor ( $P^*$ = 800 W, $Q^*$ = 800 VAR) (c) bidirectional operation ( $P^*$ = -500 W to $P^*$ = +500 W) [111]                                                                                                                                                                         | 3 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4.9  | Experimental results showing a) the input dc voltage, the capacitors boosted voltages, the inverter output voltage, and the injected grid current, (b) the voltage stress across switches $S_1$ , $S_2$ , $S_3$ , and $S_4$ in presence of the inverter output voltage, (c) the voltage stress across switches $S_5$ , $S_6$ , $S_7$ , and $S_8$ in presence of the inverter output voltage [111] |   |

| 4.10 | Experimental results showing a) the inductors currents with inverter output voltage and injected grid current at 1 kW injected power, (b) the steady-state waveforms before applying a ramp change in the input dc voltage from 80 V to 140 V, (c) the steady-state waveforms after applying a ramp change in the input dc voltage from 80 V to 140 V [111]                                       | 1 |

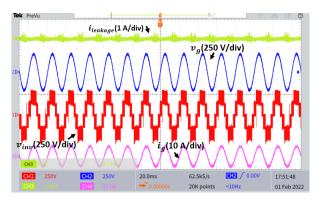

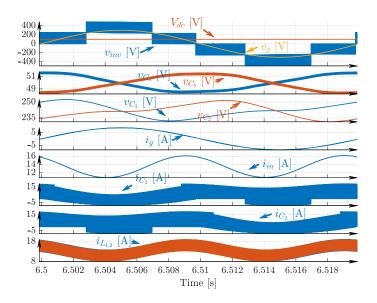

| 4.11 | Experimental results of the proposed DB-ANPC-5L inverter emphasizing on the leakage current at $P_g$ = 1.5kW [111]                                                                                                                                                                                                                                                                                |   |

| 4.12 | Detailed simulation results at $1.5~kW$ steady state injected power emphasizing on the stress on capacitors and inductors [111]                                                                                                                                                                                                                                                                   | 3 |

| 4.13 | (a) A comparative efficiency results of two-stage ANPC, two-stage SMC, and the proposed DB-ANPC-5L converters at $V_{dc}=150V$ , (b) losses distribution comparison between the two-stage ANPC converters and the proposed DB-ANPC-5L inverter at $P_g=1.5 \mathrm{kW}$ , and $V_{dc}=150V$ [111]                                                                                                 | 7 |

| 4.14 | ANPC-based 5L inverter structures, (a) conventional topology with half dc-link voltage utilization [117], (b) ABNPC-5L inverter proposed in [25] with full dc-link voltage utilization, (c) the proposed DM-ANPC-5L-Type-I converter                                                                                                                                                              | _ |

|      | [118]                                                                                                                                                                                                                                                                                                                                                                                             | 7 |

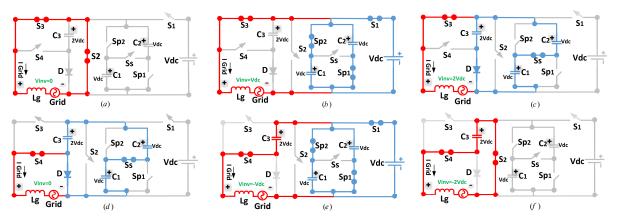

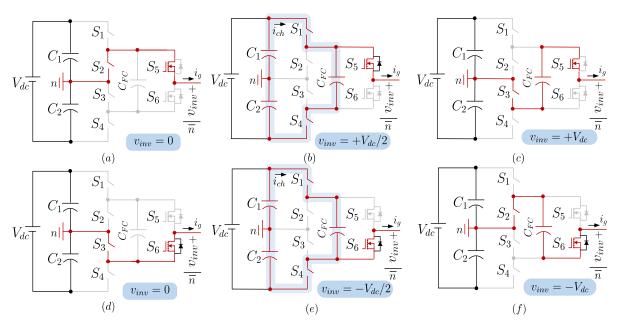

| 4.15 | Different current flowing paths of the proposed DM-ANPC-5L-Type-I inverter during boost operating mode at (a) $v_{inv}=0$ in the positive half cycle, (b) $v_{inv}=+V_{dc}/2$ , (c) $v_{inv}=+V_{dc}$ , (d) $v_{inv}=0$ in the negative half cycle, (e) $v_{inv}=-V_{dc}/2$ , and (f) $v_{inv}=-V_{dc}$                                                                                           | ) |

| 4.16 | Different current flowing paths of the proposed DM-ANPC-5L-Type-I inverter during buck operating mode at (a) $v_{inv}=0$ in the positive half cycle, (b) $v_{inv}=+V_{dc}/4$ with the first RSS, (c) $v_{inv}=+V_{dc}/4$ with the second RSS, (d) $v_{inv}=+V_{dc}/2$ , (e) $v_{inv}=0$ in the negative half cycle, (f) $v_{inv}=-V_{dc}/4$ with the                                              |   |

|      | first RSS, (g) $v_{inv} = -V_{dc}/4$ with the second RSS, (h) $v_{inv} = -V_{dc}/2$ 121                                                                                                                                                                                                                                                                                                           | 1 |

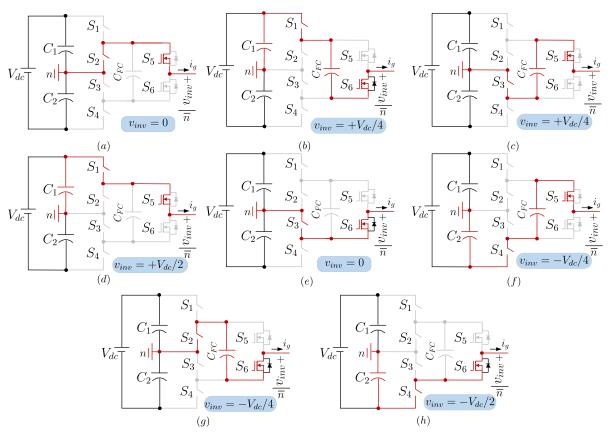

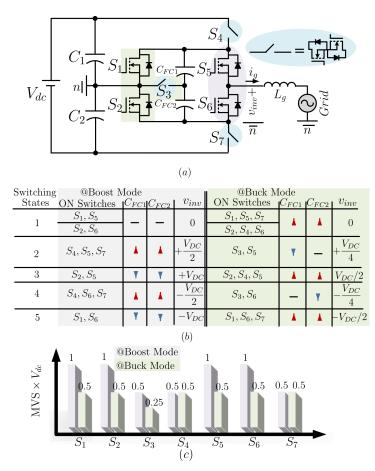

| 4.17 | Details of the modulation strategy for the proposed DM-ANPC-5L-Type-I converter, (a) with LS-PWM method in the boost mode of operation, (b) with PS-PWM method in the buck mode of operation, (c) the MVS across the switches in both modes                                                                                                                                                                                                                                                   | 122  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.18 | Proposed DM-ANPC-5L-Type-II converter, (a) the main circuit architecture, (b) the switching and FC status, (c) the MVS across the switches in both modes                                                                                                                                                                                                                                                                                                                                      | .123 |

| 4.19 | Proposed DM-ANPC-5L-Type-III converter, (a) the main circuit architecture, (b) the switching and FC status, (c) MVS across the switches in both modes. $\cdot$                                                                                                                                                                                                                                                                                                                                | 124  |

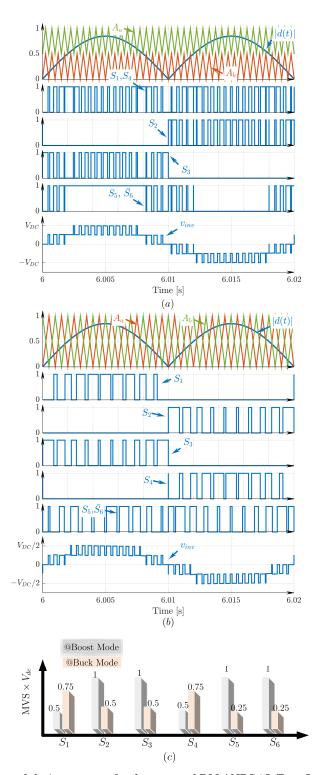

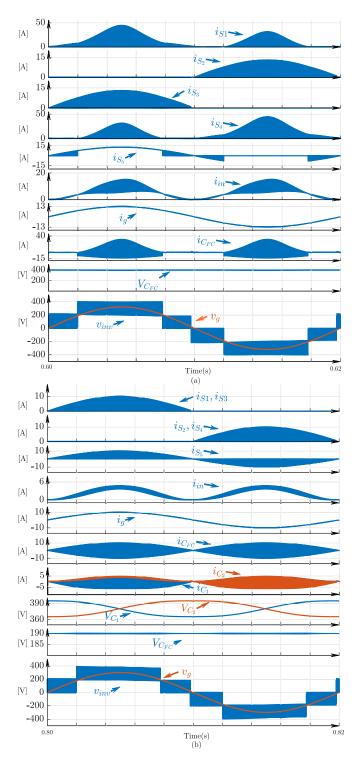

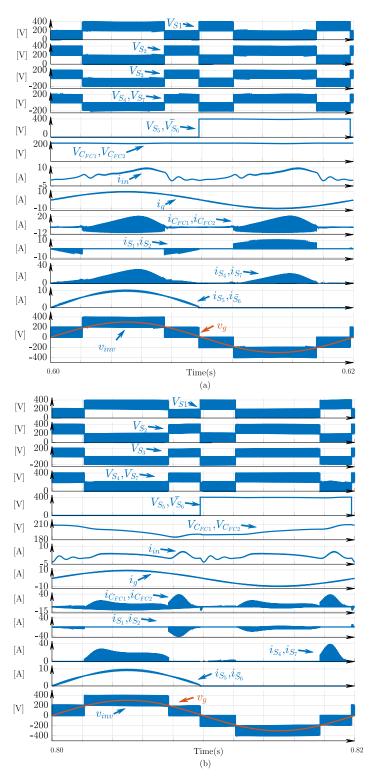

| 4.20 | Simulation results at 1.5kW steady-state grid-connected condition for the proposed DM-ANPC-5L-Type-I, (a) at the boost operating mode, (b) at the buck operating mode                                                                                                                                                                                                                                                                                                                         | 125  |

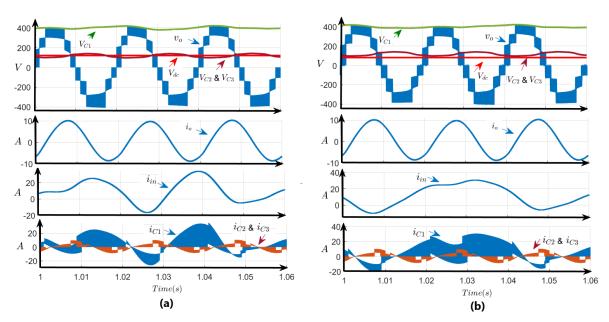

| 4.21 | Simulation results at 1.5 kW steady-state grid-connected condition for the proposed DM-ANPC-5L-Type-II, (a) at the boost operating mode, (b) at the buck operating mode                                                                                                                                                                                                                                                                                                                       | 126  |

| 4.22 | Simulation results at 1.5 kW steady-state grid-connected condition for the proposed DM-ANPC-5L-Type-III, (a) at the boost operating mode, (b) at the buck operating mode                                                                                                                                                                                                                                                                                                                      | 127  |

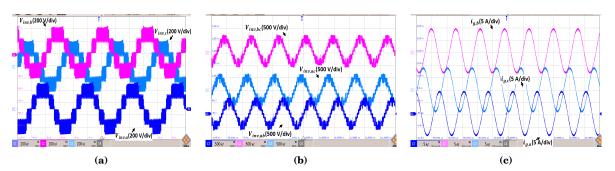

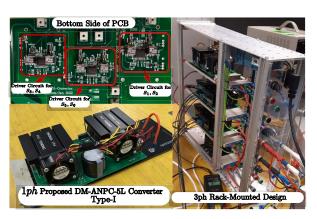

| 4.23 | Experimental prototype of the proposed DM-ANPC-5L-Type-I converter                                                                                                                                                                                                                                                                                                                                                                                                                            | 133  |

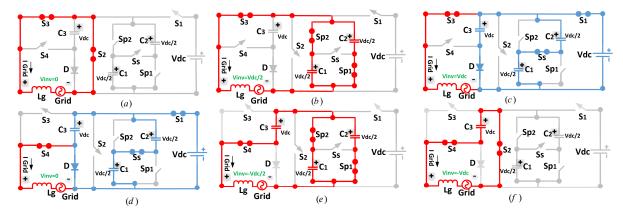

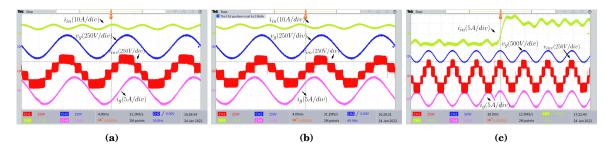

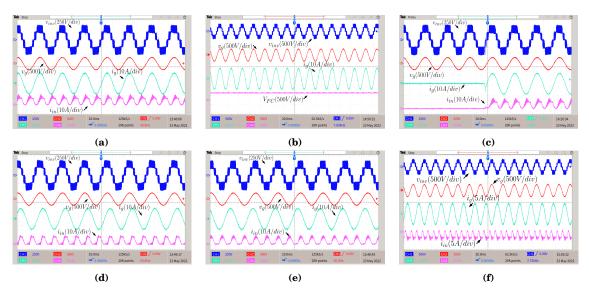

| 4.24 | Experimental results of the proposed DM-ANPC-5L-Type-I converter in the single-phase grid-connected condition and during the boost mode of operation, (a) at the rated injected power, (b) at the rated injected power and with the presence of the voltage across $C_{FC}$ , (c) with a step-change in injected power from zero to the rated power, (d) at the lagging reactive power support mode, (e) at the leading reactive power support mode (f) in the the reverse bidirectional mode | 134  |

| 4.25 | Experimental results of the proposed DM-ANPC-5L-Type-I converter in the single-phase grid-connected condition and during the buck mode of operation, (a) at the rated injected power, (b) at the rated injected power and with the presence of the voltage across dc-link capacitors and $C_{FC}$ , (c) with a stepchange in injected power from zero to 1 kW, (d) at the lagging reactive power support mode, (e) at the leading reactive power support mode (f) V2G and                     | 104  |

|      | G2V dynamic test                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 134  |

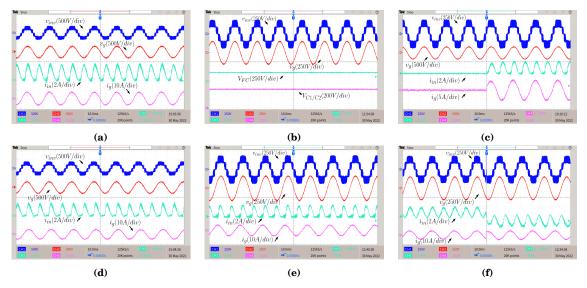

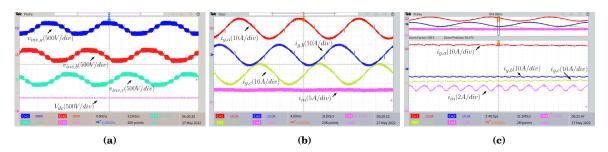

| 4.26 | Experimental results for three-phase design of the proposed DM-ANPC-5L-      |     |

|------|------------------------------------------------------------------------------|-----|

|      | Type-I converter during the boost mode of operation at $P_g$ =5.7 kW, (a) 5L |     |

|      | phase-voltage, (b) line-voltage, and (c) A zoomed shot of the injected grid  |     |

|      | current for each phase and the input current                                 | 135 |

| 4.27 | Experimental results for three-phase design of the proposed DM-ANPC-5L-      |     |

|      | Type-I converter during the buck mode of operation at $P_g$ =5.3 kW, (a) 5L  |     |

|      | phase-voltage, (b) phase-current, and (c) A zoomed shot of the injected grid |     |

|      | current for each phase and the input current                                 | 135 |

## LIST OF TABLES

| TAB | RLE Pa                                                                                                                                            | ge  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Working principle of the implemented LS-SPWM with the ON switching states of the proposed 9L9S-CGSC-TL inverter governed by a PR controller [75]. | 43  |

| 2.2 | A comparison between the proposed 9L9S-CGSC-TL inverter and other existing 9L-based inverter counterparts.                                        | 47  |

| 2.3 | Parameters used for the experimental prototype [75]                                                                                               | 48  |

| 2.4 | ON Switching States of the Proposed SBCG5L-TL Inverter Governed by the Proposed CCS-MPC Method                                                    | 62  |

| 2.5 | A Comparison Between the Proposed Topology and Existing TL Grid-Connected Converters                                                              | 66  |

| 2.6 | A Comparison Between Three-Phase Extension of Different Converters                                                                                | 67  |

| 3.1 | A Comparison Between the Proposed Topology and Existing TL Grid-Connected Converters.                                                             | 79  |

| 3.2 | ON switching states of the proposed CGSB5L-TL inverter modulated with a LS-SPWM technique                                                         | 85  |

| 3.3 | A comparison between the proposed SBCG5L-TL inverter and its other 5L-CG-Based TL-inverter counterparts                                           | 88  |

| 3.4 | Parameters used for the experimental prototype of the proposed CGSB5L-TL inverter                                                                 | 90  |

| 4.1 | Voltage stress across the switches for the proposed single-stage DB-ANPC-5L inverter and its two-stage conventional counterparts.                 | 105 |

| 4.2 | ON switching states of the proposed DB-ANPC-5L inverter modulated with a PS-PWM technique                                                         | 108 |

| 4.3 | A comparison between the proposed DB-ANPC-5L inverter and the other single-source 5L-SB-based inverters                                           | 112 |

#### LIST OF TABLES

| 4.4 | A comparison between the proposed DM-ANPC-5L converters and their other |     |

|-----|-------------------------------------------------------------------------|-----|

|     | available 5L inverters/converters counterparts                          | 131 |

### **ACRONYMS**

- PV: Photovoltaic

- RE: Renewable Energy

- APD: Active Power Decoupling

- MPPT: Maximum Power Point Tracking

- GT-ACM: Grid-Tied-AC Module

- **LF**: Low Frequency

- **HF**: High Frequency

- CMV: Common Mode Voltage

- **PQE**: Power Quality Enhancement

- CG: Common-Ground

- TSV: Total Standing Voltage

- ullet SC: Switched-Capacitor

- SB: Switched-Boost

- LS-PWM: Level-Shifted Pulse Width Modulation

- PS-PWM: Phase-Shifted Pulse Width Modulation

- MLIs: Multilevel Inverters

- **FC**: Flying-Capacitor

- ANPC: Active Neutral Point Clamped

- ABNPC: Active Boost Neutral Point Clamped

- CPC: Charge Pumped Circuit

- MPC: Model Predictive Control

- **DBC**: Dead-Beat Controller

- **SMC**: Sliding Mode Control

- **HCC**: Hystresis Current Control

- **FC**: Flying-Capacitor

- FCS-MPC: Finite-Control-Set MPC

- CCS-MPC: Continuous-Control Set MPC

- VOC: Voltage Oriented Control

- **THD**: Total Harmonic Distortion

- PLL: Phase Locked Loops

- **SRF**: Synchronous Reference Frame

- GVO: Grid Voltage Observer

- **PI**: Proportional-Integrator

- **PR**: Proportional-Resonant

- MVS: Maximum Voltage Stress

- QSC: Quasi Soft Charging

- LDT: Longest Discharging Time

- **RSS**: Redundant Switching State

CHAPTER

INTRODUCTION

## 1.1 Recent Advances on Grid-Tied Transformerless Inverters

he integration of intermittent renewable energy (RE)-based resources, e.g., PV arrays, fuel cells, batteries and wind turbines in power grids and the new policies of the governments to reduce the need for fossil fuels dependent energy generation have accelerated the necessity of efficient and reliable energy management in a multigeneration source network [1]. As for the low power-scaled single-phase grid-tied utilities, a PV panel is directly connected to a power electronic converter within a single or two stages operation as illustrated in Fig. 1.1. Maximum power point tracking (MPPT), active power decoupling (APD), grid current control regulation, PV voltage amplification, islanding detection and the power quality enhancements are some crucial and strict missions, which must be taken into account in designing any new breed of grid tied-AC module (GT-ACM) systems [2].

In two-stage power conversion systems, utilization of the front-end dc-dc boost or buck-boost converter is imperative as the MPPT operation even with presence of a wide varying dc link voltage in the PV string modules is facilitated [3]. Moreover, in case of having a low available dc voltage magnitude, a voltage boosting feature can be added to the entire power conversion process in order to meet the peak voltage requirement of the grid. Applying APD in single-phase grid-connected applications [4],[5], and drawing