# Single-Stage Grid-Connected Multilevel Converters: Topologies and Control Strategies

by Majid Farhangi

Thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy under the supervision of Prof. Dylan Lu A/ Prof. Yam P. Siwakoti

> School of Electrical and Data Engineering Faculty of Engineering and IT University of Technology Sydney 06/12/2023

## Certificate of Authorship / Originality

I, Majid Farhangi, declare that this thesis is submitted in fulfilment of the requirements for the award of Doctor of Philosophy, in the School of Electrical and Data Engineering at the University of Technology Sydney.

This thesis is wholly my own work unless otherwise referenced or acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis. This document has not been submitted for qualifications at any other academic institution.

This research is supported by the Australian Government Research Training Program.

Production Note: Signature: Signature removed prior to publication.

Date:

December 7, 2023

### Abstract

The global need for sustainable energy supplies is one of the major drivers in the power electronics industry. In this work, the main challenges and objectives for multilevel power converters in grid-connected applications have been elaborated. To address the identified requirements and challenges, a family of efficient multilevel converters with the single-stage dynamic voltage-boosting feature, reduced number of circuit components, modular structure, and bidirectional operation is presented. The aforementioned advantages make this converter a suitable candidate for renewable energy applications. Moreover, to further improve the performance of the proposed converter, an active power decoupling (APD) strategy for single-phase grid-connected inverters is presented to cancel out the double-line frequency ripple in the input current profile. This enables the converter to be employed in a broad range of grid-connected applications with improved efficiency without adding extra components to the circuit. The experimental results show more than 1%improvement in conversion efficiency over the whole power range, only by applying the proposed control strategy. Additionally, a flexible APD control strategy is applied to continuously adjust the tradeoff between the DC input current ripple and voltage stress on the circuit components, while retaining the power quality requirements of a standard grid-connected inverter. The voltage stress on the circuit components can be reduced by up to 17% with the proposed method compared to the conventional APD approaches. Furthermore, to address the scalability requirement of the single-stage DC-AC converters, a new transformerless grid-connected inverter with a commongrounded circuit architecture and single-stage dynamic voltage boosting gain is proposed. The key features of the presented inverter are the reduced current stress profile, modularity, uniform peak voltage stress on the switches, higher power handling capability, and bidirectional power flow operation. Through a modular design with a phase-shifted modulation, the injected grid current can be shared among the modules, while the size of the gridinterface filters can be reduced. The working principle and the generalized form of the converter are discussed, and some simulation and experimental

results are presented to validate its feasibility, achieving more than 95% efficiency in grid-connected mode at 120 V DC input voltage over a broad power range. Finally the conclusions and recommended future works are provided.

# Dedication

To my wife, my family, and my friends

### Acknowledgements

I would like to thank my wife, my family, my friends, and my colleagues who encouraged and helped me in this journey.

Also, I would like to express my gratitude to my supervisors Prof. Dylan Lu and Prof. Yam Siwakoti for their continuous support and guidance. In addition, I'm deeply thankful to Prof. Ricardo Aguilera for his valuable insights and support during my PhD studies.

Finally, I'm grateful to my dear friend, Dr. Reza Barzegarkhoo, who continuously helped me in this path, working and learning together.

Majid Farhangi December 7, 2023 Sydney, Australia

### List of Publications

#### **Journal Papers:**

- M. Farhangi, R. Barzegarkhoo, S. S. Lee, R. P. Aguilera, D. D. -C. Lu, and Y. P. Siwakoti, "An Interleaved Single-Stage Switched-Boost Common-Ground Multilevel Inverter: Design, Control, and Experimental Validation," in IEEE Trans. Ind. Appl., 2023. (Under Review)

- M. Farhangi, R. Barzegarkhoo, R. P. Aguilera, D. D. -C. Lu, M. Liserre and Y. P. Siwakoti, "A Single-Stage Switched-Boost Grid-Connected Five-Level Converter With Integrated Active Power Decoupling Under Polluted Grid Voltage Condition," in IEEE open j. Ind. Electron. Soc., vol. 4, pp. 328-345, 2023, doi: 10.1109/OJIES.2023.3305492.

- M. Farhangi, R. Barzegarkhoo, R. P. Aguilera, S. S. Lee, D. D. -C. Lu and Y. P. Siwakoti, "A Single-Source Single-Stage Switched-Boost Multilevel Inverter: Operation, Topological Extensions, and Experimental Validation," in IEEE Trans. Power Electron., vol. 37, no. 9, pp. 11258-11271, Sept. 2022, doi: 10.1109/TPEL.2022.3163762.

#### **Conference Papers:**

- M. Farhangi, R. Barzegarkhoo, R. P. Aguilera, Y. P. Siwakoti, D. D. -C. Lu, "A Flexible Active Power Decoupling Strategy for A Switched-Boost Single-Stage Grid-Connected Multilevel Inverter," 2023 IEEE Intl. Future Energy Electron. Conf. (IFEEC), Sydney, Australia, 2023.

- M. Farhangi, R. Barzegarkhoo, S. S. Lee, D. Lu and Y. Siwakoti, "An Interleaved Switched-Boost Common-Ground Five-Level Inverter," 2022 Intl. Power Electron. Conf. (IPEC-Himeji 2022- ECCE Asia), Himeji, Japan, 2022, pp. 867-872, doi: 10.23919/IPEC-Himeji2022-ECCE53331. 2022.9807154.

M. Farhangi, R. Barzegarkhoo, Y. P. Siwakoti, D. Lu and S. S. Lee, "A Novel Single-Source Single-Stage Switched-Boost Five-Level (S5B5L) Inverter With Dynamic Voltage Boosting Feature," 2021 IEEE Energy Convers. Congr. Expo. (ECCE), 2021, pp. 2557-2562, doi: 10.1109/ECCE47101.2021.9595174.

## Related/Collaborative Publications: Journal Papers:

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, M. Liserre and Y. P. Siwakoti, "New Family of Dual-Mode Active Neutral Point-Clamped Five-Level Converters," in IEEE Trans. Power Electron., doi: 10.1109/TPEL.2023.3283694.

- Y. Y. Syasegov, M. Farhangi, R. Barzegarkhoo, Y. P. Siwakoti, L. Li, D. D. -C. Lu, R. P. Aguilera and J. Pou, "A 5-Level HERIC Active-Clamped Inverter With Full Reactive Power Capability for Grid-Connected Applications," in IEEE open j. Ind. Electron. Soc., vol. 4, pp. 135-148, 2023, doi: 10.1109/OJIES.2023.3271637.

- Y. Y. Syasegov, M. Farhangi, R. Barzegarkhoo, L. Li, D. D. -C. Lu, R. P. Aguilera and Y. P. Siwakoti, "HERIC-Clamped and PN-NPC Inverters With Five-Level Output Voltage and Reduced Grid-Interfaced Filter Size," in IEEE open j. power electron., vol. 4, pp. 306-318, 2023, doi: 10.1109/OJPEL.2023.3265062.

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, F. Blaabjerg and Y. P. Siwakoti, "A Novel Active Neutral Point-Clamped Five-Level Inverter With Single-Stage-Integrated Dynamic Voltage Boosting Feature," in IEEE Trans. Power Electron., vol. 38, no. 6, pp. 7796-7809, June 2023, doi: 10.1109/TPEL.2023.3257959.

- S. S. Lee, S. Cao, R. Barzegarkhoo, M. Farhangi and Y. P. Siwakoti, "Single-Phase 5-Level Split-Midpoint Cross-Clamped (5L-SMCC) Inverter: An Alternative to the Two-Stage ANPC Topology," in Trans. Emerg. Sel. Topics Power Electron., vol. 11, no. 2, pp. 1995-2003, April 2023, doi: 10.1109/JESTPE.2023.3236012.

- R. Barzegarkhoo, M. Farhangi, R. P. Aguilera, S. S. Lee, F. Blaabjerg and Y. P. Siwakoti, "Common-Ground Grid-Connected Five-Level Transformerless Inverter With Integrated Dynamic Voltage Boosting Feature," in IEEE Trans. Emerg. Sel. Topics Power Electron., vol. 10, no. 6, pp. 6661-6672, Dec. 2022.

R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, Y. P. Siwakoti and J. Pou, "Nine-Level Nine-Switch Common-Ground Switched- Capacitor Inverter Suitable for High-Frequency AC-Microgrid Applications," in IEEE Trans. Power Electron., vol. 37, no. 5, pp. 6132-6143, May 2022, doi: 10.1109/TPEL.2021.3131847.

#### **Conference Papers:**

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera, Y. P. Siwakoti and M. Liserre, "Active Neutral Point-Clamped Five-Level Inverter With Single-Stage Dynamic Voltage Boosting Capability," 2022 IEEE 13th Intl. Symp. on Power Electron. for Distributed Generation Systems (PEDG), Kiel, Germany, 2022, pp. 1-6, doi: 10.1109/PEDG54999. 2022.9923158.

- R. Barzegarkhoo, M. Farhangi, S. S. Lee, R. P. Aguilera and Y. P. Siwakoti, "A Novel Seven-Level Switched-Boost Common-Ground Inverter With Single-Stage Dynamic Voltage Boosting Gain," 2022 Intl. Power Electron. Conf. (IPEC-Himeji 2022- ECCE Asia), Himeji, Japan, 2022, pp. 873-877, doi: 10.23919/IPEC-Himeji2022-ECCE53331. 2022.9807006.

- M. Farhangi, Y. P. Siwakoti, R. Barzegarkhoo, S. U. Hasan, D. Lu and D. Rogers, "A Compact Design Using GaN Semiconductor Devices for a Flying Capacitor Five-Level Inverter," 2021 IEEE Energy Convers. Congr. Expo. (ECCE), 2021, pp. 2475-2479, doi: 10.1109/ECCE47101. 2021.9595266.

- R. Barzegarkhoo, M. Farhangi, R. P. Aguilera, Y. P. Siwakoti and S. S. Lee, "Switched-Boost Common-Ground Five-Level (SBCG5L) Grid-Connected Inverter With Single-Stage Dynamic Voltage Boosting Concept," 2021 IEEE Energy Convers. Congr. Expo. (ECCE), 2021, pp. 1014-1019, doi: 10.1109/ECCE47101.2021.9595581.

# Contents

| 1        | Intr | oducti               | ion                                                     | <b>2</b> |

|----------|------|----------------------|---------------------------------------------------------|----------|

|          | 1.1  | Resear               | rch Objectives                                          | 4        |

|          | 1.2  | Thesis               | Overview                                                | 5        |

| <b>2</b> | Lite | erature              | Review                                                  | 7        |

|          | 2.1  | DC-A                 | C Converters                                            | 7        |

|          |      | 2.1.1                | DC-AC Converter Configurations                          | 9        |

|          |      | 2.1.2                | Conventional 3L Converters                              | 9        |

|          |      | 2.1.3                | Extension Techniques                                    | 15       |

|          |      | 2.1.4                | Comparative Study                                       | 18       |

|          | 2.2  | Contro               | ol and Modulation                                       | 24       |

|          |      | 2.2.1                | Control Targets                                         | 24       |

|          |      | 2.2.2                | Controller Types                                        | 26       |

|          |      | 2.2.3                | Modulators                                              | 28       |

|          |      | 2.2.4                | Control Strategies for Grid-Connected Inverters         | 31       |

|          | 2.3  | Design               | n Challenges in Grid-Connected Inverters                | 36       |

|          |      | 2.3.1                | Grid Filter Size and Power Quality                      | 36       |

|          |      | 2.3.2                | Non-Ideal Grids and Voltage Harmonics                   | 38       |

|          |      | 2.3.3                | Scalability and Modular Structure                       | 38       |

|          |      | 2.3.4                | Power Decoupling                                        | 39       |

|          |      | 2.3.5                | Single-Stage Dynamic Voltage Boosting and Bidirec-      |          |

|          |      |                      | tional Power Flow                                       | 40       |

|          |      | 2.3.6                | Research Gaps                                           | 42       |

| 3        | A S  | ingle-S              | Source Single-Stage Switched-Boost Multilevel In-       |          |

|          | vert | $\operatorname{ter}$ |                                                         | 43       |

|          | 3.1  | Introd               | uction                                                  | 43       |

|          | 3.2  | Propo                | sed $S^5B5L$ -VSI                                       | 44       |

|          | 3.3  | Topolo               | ogical Extensions                                       | 52       |

|          |      | 3.3.1                | Three-Phase 3L Extension of the Proposed Topology $\ .$ | 52       |

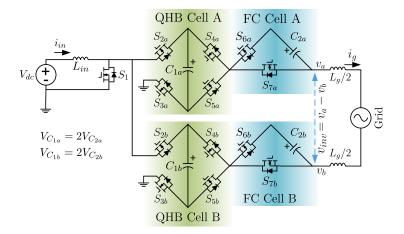

|          |                                         | 3.3.2 Extended 9L-FC-Based Variant of the Proposed Topol-                             |                 |

|----------|-----------------------------------------|---------------------------------------------------------------------------------------|-----------------|

|          | 0.4                                     | $\operatorname{ogy}$                                                                  | 53              |

|          | 3.4                                     | Passive Elements Design Guidelines and Power Loss Analysis .                          | 55              |

|          |                                         | 3.4.1 Passive Elements Design Guidelines                                              | $55 \\ 58$      |

|          | 3.5                                     | 3.4.2 Power Loss Analysis                                                             | $\frac{58}{61}$ |

|          |                                         | Comparative Study                                                                     | 65              |

|          | $\begin{array}{c} 3.6\\ 3.7\end{array}$ | Control Strategy                                                                      | 65              |

|          | 5.7                                     | Simulation and Experimental Results                                                   | 66              |

|          |                                         | 3.7.2 Experimental Results                                                            | 00<br>70        |

|          | 3.8                                     | Conclusion                                                                            |                 |

|          | 0.0                                     |                                                                                       | ••              |

| 4        |                                         | ingle-Stage Switched-Boost Grid-Connected Five-Level                                  |                 |

|          |                                         | verter With Integrated Active Power Decoupling Under<br>corted Grid Voltage Condition | 78              |

|          | 4.1                                     | Introduction                                                                          | 78              |

|          | 4.2                                     | Closed-Loop Control Strategy Applied to the $S^5B5L$ Converter                        | 10              |

|          | 4.2                                     | Without APD Under Distorted Grid Voltage                                              | 80              |

|          | 4.3                                     | Proposed Control Strategy with APD Under Distorted Grid                               | 00              |

|          | 1.0                                     | Voltage                                                                               | 81              |

|          |                                         | 4.3.1 GVO Mechanism                                                                   | 86              |

|          |                                         | 4.3.2 Reference Design                                                                | 89              |

|          |                                         | 4.3.3 Stability and Sensitivity Analysis                                              | 92              |

|          | 4.4                                     | Comparative Study                                                                     | 97              |

|          |                                         | 4.4.1 Performance Investigation of the S <sup>5</sup> B5L Converter With              |                 |

|          |                                         | and Without APD                                                                       | 97              |

|          |                                         | 4.4.2 A Comparison over Other Available Topologies with                               |                 |

|          |                                         | APD Control                                                                           |                 |

|          | 4.5                                     | Experimental Results                                                                  |                 |

|          | 4.6                                     | Conclusion                                                                            | 114             |

| <b>5</b> | Flex                                    | tible Active Power Decoupling for A Single-Stage Single-                              |                 |

|          |                                         |                                                                                       | 115             |

|          | 5.1                                     |                                                                                       | 115             |

|          | 5.2                                     | APD Working Principle                                                                 |                 |

|          | 5.3                                     | FAPD Working Principle                                                                |                 |

|          | 5.4                                     | Control Strategy                                                                      |                 |

|          |                                         | 5.4.1 System Modeling                                                                 |                 |

|          |                                         | 5.4.2 Model Predictive Control                                                        |                 |

|          |                                         | 5.4.3 Grid Voltage Observer                                                           |                 |

|          |                                         | 5.4.4 Reference Design                                                                | 123             |

|   |      | 5.4.5 State Observer $\ldots \ldots 12$ | 4        |

|---|------|--------------------------------------------------------------------------------------------------------|----------|

|   |      | 5.4.6 Capacitor Voltage Controller                                                                     | 5        |

|   |      | 5.4.7 Minimum Capacitor Voltage Reference Estimation 12                                                | 5        |

|   | 5.5  | Theoretical Analysis                                                                                   | 7        |

|   | 5.6  | Sensitivity Analysis                                                                                   | 7        |

|   | 5.7  | Simulation Results                                                                                     | 9        |

|   | 5.8  | Conclusion                                                                                             | 3        |

| 6 | An   | Interleaved Single-Stage Switched-Boost Common-Ground                                                  |          |

|   | Mu   | tilevel Inverter: Design, Control, and Experimental Val-                                               |          |

|   | idat | ion 14                                                                                                 | 7        |

|   | 6.1  | Introduction                                                                                           | 7        |

|   | 6.2  | Proposed Interleaved CGSB-MLI and Its Modulation/Control                                               |          |

|   |      | Strategy                                                                                               | 8        |

|   |      | 6.2.1 Working Principle of the Proposed Generalized Topology14                                         | 8        |

|   |      | 6.2.2 Modulation/Control Strategy for A 7L Variant of the                                              |          |

|   |      | Proposed Converter                                                                                     | 2        |

|   | 6.3  | Passive Elements Design Guidance                                                                       |          |

|   |      | 6.3.1 Design of $L_{dc_x}$ and $C_x$                                                                   |          |

|   |      | 6.3.2 Design of $L_{g_x}$ and $L_g$                                                                    |          |

|   | 6.4  | Sensitivity Analysis                                                                                   |          |

|   | 6.5  | Comparative Study                                                                                      | 4        |

|   | 6.6  | Experimental Results                                                                                   |          |

|   | 6.7  | Conclusion                                                                                             | 0        |

| 7 | Con  | clusions and Future Work 18                                                                            | <b>2</b> |

|   | 7.1  | Recommendations & Future Works                                                                         | 4        |

# List of Figures

| 1.1  | DC-AC converter architectures: (a) conventional two-stage inverter with a dedicated boost stage, (b) single-stage inverter |    |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

|      | with integrated voltage boosting capability                                                                                | 4  |

| 2.1  | DC-AC converter types.                                                                                                     | 8  |

| 2.2  | DC-AC converter configurations.                                                                                            | 10 |

| 2.3  | Conventional 3L inverter topologies: (a) H-bridge; (b) NPC [30]; (c) ANPC [31]; (d) T-Type [32]; (e) HERIC [36]; (f)       |    |

|      | H5 [37]; (g) PN-NPC [38]; (h) SSI [39]; (i) qZ-source [16]                                                                 | 14 |

| 2.4  | An overview of the available extension techniques for DC-AC                                                                |    |

|      | converters                                                                                                                 | 15 |

| 2.5  | Conventional multilevel converters based on cascading tech-                                                                |    |

|      | nique: (a) CHB [46]; (b) MMC [47]                                                                                          | 16 |

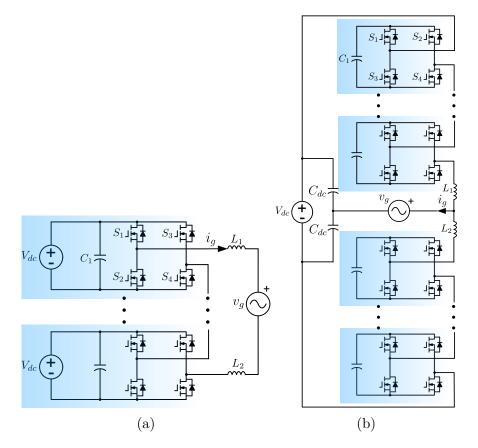

| 2.6  | Examples of single-phase interleaved DC-AC converters based                                                                |    |

|      | on: (a) conventional half-bridge topology; (b) conventional                                                                |    |

|      | H-bridge topology; (c) Siwakoti-H topology [52]; (d) T-type                                                                |    |

|      | topology; (e) quasi Z-source topology [16]                                                                                 | 19 |

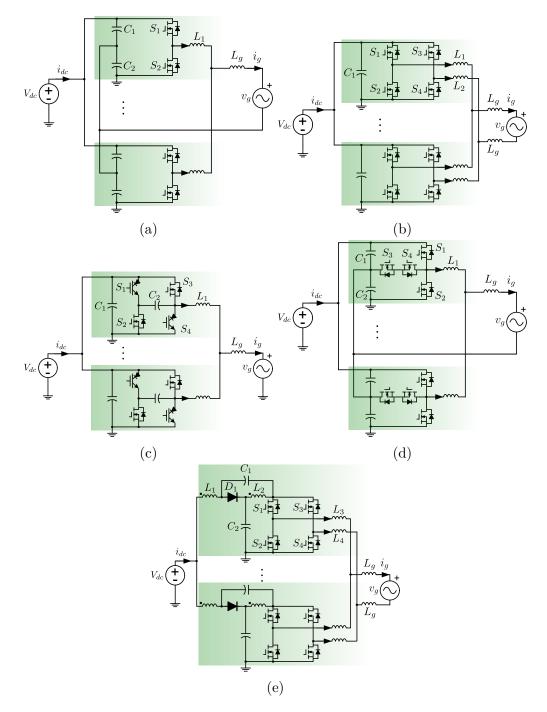

| 2.7  | Buck-based multilevel converters: (a) Hybrid ANPC [58]; (b)                                                                |    |

|      | SMC [59]; (c) Hybrid CG [60]; (d) Hybrid CG [25]; (e) Hybrid                                                               |    |

|      | CG [61]; (f) ABNPC [62]; (g) Hybrid T-Type [26]; (h) Hybrid                                                                |    |

|      | MC [63]; (i) Hybrid FC [64]; (j) PUC5 [65]                                                                                 | 20 |

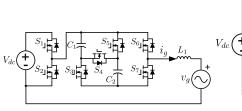

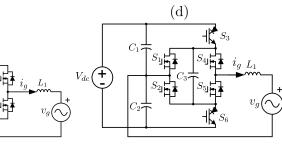

| 2.8  | Boost-based multilevel converters: (a) Hybrid ANPC [66]; (b)                                                               |    |

|      | Hybrid SB $[67]$ ; (c) Hybrid SB $[68]$ ; (d) Hybrid SB $[27]$ ; (e)                                                       |    |

|      | Hybrid SB [24]; (f) Hybrid qZ-Source [69]. $\ldots$                                                                        | 21 |

| 2.9  | Dual-mode 5L converter [57]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                  | 22 |

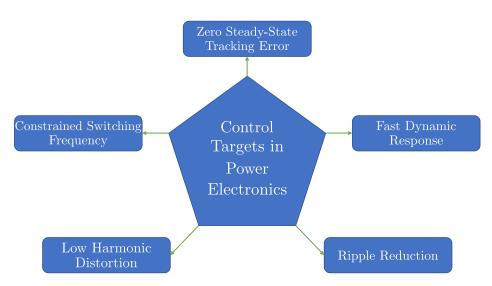

| 2.10 | Major control targets in power electronics converters                                                                      | 24 |

| 2.11 |                                                                                                                            |    |

|      | (b) controller without modulator                                                                                           | 27 |

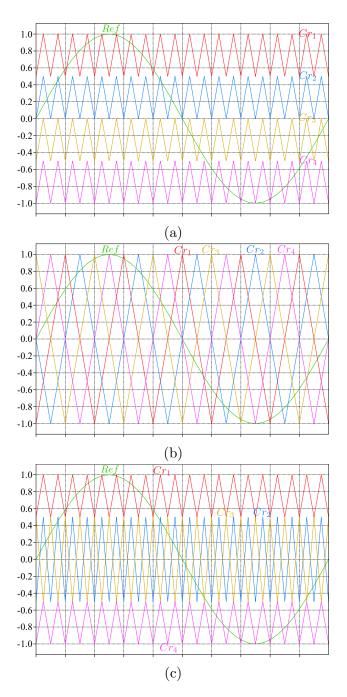

| 2.12 | Carrier-based PWM methods for multilevel converters: (a)                                                                   |    |

|      | LS-PWM; (b) PS-PWM; (c) Hybrid PWM                                                                                         | 30 |

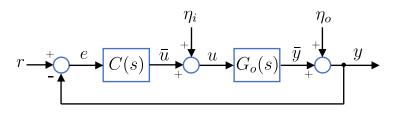

| 2.13 | A block diagram view of a generic closed-loop control system.                                                              | 32 |

| 2.14        | Simplified block diagram view of conventional frequency-domain<br>control strategies for grid-connected inverters: (a) PI con- |          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----------|

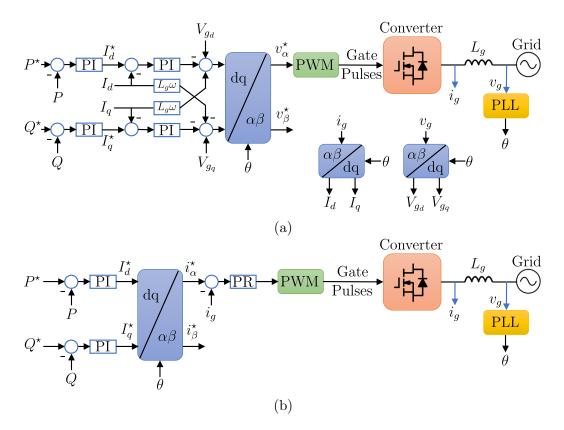

| 2.15        | troller; (b) PR controller                                                                                                     | 34<br>40 |

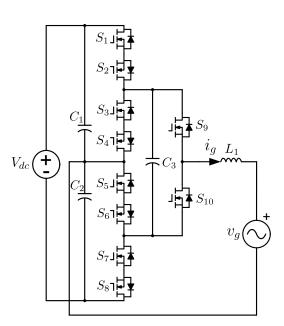

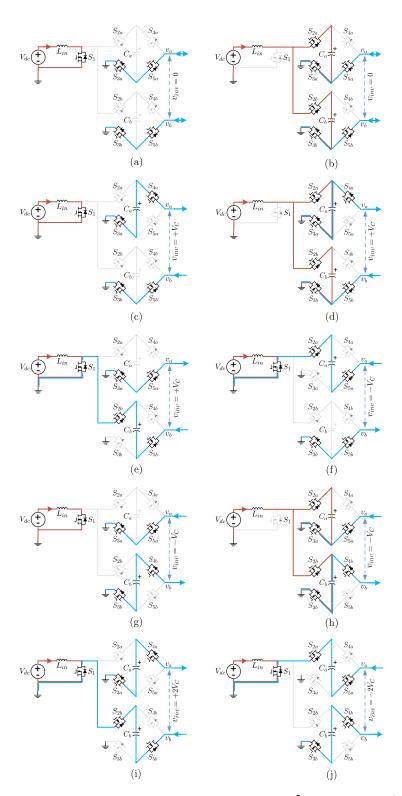

| 3.1<br>3.2  | The proposed S <sup>5</sup> B5L-VSI                                                                                            | 45       |

| 3.3         | $v_{inv} = -2V_C \ (L_{in}: \text{ Charging}).$                                                                                | 46<br>51 |

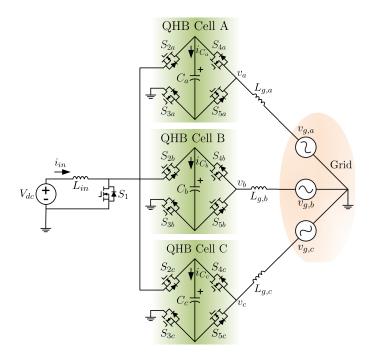

| 3.4         | Three-phase 3L extension of the proposed $S^5B5L-VSI$                                                                          | 53       |

| 3.5         | The 9L circuit extension of the proposed topology.                                                                             | 54       |

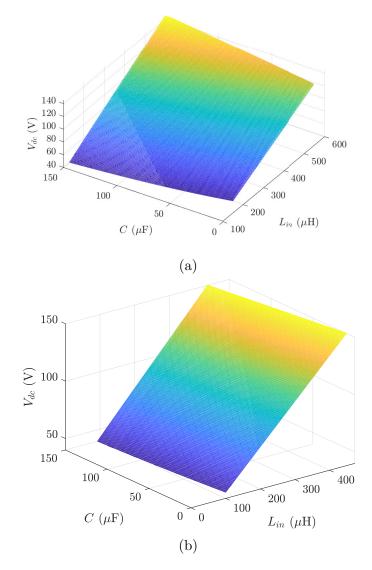

| 3.6         | Boundary values of input inductor and module capacitors for $10\%$ ripple on the capacitor voltages at: (a) $P = 3$ kW; (b)    | -        |

|             | P = 5  kW                                                                                                                      | 58       |

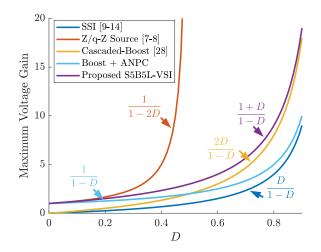

| 3.7         | Comparative output voltage gain curves of SSI, Z/q-Z source, cascaded boost, double-stage boost+ANPC, and the proposed         |          |

|             | inverter                                                                                                                       | 63       |

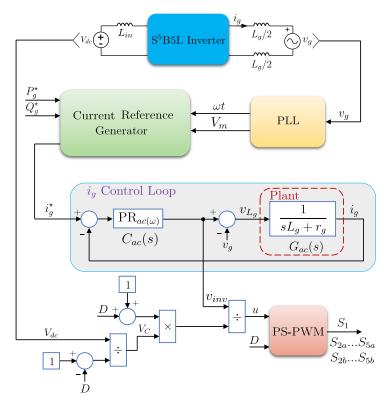

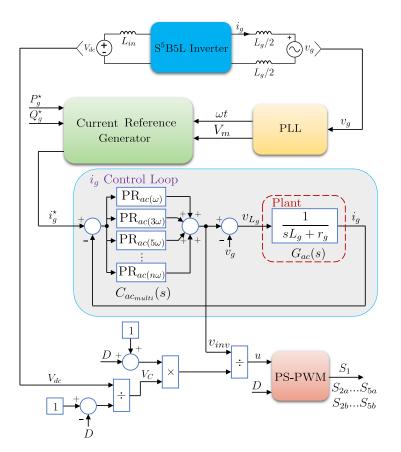

| 3.8         | Control block diagram for the proposed $S^5B5L-VSI$                                                                            | 66       |

| 3.9<br>3.10 | A picture of the 3 kW experimental prototype                                                                                   | 67       |

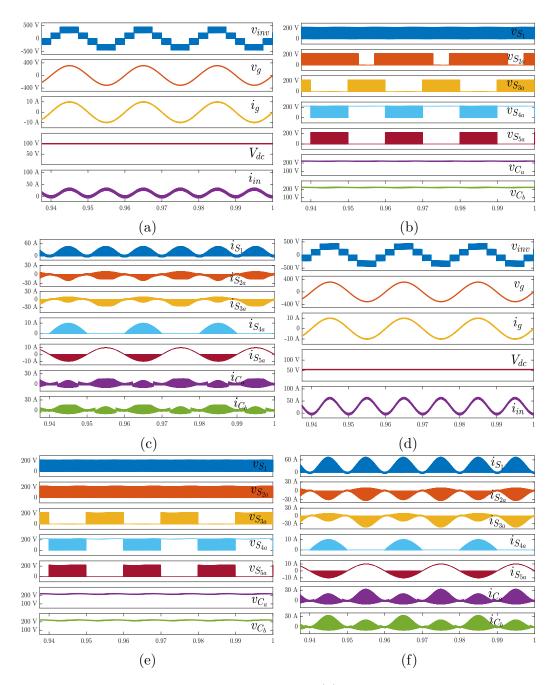

|             | of switches at $D = 0.75$                                                                                                      | 69       |

|             |                                                                                                                                |          |

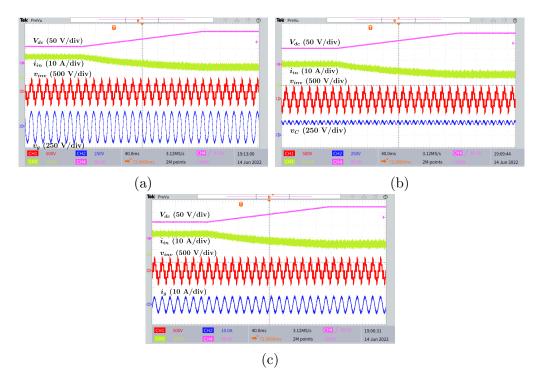

| 3.11 | Experimental results showing from top to bottom: 5L proposed inverter output voltage, the voltage across the capacitors, input current, and the load current: (a) at 1 kW output power, $D = 0.8$ , $m = 0.87$ , and $V_{dc} = 50$ V; (b) at $D = 0.8$ , and $V_{dc} = 50$ V under the step change in $m$ from 0.61 to 0.87; (c) at $V_{dc} = 50$ V, and step change in $D$ from 0.6 to 0.7; (d) at 3 kW output power, $D = 0.65$ , $m = 0.73$ , and $V_{dc} = 100$ V; (e) at $V_{dc} = 120$ V, $D = 0.65$ , $m = 0.73$ , and step change in the load value from 0.5 kW to 1.5 kW output power; and (f) the blocking voltages across $S_{3a}$ , $S_{3b}$ (green trace), $S_{5a}$ , $S_{5b}$ (pink trace), and $S_{2a}$ , $S_{2a}$ , and $S_1$ (red trace) at $D = 0.65$ , $m$ |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 9 19 | = 0.73, and $V_{dc}$ = 100 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71 |

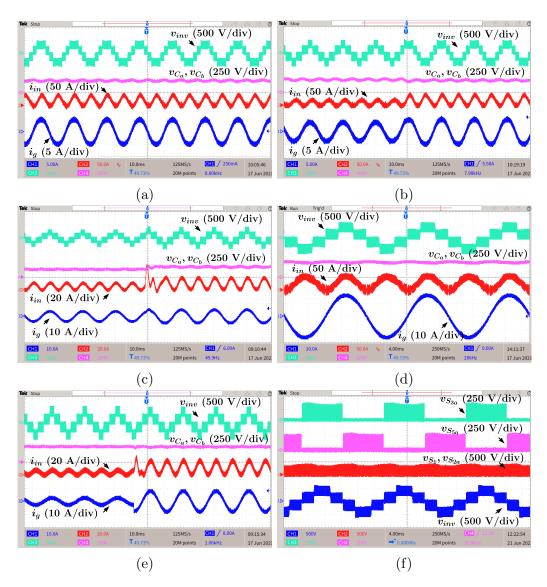

| 3.12 | Experimental waveforms of the proposed topology at (a) $V_{dc}$ = 90 V and $D = 0.6$ , (b) $V_{dc} = 55$ V and $D = 0.75$ , (c) $V_{dc} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | 40  V  and  D = 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73 |

| 3.13 | 90 V (a) leading power factor $(P = 1 \text{ kW}, Q = 1 \text{ kVAr})$ ,<br>(b) lagging power factor $(P = 1 \text{ kW}, Q = -1 \text{ kVAr})$ , and (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 0.14 | bidirectional operation $(P = -1 \text{ kW to } P = +1 \text{ kW})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74 |

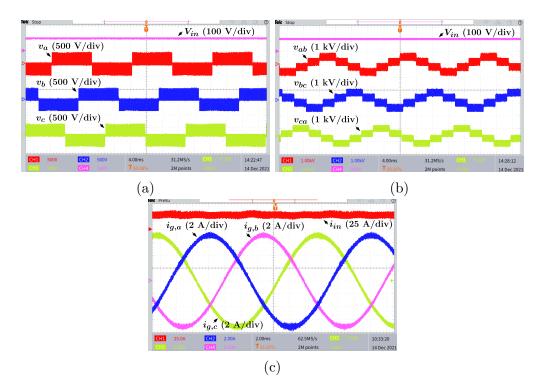

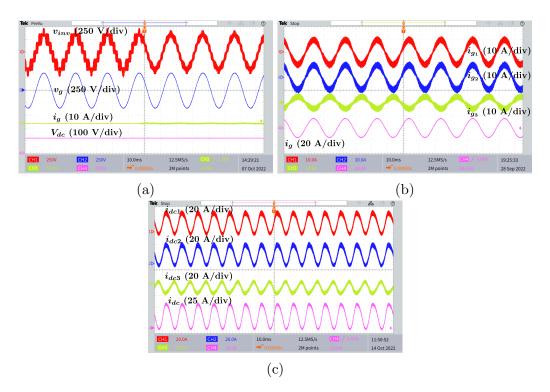

| 3.14 | Experimental waveforms of the three-phase extension of the proposed topology at $V_{dc} = 100$ V. (a) 3L phase-to-ground output voltages and DC input voltage, (b) 5L phase-to-phase voltages and DC input voltage, and (c) load current of each phase at 2.2 hW extent a group and imput support                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75 |

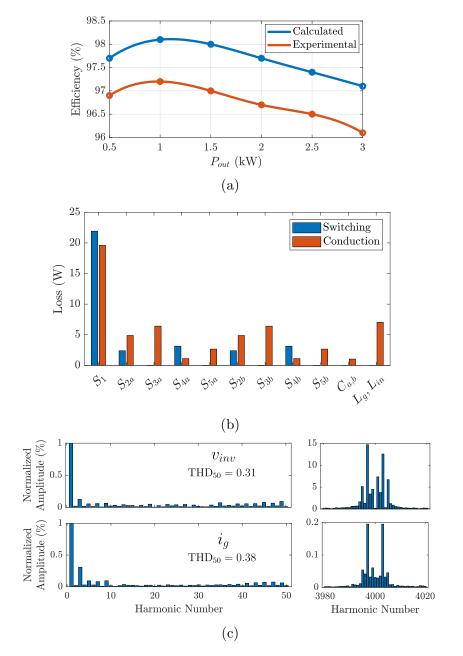

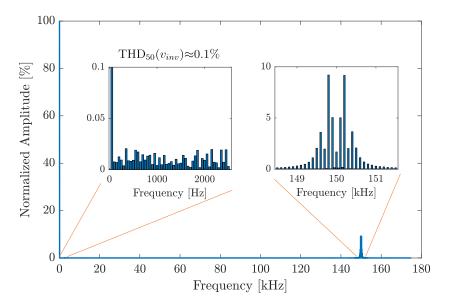

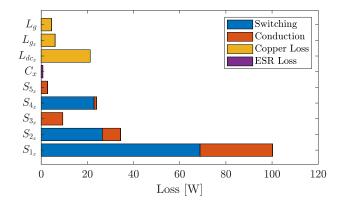

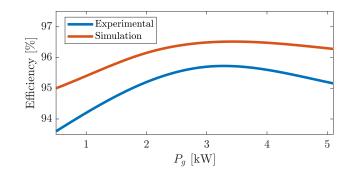

| 3.15 | phase at 3.2 kW output power and input current Converter performance: (a) Calculated and measured efficiency of the proposed S <sup>5</sup> B5L-VSI, (b) PLECS loss breakdown results at $P = 3$ kW and $V_{dc} = 100$ V, (c) experimental inverter output voltage and grid current harmonics at $P = 3$ kW, and $V_{dc}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75 |

|      | = 100  V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76 |

| 4.1  | Multi-PR control strategy for the $S^5B5L$ -VSI under distorted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

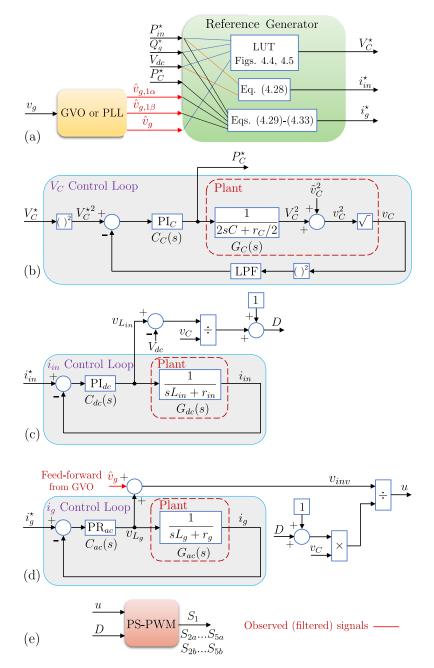

| 4.2  | grid voltage without APD functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81 |

| 4.2  | and reference generation; (b) capacitor voltage controller; (c)<br>DC input current controller; (d) grid current controller; (e)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 4.9  | Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85 |

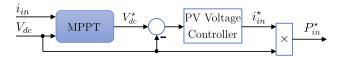

| 4.3  | Additional MPPT controller providing the input power refer-<br>ence, $P_{in}^{\star}$ , to the proposed APD control strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89 |

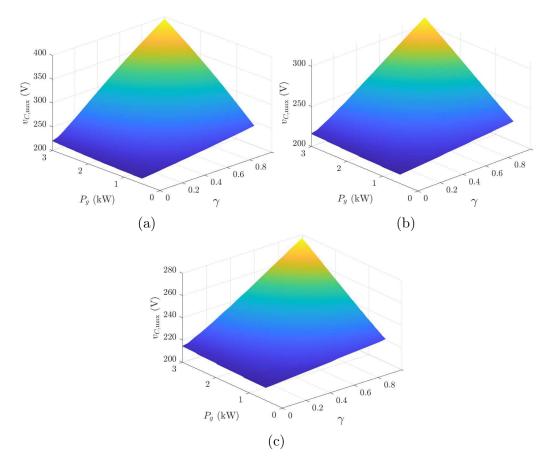

| 4.4  | Minimum required average capacitor voltage $(V_C)$ for a given                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

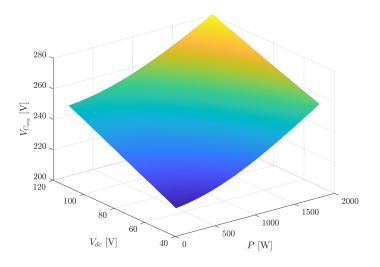

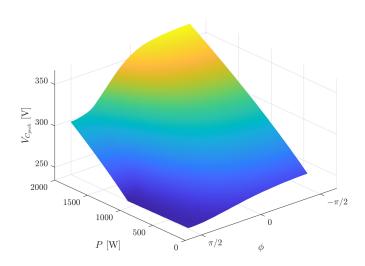

|      | grid-tied operating condition and $C = 75 \ \mu\text{F.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91 |

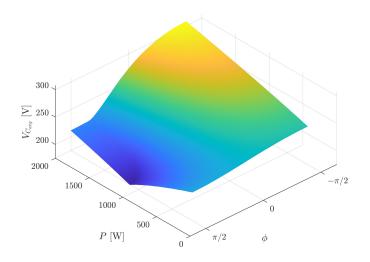

| 4.5  | Minimum required average capacitor voltage $(V_C)$ for a given $\phi$<br>and grid-tied operating condition at $V_{dc} = 100$ V and $C = 75 \mu$ F.      | 91  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

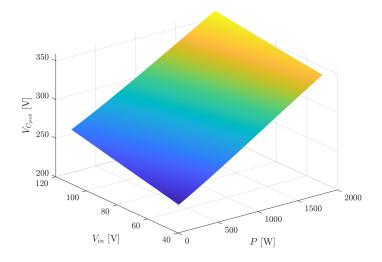

| 4.6  | Minimum required peak capacitor voltage $(V_C)$ for a given                                                                                             |     |

| 4.7  | grid-tied operating condition and $C = 75 \ \mu\text{F.} \dots \dots$<br>Minimum required peak capacitor voltage $(V_C)$ for a given $\phi$             | 92  |

| 4.8  | and grid-tied operating condition at $V_{dc} = 100$ V and $C = 75 \mu\text{F}$ .<br>Rode plot of: (a) closed loop system: $i^*$ to $i$ . (b) $i$ closed | 92  |

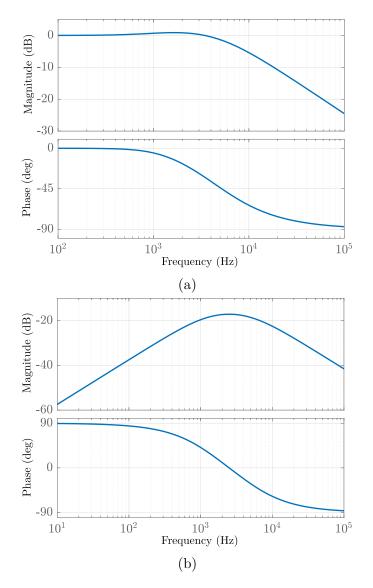

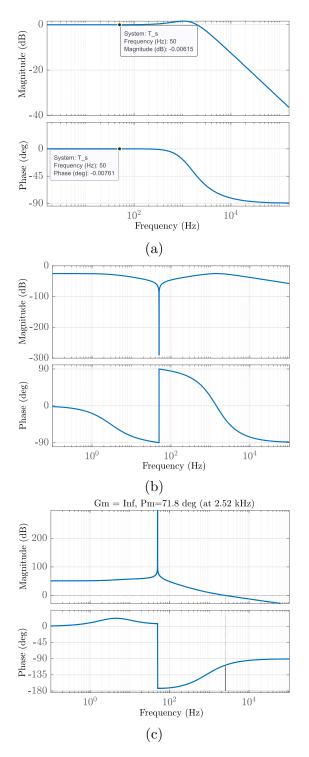

| 4.0  | Bode plot of: (a) closed-loop system: $i_{in}^{\star}$ to $i_{in}$ ; (b) $i_{in}$ closed-loop input sensitivity against input disturbances.             | 93  |

| 4.9  | Root loci plot of the closed-loop poles under varying parameter $I \neq (a)$ Overall view: (b) zeemed in view                                           | 94  |

| 4.10 | $L_g$ : (a) Overall view; (b) zoomed-in view                                                                                                            | 94  |

|      | loop input sensitivity against input disturbances; (c) stability margins of the designed $i_q$ control system.                                          | 96  |

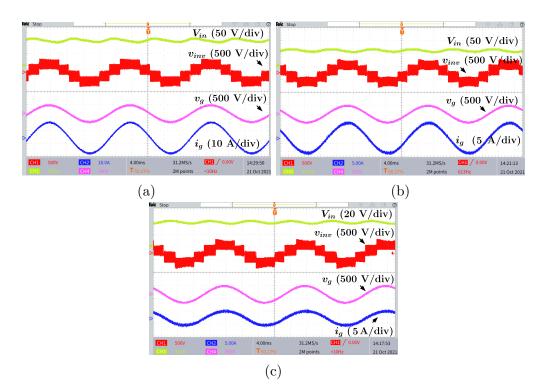

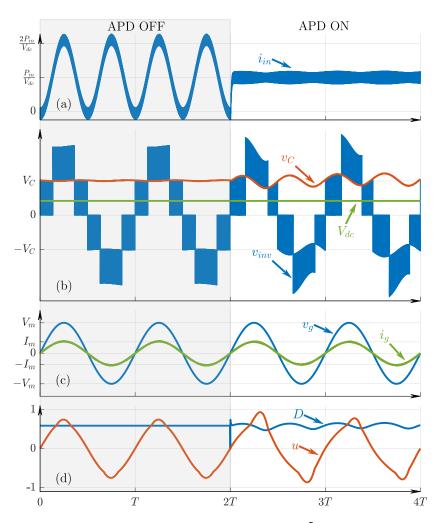

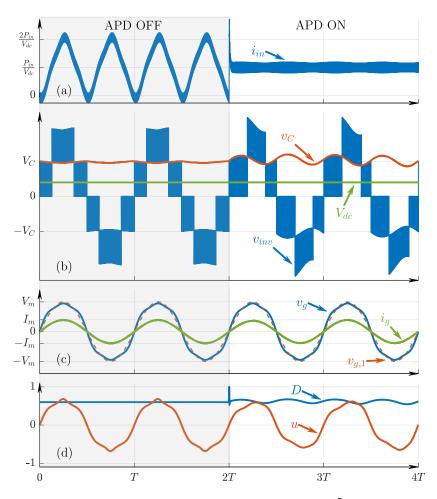

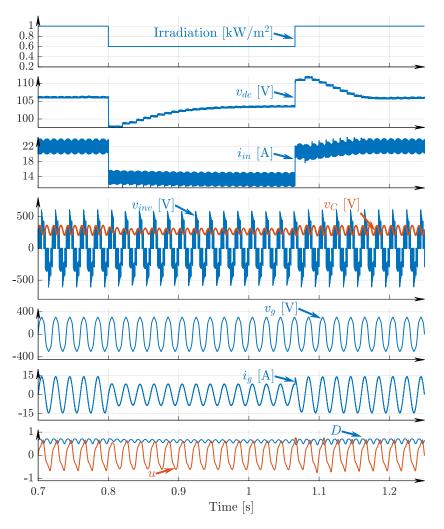

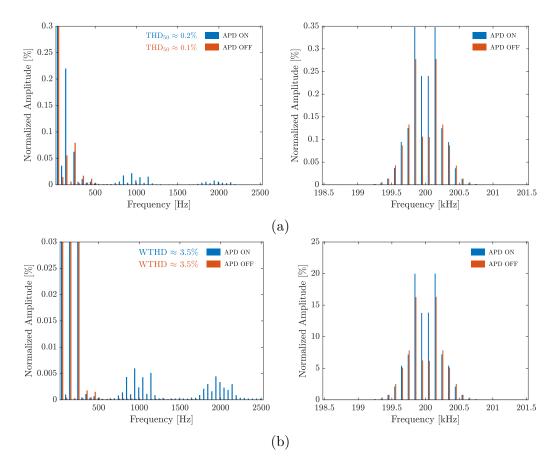

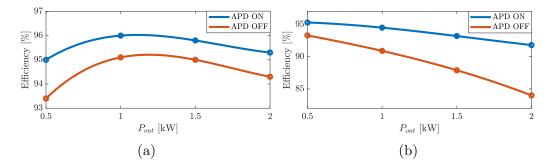

| 4.11 | Typical key operating waveforms of the S <sup>5</sup> B5L inverter under                                                                                | 90  |

|      | ideal grid-connected condition before and after enabling the proposed APD control scheme: (a) input current $(i_{in})$ ; (b)                            |     |

|      | DC input voltage $(V_{dc})$ , capacitor voltage $(v_C)$ , and inverter                                                                                  |     |

|      | output voltage $(v_{inv})$ ; (c) pure sinusoidal grid voltage $(v_g)$ , and grid current $(i_q)$ ; (d) boost duty cycle $(D)$ , and AC modulation       |     |

|      | reference $(u)$ .                                                                                                                                       | 99  |

| 4.12 | Typical key operating waveforms of the S <sup>5</sup> B5L inverter under<br>polluted grid-connected condition before and after enabling                 |     |

|      | the proposed APD control scheme: (a) input current $(i_{in})$ ; (b)                                                                                     |     |

|      | DC input voltage $(V_{dc})$ , capacitor voltage $(v_C)$ , and inverter<br>output voltage $(v_{inv})$ ; (c) polluted grid voltage $(v_g)$ with its       |     |

|      | fundamental harmonic $(v_{g,1})$ , and grid current $(i_g)$ ; (d) boost                                                                                 |     |

| 1 13 | duty cycle $(D)$ , and AC modulation reference $(u)$ RMS currents using PLECS at $P_g = 2$ kW without and with                                          | 100 |

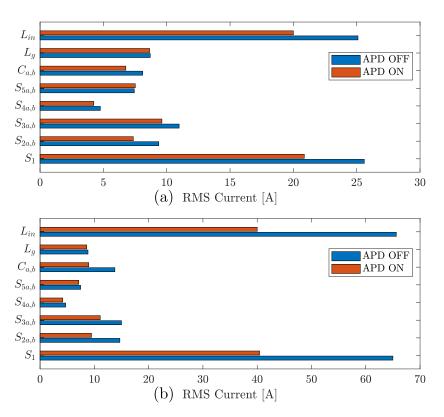

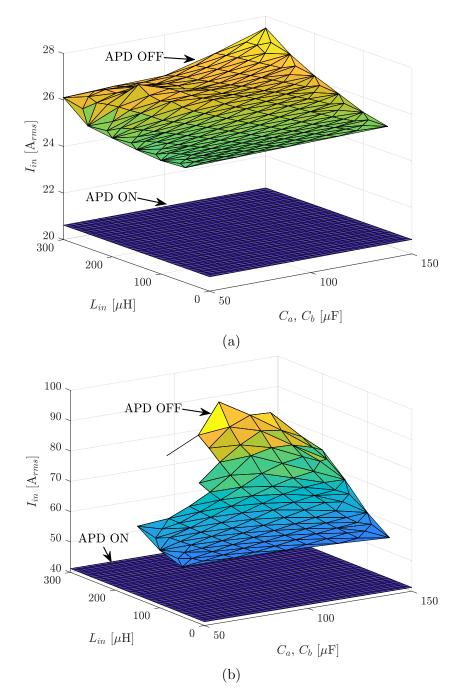

| 4.10 | APD control at: (a) $V_{dc} = 100$ V; (b) $V_{dc} = 50$ V                                                                                               | 101 |

| 4.14 | RMS input current using PLECS at $P_g = 2$ kW without and with APD control at: (a) $V_{dc} = 100$ V; (b) $V_{dc} = 50$ V                                | 103 |

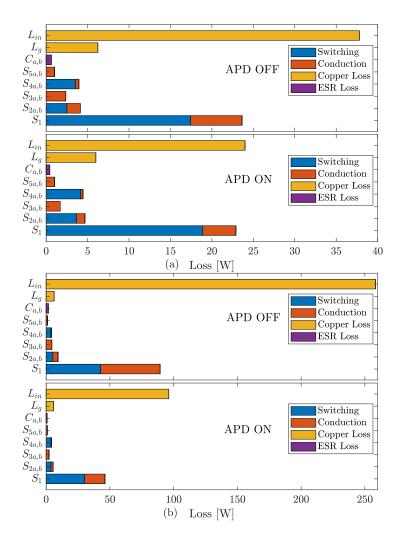

| 4.15 | Loss breakdown using PLECS at $P_g = 2$ kW without and with                                                                                             |     |

| 4 16 | APD control at: (a) $V_{dc} = 100$ V; (b) $V_{dc} = 50$ V Simulation results of a 2 kW grid-connected PV system with                                    | 104 |

| 7.10 | the proposed APD control and MPPT functionality                                                                                                         | 105 |

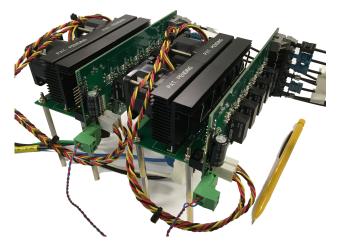

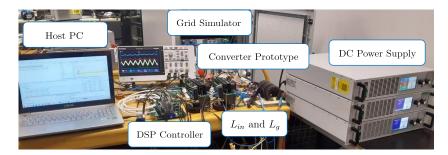

| 4.17 | A view of the experimental setup                                                                                                                        | 108 |

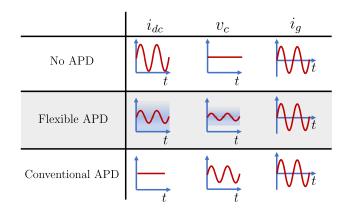

- 5.1 A qualitative comparison based on the operating conditions without APD, with conventional APD, and with the proposed FAPD methods.

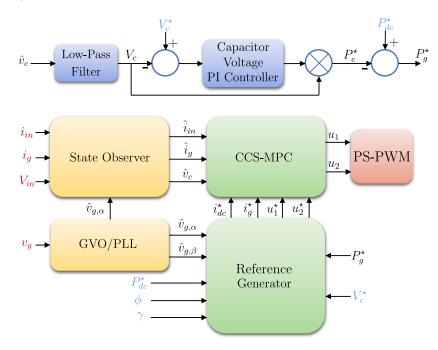

5.2 Block diagram of the proposed control system.

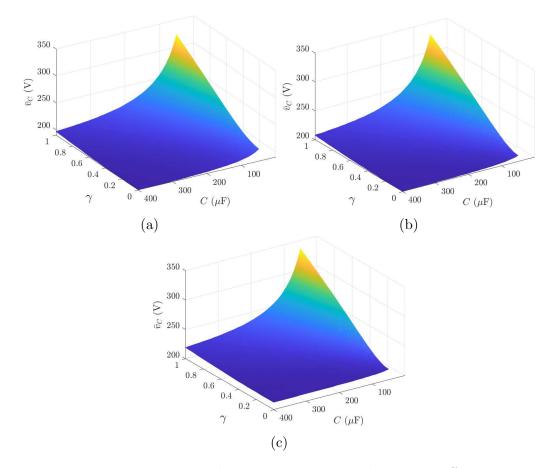

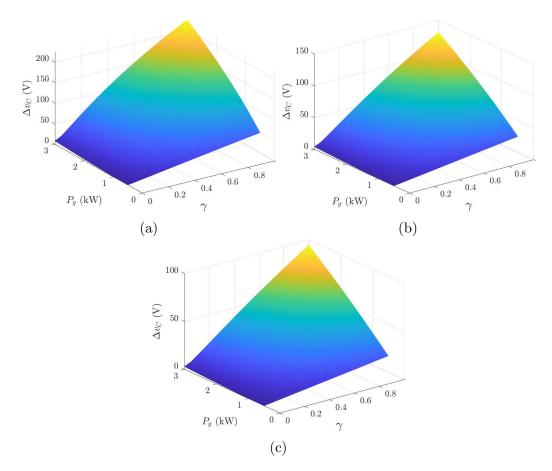

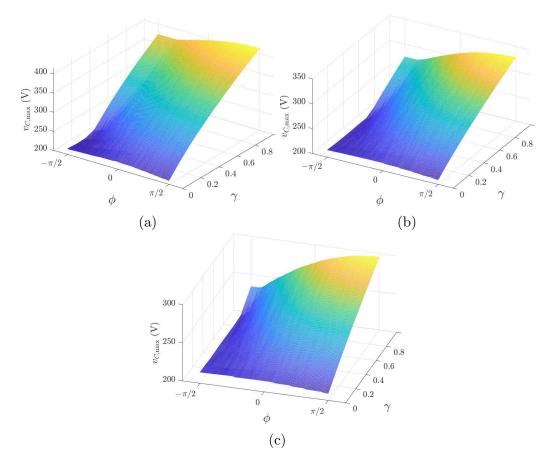

5.3 Minimum required average capacitor voltage at different ripple factors and P<sub>g</sub> = 3 kW at (a) V<sub>in</sub> = 50 V, (b) V<sub>in</sub> = 75 V, and

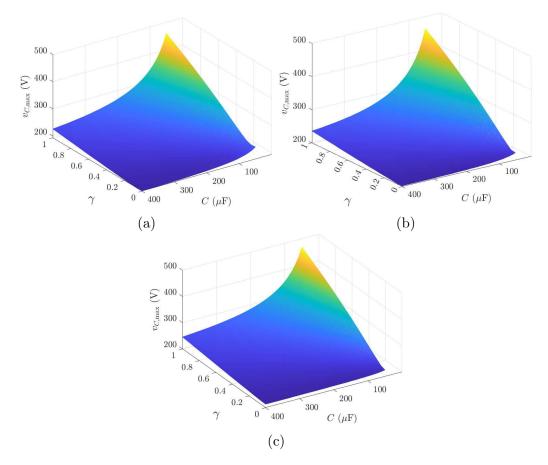

| 5.5                                       | Capacitor peak voltage at different ripple factors and $P_g = 3$ kW at (a) $V_{in} = 50$ V, (b) $V_{in} = 75$ V, and (c) $V_{in} = 100$ V. 130                                            | )      |

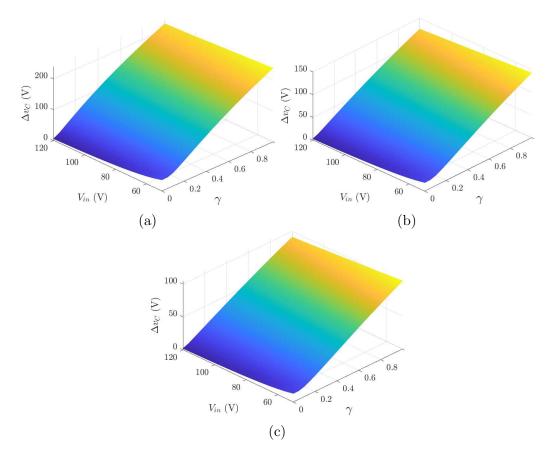

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

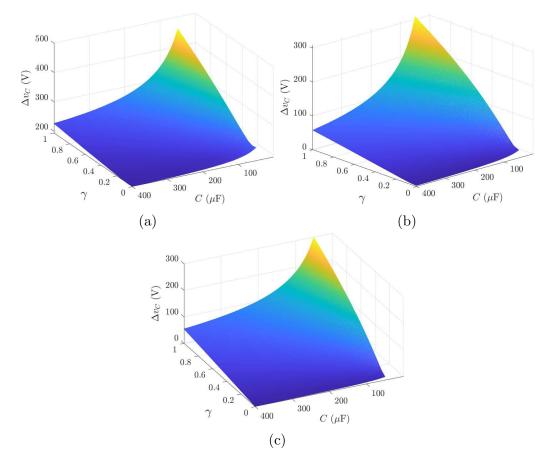

| 5.6                                       | Capacitor voltage ripple at different ripple factors at $V_{in} = 100$ V (a) $C = 75$ µF, (b) $C = 150$ µF, and (c) $C = 220$ µF. 131                                                     |        |

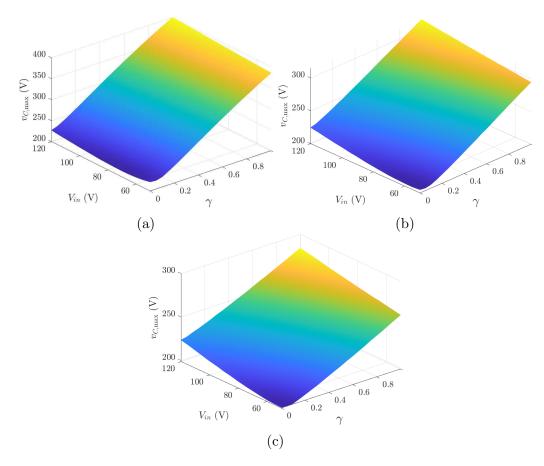

| 5.7                                       | Capacitor average voltage at different ripple factors at $V_{in} = 100$ V (a) $C = 75$ µF, (b) $C = 150$ µF, and (c) $C = 220$ µF. 132                                                    | 2      |

| 5.8                                       | Capacitor peak voltage at different ripple factors at $V_{in} = 100$ V (a) $C = 75 \mu$ F, (b) $C = 150 \mu$ F, and (c) $C = 220 \mu$ F 133                                               | }      |

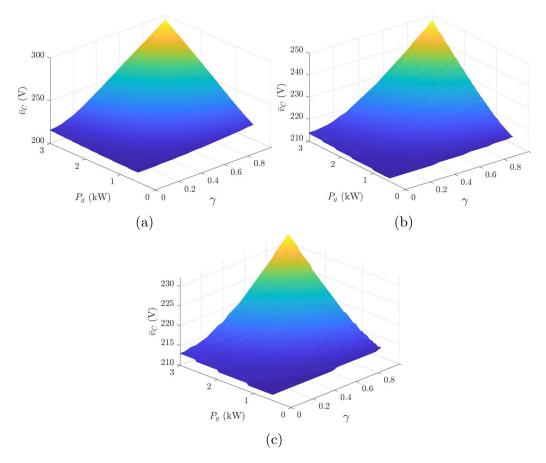

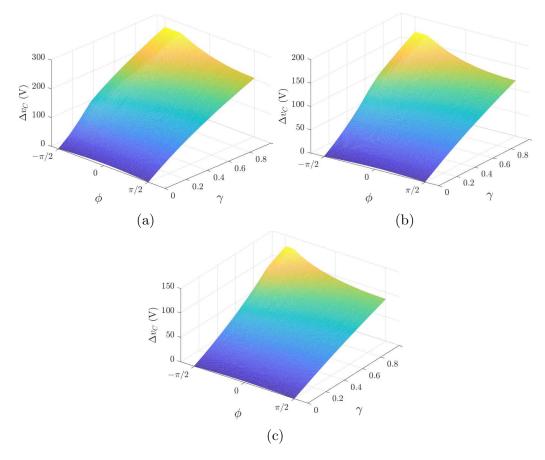

| 5.9                                       | Capacitor voltage ripple at different ripple factors and power factors, $S = 3$ kVA, $V_{in} = 100$ V (a) $C = 75$ µF, (b) $C =$                                                          |        |

| 5.10                                      | 150 $\mu$ F, and (c) $C = 220 \mu$ F                                                                                                                                                      | E      |

| 5.11                                      | 150 $\mu$ F, and (c) $C = 220 \mu$ F                                                                                                                                                      | ,<br>) |

|                                           | voltages, $P_g=3$ kW (a) $C = 75 \ \mu\text{F}$ , (b) $C = 150 \ \mu\text{F}$ , and (c) $C = 220 \ \mu\text{F}$                                                                           | 3      |

| 5.12                                      | Capacitor peak voltage at different ripple factors and input<br>voltages, $P_g=3$ kW (a) $C = 75$ µF, (b) $C = 150$ µF, and (c)                                                           | 7      |

| 5.13                                      | $C = 220 \ \mu\text{F.} \dots \dots$                                                |        |

|                                           | Simulation results of the proposed $S^5B5L-VSI$ with FAPD at                                                                                                                              | ,      |

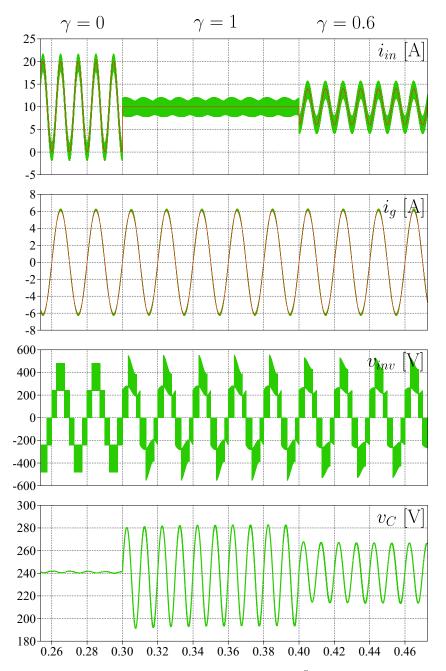

|                                           | $V_{in}=100 \text{ V}, P_g=1 \text{ kW}, \text{ and different } \gamma \text{ values. } \ldots \ldots \ldots \ldots 141$                                                                  | _      |

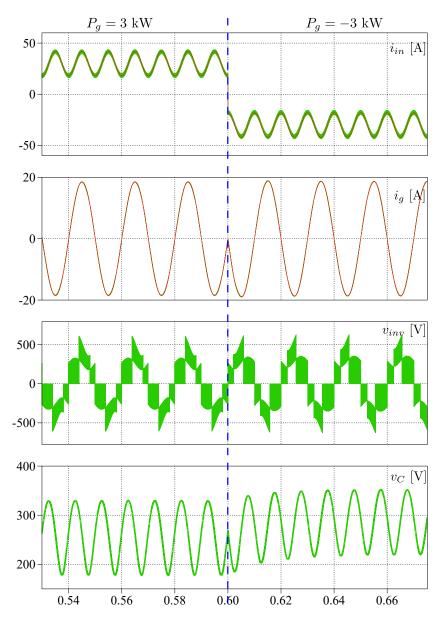

| 5.15                                      | Simulation results of the proposed $S^5B5L-VSI$ with FAPD at                                                                                                                              |        |

| 5.16                                      | $V_{in}=100 \text{ V}, \gamma = 0.6, \text{ and } P_g \text{ from } +3 \text{ kW to } -3 \text{ kW}. \dots 142$<br>Simulation results of the proposed S <sup>5</sup> B5L-VSI with FAPD at | 2      |

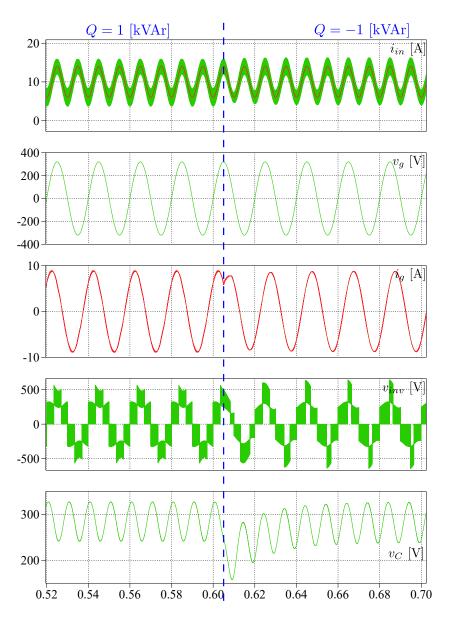

|                                           | $V_{in}=100$ V, $\gamma = 0.6$ , and $P_g = 1$ kW, and $Q_g$ from +1 kVAr                                                                                                                 |        |

| F 1 F                                     | to $-1 \text{ kVAr}$ . $143$                                                                                                                                                              | 5      |

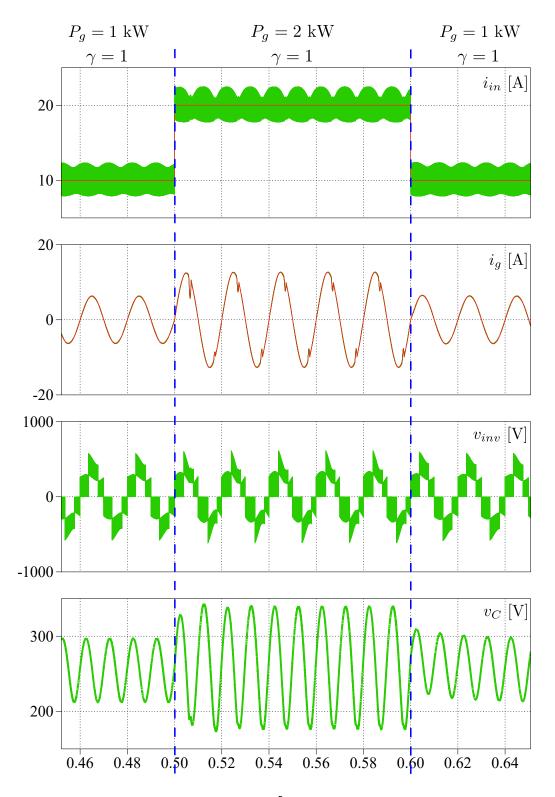

| 5.17                                      | Simulation results of the S <sup>5</sup> B5L-VSI with conventional APD<br>at $V_{in} = 100$ V, and pulsed transition from $P_g = 1$ kW to                                                 |        |

| 5.18                                      | $P_g = 2$ kW                                                                                                                                                                              | Ł      |

|                                           | $P_g = 2 \text{ kW}.$ 100 °, and pulsed transition from $T_g$ = 1 kW to                                                                                                                   | ,<br>) |

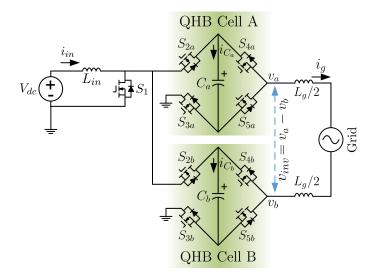

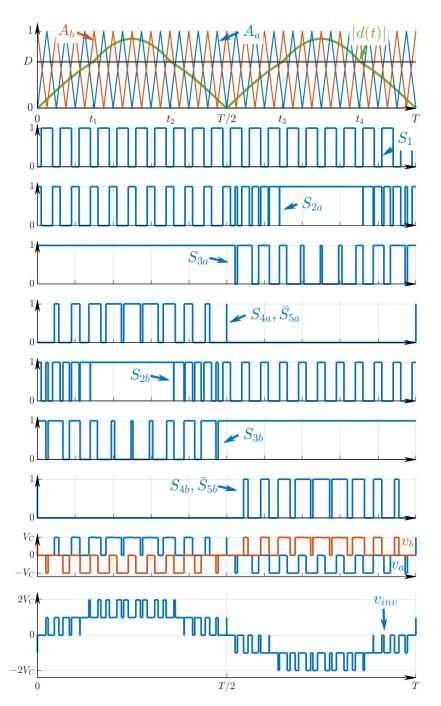

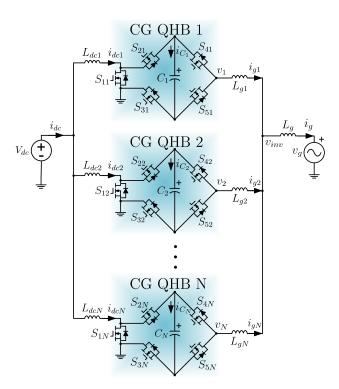

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | The proposed interleaved CGSB-based MLI                                                                                                                                                   | )      |

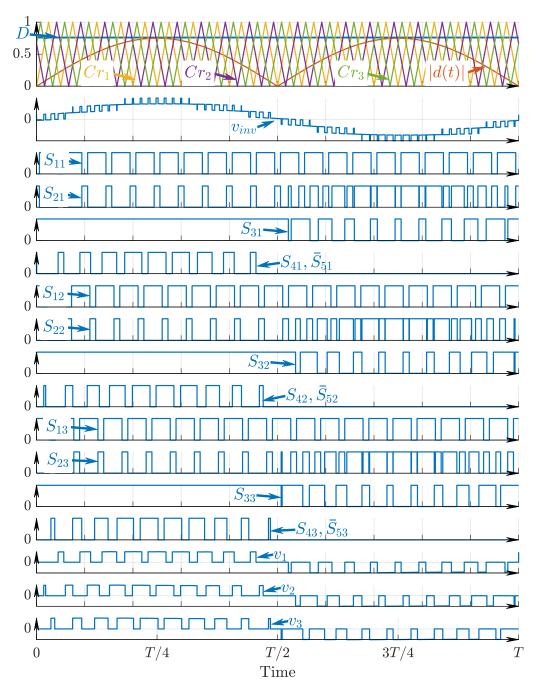

|                                           | variant of the proposed interleaved CGSB-based MLI, where $D = D_x$                                                                                                                       | 3      |

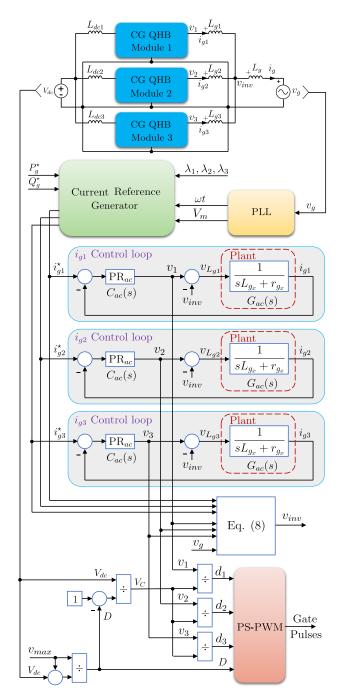

| 6.3                                       | Controller block diagram. $\ldots \ldots 155$                                                                | ,<br>) |

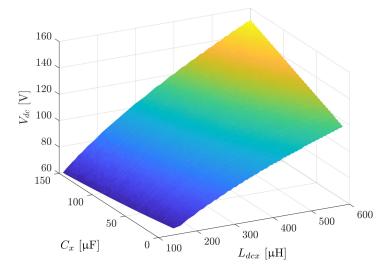

| 6.4  | Boundary values for passive circuit components using three                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------|

|      | CG-QHB modules assuming 10% ripple on capacitor voltages                                                                        |

| ~ ~  | at different DC input voltages, $V_m = 340$ V, and $P_g = 5.1$ kW. 158                                                          |

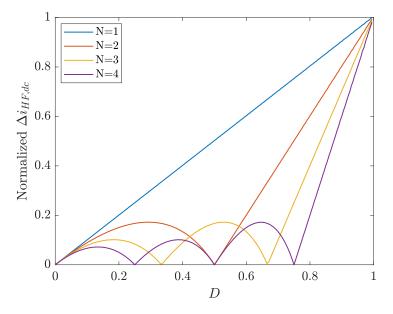

| 6.5  | Normalized high-frequency input current ripple for different                                                                    |

|      | number of interleaved CG-QHB modules                                                                                            |

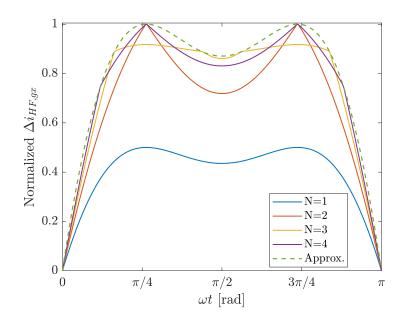

| 6.6  | Normalized high-frequency AC inductors current ripple for                                                                       |

|      | different number of interleaved CG-QHB modules at $V_{dc}$ =                                                                    |

|      | 120 V, $V_m = 340$ V, unity power factor, and $D_x = 0.76$ 160                                                                  |

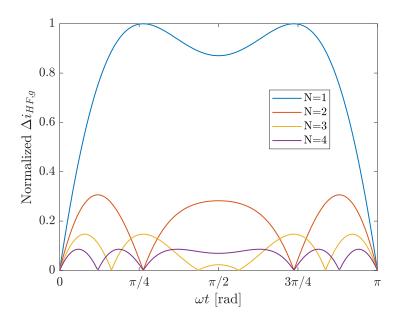

| 6.7  | Normalized high-frequency grid current ripple for different num-                                                                |

|      | ber of interleaved CG-QHB modules at $V_{dc} = 120$ V, $V_m =$                                                                  |

|      | 340 V, unity power factor, and $D_x = 0.76$                                                                                     |

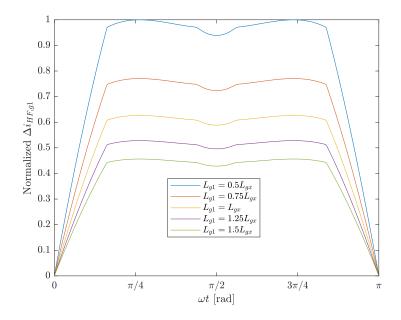

| 6.8  | Normalized high-frequency AC inductors current ripple under                                                                     |

|      | mismatched $L_{g1}$ at $V_{dc} = 120$ V, $V_m = 340$ V, unity power                                                             |

|      | factor, and $D_x = 0.76$                                                                                                        |

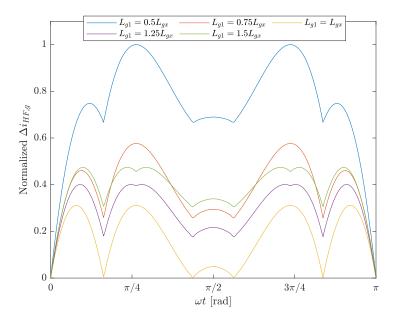

| 6.9  | Normalized high-frequency grid current ripple under mismatched                                                                  |

|      | $L_{g1}$ at $V_{dc} = 120$ V, $V_m = 340$ V, unity power factor, and                                                            |

|      | $D_x = 0.76. \dots \dots$ |

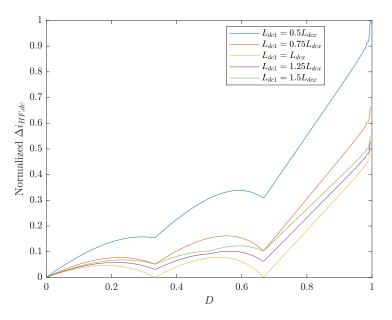

| 6.10 | Normalized high-frequency input current ripple under mis-                                                                       |

|      | matched $L_{dc1}$                                                                                                               |

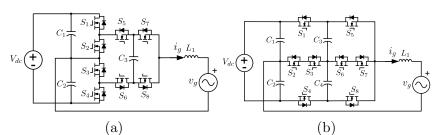

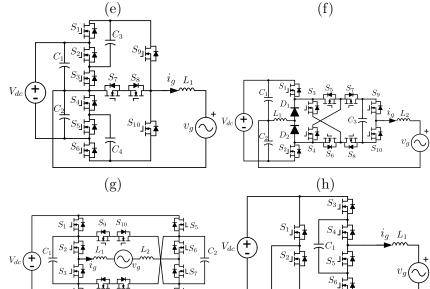

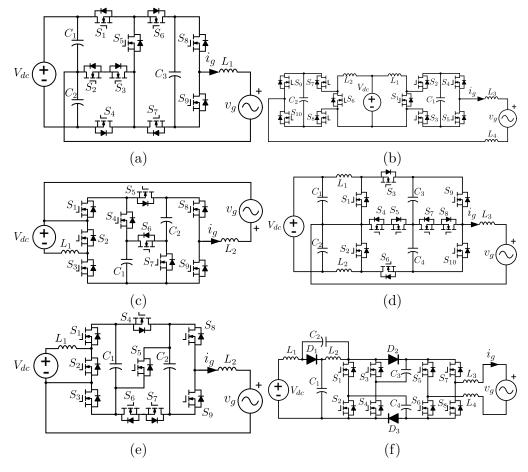

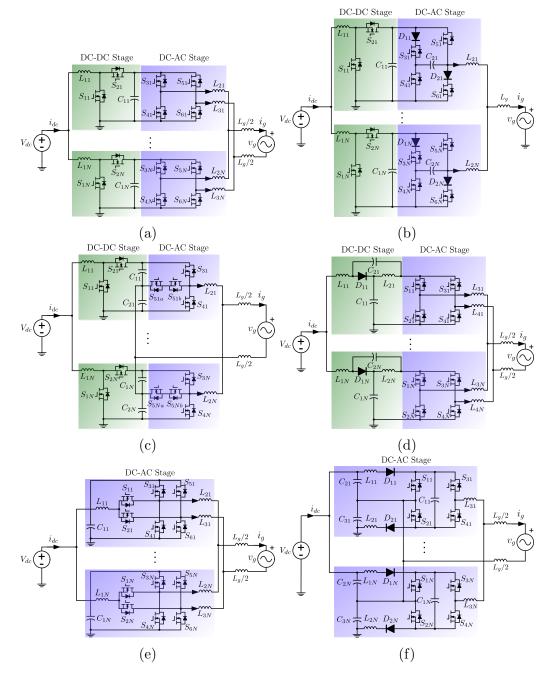

| 6.11 |                                                                                                                                 |

|      | converters based on 3L modules: (a) conventional H-bridge                                                                       |

|      | topology; (b) Siwakoti-H topology [52]; (c) T-type topology;                                                                    |

|      | (d) quasi Z-source topology [16]; (e) split-source inverter topol-                                                              |

|      | ogy [39]; (f) dual-boost H-bridge topology [175]. $\dots \dots \dots 165$                                                       |

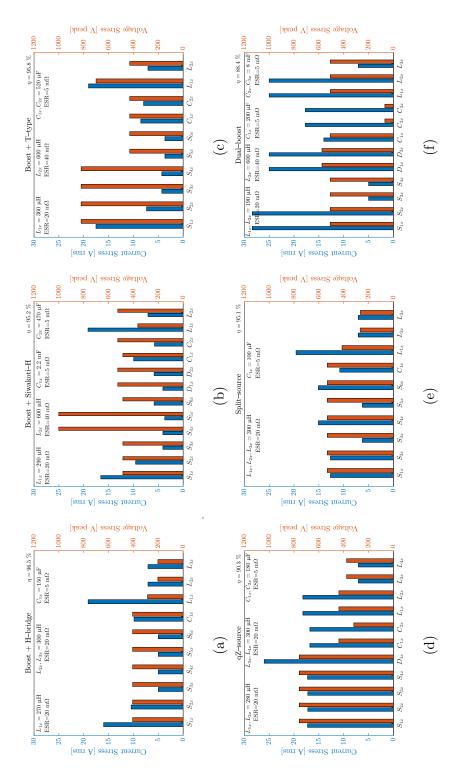

| 6.12 | Voltage and current stress analysis of components at 1.7kW                                                                      |

|      | injected power per module for the two-stage and single-stage                                                                    |

|      | single-phase interleaved dc-ac converters, when $V_{dc}=120$ V                                                                  |

|      | based on: (a) conventional H-bridge topology; (b) Siwakoti-H                                                                    |

|      | topology [52]; (c) T-type topology; (d) quasi Z-source topol-                                                                   |

|      | ogy $[16]$ ; (e) split-source inverter topology $[39]$ ; (f) dual-boost                                                         |

|      | H-bridge topology $[175]$                                                                                                       |

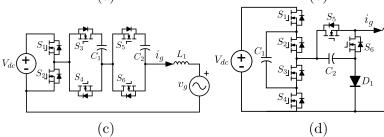

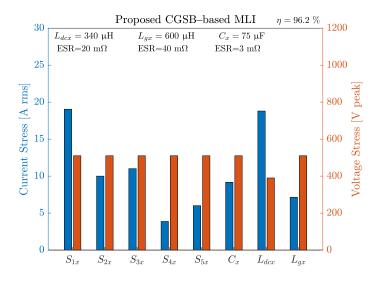

| 6.13 | Voltage and current stress analysis of components at 1.7kW                                                                      |

|      | injected power per module, when $V_{dc}=120$ V for the proposed                                                                 |

|      | CGSB-based MLI                                                                                                                  |

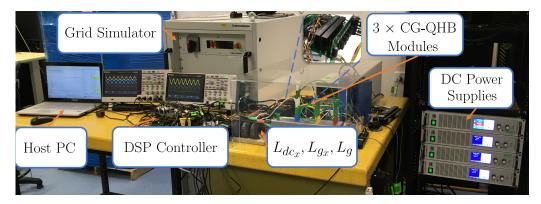

| 6.14 | A view of the experimental setup                                                                                                |

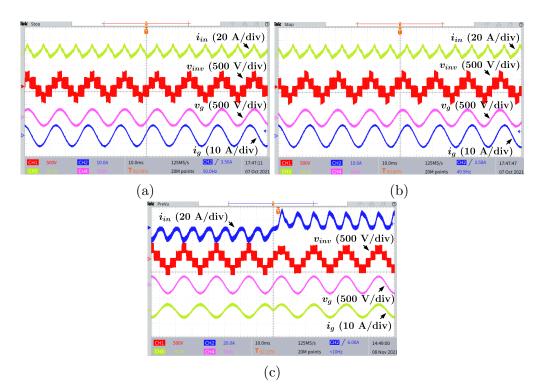

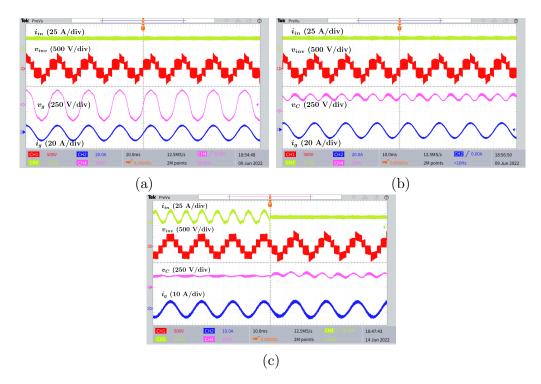

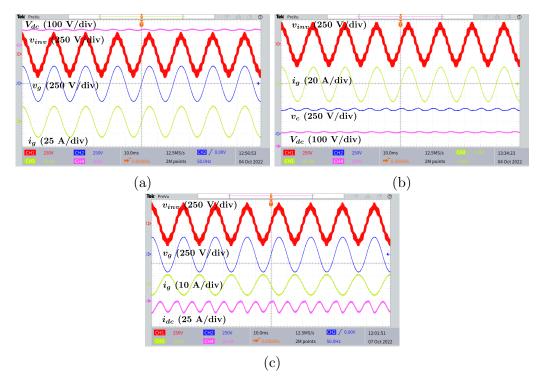

| 6.15 | Experimental results at $V_{dc} = 120$ V (a) steady-state at $P_g =$                                                            |

|      | 5.1 kW and $D_x = 0.76$ ; (b) steady-state DC input voltage                                                                     |

|      | and capacitor voltages at $P_g = 4.6$ kW and $D_x = 0.76$ ; (c)                                                                 |

|      | steady-state input currents at $P_g = -1.3$ kW and $D_x = 0.75$ . 172                                                           |

|      |                                                                                                                                 |

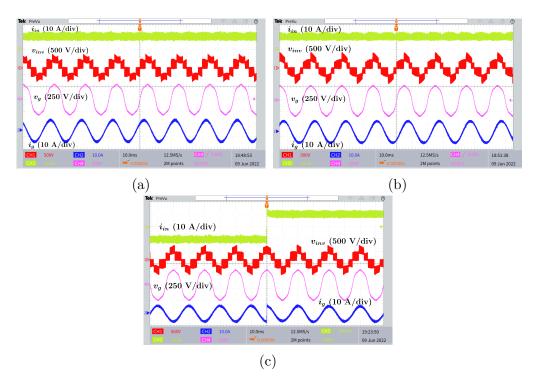

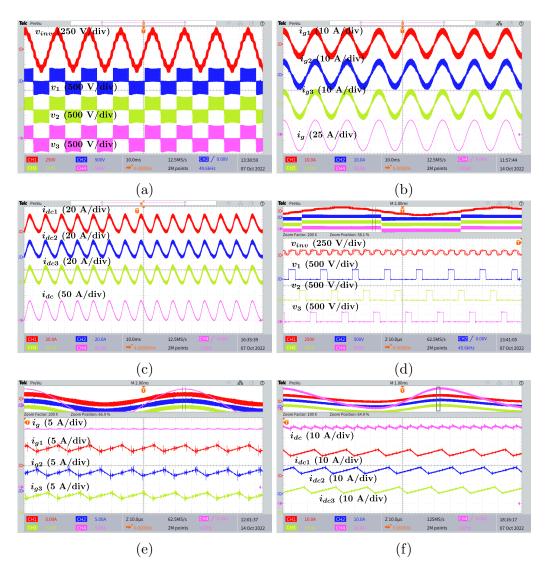

- 6.16 Experimental steady-state results at  $V_{dc} = 120$  V and  $D_x = 0.76$  (a) inverter and individual modules' output voltages at  $P_g = 5.1$  kW; (b) module AC currents at  $P_g = 5.1$  kW; (c) module DC input currents at  $P_g = 4.6$  kW; (d) zoomed-in view of inverter and modules' output voltages at  $P_g = 5.1$  kW; (e) zoomed-in view of module AC currents at  $P_g = 5.1$  kW; (f) zoomed-in view of module DC input currents at  $P_g = 4.6$  kW; (f)

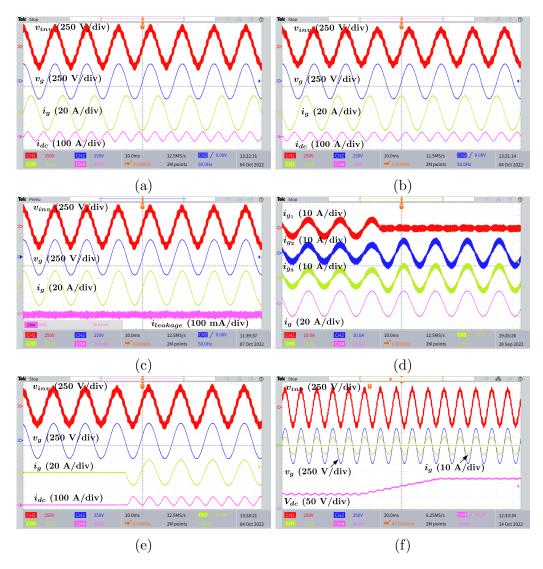

- 6.18 Experimental results at  $V_{dc} = 120$  V,  $D_x = 0.76$  (a) before and after the grid connection; (b) AC output currents at unequal power references and power flow directions; (c) DC input currents at unequal power references and power flow directions. 178

# List of Tables

| 2.1 | Conventional 3L voltage-source DC-AC converters                                     | 13  |

|-----|-------------------------------------------------------------------------------------|-----|

| 2.2 | Comparative study summary for the selected multilevel topolo-                       |     |

|     | gies                                                                                | 23  |

| 3.1 | Switching states and corresponding output voltage generation                        |     |

|     | in a QHB cell of $S^5B5L$ -VSI.                                                     | 45  |

| 3.2 | Working principle of the proposed $S^5B5L-VSI$                                      | 47  |

| 3.3 | Voltage and current stresses of the proposed $S^5B5L-VSI$                           | 50  |

| 3.4 | The list of ON switching states and the FC status of the 5L-                        |     |

|     | CG-based VSI integrated into the 9L-FC-based variant of the                         |     |

|     | proposed topology ( $\uparrow$ : Charging, $\downarrow$ : Discharging)              | 54  |

| 3.5 | Switching state and corresponding output voltage of the 9L-                         |     |

|     | FC-based variant of the proposed topology considering $V_{C_{1a}} =$                |     |

|     | $V_{C_{1k}} = V_C  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 55  |

| 3.6 | Instantaneous switching frequency of the gate signals of the                        |     |

|     | proposed $S^5B5L-VSI$ .                                                             | 59  |

| 3.7 | Turn-on and turn-off voltages and currents of the switches in                       |     |

|     | the proposed $S^5B5L-VSI$ .                                                         | 60  |

| 3.8 | A comparison between the proposed $S^5B5L$ -VSI and the other                       |     |

|     | single-source single-phase 5L-based VSIs                                            | 64  |

| 3.9 | Parameters used for the experimental prototype                                      | 66  |

| 4.1 | Controller parameters used for simulation and experimental                          |     |

|     | prototype                                                                           | 94  |

| 4.2 | A circuit characteristics-based comparison among different avail-                   |     |

|     | able topologies with APD control                                                    | 107 |

| 4.3 | Components used in the experimental prototype                                       | 108 |

| 5.1 | Sensitivity analysis results considering the grid impedance and                     |     |

|     | grid-interface filter uncertainty                                                   | 139 |

| 5.2 | Sensitivity analysis results considering the capacitance mismatch                   | 139 |

| 6.1 | Working principle of the proposed 7L variant of the proposed              |

|-----|---------------------------------------------------------------------------|

|     | interleaved CGSB-based MLI with 3 CG-QHB modules (as-                     |

|     | suming $L_g \gg L_{g_x}/N$                                                |

| 6.2 | A comparison of the proposed interleaved CGSB-MLI and                     |

|     | other interleaved topologies with 3L modules                              |

| 6.3 | System parameters used in simulation and experimental setup 171           |

| 6.4 | Components used for the experimental prototype $\ldots \ldots \ldots 171$ |

# Chapter 1 Introduction

The growth rate of renewable energy sources in the global energy market shows a clear trend and interest toward green power generation with a minimized carbon footprint. Australia has set ambitious targets to increase its share of renewable power and reduce its carbon footprint, similar to the efforts in Europe. The Australian government has established a goal to achieve 82% renewable electricity by 2030 [1,2]. Currently, Australia generates about 32% of its power from renewable sources, including wind, solar, and hydro [3]. In addition to this, Australia has committed to reducing its greenhouse gas emissions by 43% from 2005 levels by 2030 and aims to reach net zero emissions by 2050 [4].

To support the high renewable penetration in the existing electrical grids, the role of power electronic converters is inevitable. Power electronics is one of the critical enablers of integrating renewable sources in the electrical grid. Most renewable energy sources are not inherently compatible with the grid operating conditions and need a power converter as an interface. Normally, the power flow direction for renewable sources is from the source to load side (unidirectional power flow). Moreover, to address the intermittency issue of renewables, energy storage devices are crucial in modern grids. Integrating the battery energy storage systems into the grids, requires power converters with specific features such as bidirectional power flow capability, and continuous and ripple-free DC input current profile. In this case, a converter with built-in bidirectional power flow allows for efficient charging and discharging the energy-storing element (e.g., batteries, supercapacitors, etc.) according to the requested power reference commands. On the other hand, some energy-storage technologies such as fuel-cells are prone to accelerated degradation under fluctuating and changing currents [5]. Furthermore, low-frequency ripple currents in DC buses that are common in single-phase systems and unbalanced three-phase systems cause higher root-mean-square (RMS) current values passing through the components, leading to increased operating temperatures and consequent potentially reduced lifetime of the batteries or DC-link capacitors.

Furthermore, the accelerating trend of modern electric vehicles (EVs) with improved range, superior performance, and energy efficiency opens an opportunity for developing better power converters complying with the strict and challenging automotive industry requirements in terms of reliability, electromagnetic compatibility (EMC), efficiency, compactness, and of course total cost of ownership. Moreover, in smart grids, EVs are considered as moving distributed energy-storage units. Therefore, they can be operated as grid-connected inverters and participate in the grid voltage and frequency regulation services through active and reactive power injection into the grid. More specifically, energy exchange from EV to grid (V2G) and from grid to EV (G2V) are important approaches to improve the power quality, power efficiency, and reduce the users' energy bills [6-8].

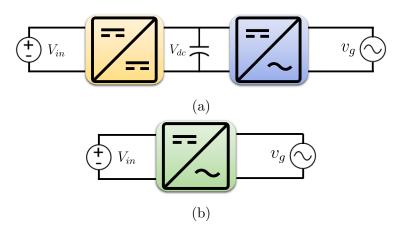

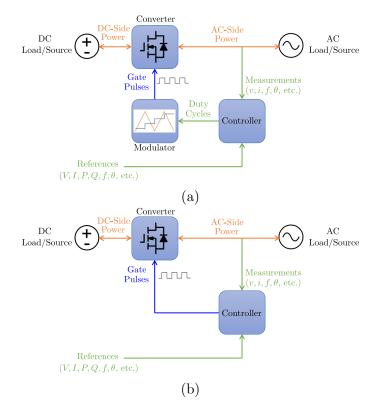

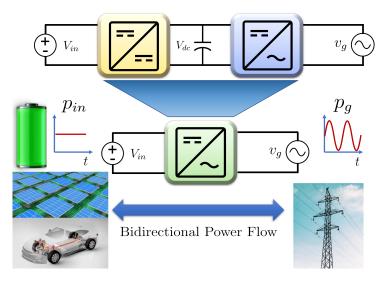

In most applications, a two-stage power conversion structure is necessary due to the requirements of the DC source and the load(s), as shown in Fig. 1.1(a). For instance, in a grid-connected PV inverter, a front-end boost DC-DC stage is followed by a DC-AC inverter, allows for Maximum Power Point Tracking (MPPT) under a wide range of irradiation and shading conditions while the grid voltage amplitude is met. Similarly, two-stage DC-AC power converters are broadly incorporated in many grid-connected applications such as battery energy storage systems. It should be noted that in some particular applications such as wind-based energy generation, the input source has an AC voltage waveform and, therefore, it requires a different power converter).

One of the requirements for EV, fuel-cell, battery, and PV applications is a ripple-free and steady DC power. Therefore, due to the difference in the instantaneous power at the DC and AC ports, a power decoupling strategy is necessary. Conventionally, active or passive buffer circuits are used to address this issue in DC-AC converters. Thus, the buffer circuit needs to compensate and inject a suitable voltage or current to cancel this undesirable input ripple. However, including an additional buffer circuit to a DC-AC converter can increase the size, cost, complexity, and potentially the overall failure rate of the system. As a common practice, a two-stage structure is used in many grid-connected inverter units as shown in Fig. 1.1(a). The first DC-DC stage is responsible for achieving DC input voltage control as well as boosting the voltage to an appropriate level for the DC-AC stage. Moreover, the DC-DC stage in conjunction with the DC-link capacitor can serve as an Active Power Decoupling (APD) circuit to redirect the ripples from the DC port

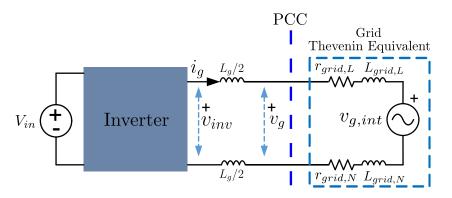

Fig. 1.1. DC-AC converter architectures: (a) conventional two-stage inverter with a dedicated boost stage, (b) single-stage inverter with integrated voltage boosting capability.

to the DC-link capacitor. However, the same level of functionality can be reached with some of the proposed single-stage DC-AC converters as shown in Fig. 1.1(b).

Power electronic converters with single power processing DC-AC stage have been recognized as efficient, compact, and attractive solutions during the latest years for the newly-developed renewable-energy (RE)-based systems [9]. This concept, as shown in Fig. 1.1(b), is motivated by targeting some shortcomings associated with the two-stage DC-AC converters such as lower overall efficiency, larger number of required components, lower feasible range of output voltage gain, higher manufacturing cost, and lower overall power density [10, 11]. The main research objectives and an overview of the report are presented in the next section.

### 1.1 Research Objectives

The main aim of this research is to propose improved DC-AC multilevel converter structures, modulation, and control strategies tailored for gridconnected applications with RE- and battery-based sources. More specifically, this work is moving toward the single-stage boost-based DC-AC converters with developed advanced capabilities such as dynamic voltage boosting gain, APD, bidirectional power flow, and full reactive power support.

The specific research objectives of this thesis are:

1. To propose and improve flexible single-stage multilevel converter structures complying with the application-specific requirements for both single- and three-phase use cases

- 2. To develop integrated modulation and control strategies to enable the potential advanced features of the converters

- 3. To design control strategies with active power decoupling feature for single-stage multilevel converters as a critical requirement for PV, fuel cell, and battery operated systems

- 4. To investigate the possibility of power/current sharing within a multilevel converter with a modular architecture as an enabler for active thermal control techniques

- 5. To implement power converters with corresponding controllers to achieve bidirectional power flow feature for the battery-based systems such as EVs or battery energy storage systems

### 1.2 Thesis Overview

The rest of the thesis is structured as follows:

Chapter 2 provides a literature review on major aspects of power electronics converters with a focus on grid-connected applications. This includes an overview of the circuit topologies used in power converters, and various modulation and control approaches to be applied on power converters. Moreover, the identified gaps in the literature have been explained.

Chapter 3 aims to present a family of multilevel converters with the singlestage dynamic voltage-boosting feature, reduced number of circuit components, modular structure, bidirectional operation, continuous input current, and acceptable overall efficiency. The proposed structure is based on a threelevel single-stage boost integrated inverter with an embedded quasi H-bridge (QHB) cell. These features allows using the proposed converters as an interface between the available varying low-voltage DC sources (e.g., battery or PV) and a standard AC grid. In addition, the proposed converters have the potential for integrating active power decoupling, that is investigated in the following chapters. The proposed topology directly addresses research objectives 1 and 5, and the proposed modulation to enhance the maximum voltage gain links to research objective 2.

Chapter 4 aims to implement an integrated active power decoupling technique using the proposed S<sup>5</sup>B5L-VSI to eliminate the double-line frequency ripple at the DC port without any additional components. APD is particularly critical for single-phase EV chargers, battery- and RE-based applications, as it improves the power quality at the DC side and enhances the overall power efficiency. This chapter addresses research objectives 2, 3, and 5 using the proposed APD control for bidirectional power flow control under distorted grid voltage conditions.

Chapter 5 extends the flexibility of conventional active power decoupling strategies and allows for a dynamically adjustable tradeoff between the double-line frequency ripple in the DC input current and capacitor voltage ripple. This can be used to reduce the voltage stress on the active and passive components or reducing the minimum capacitance requirement. This chapter links to research objectives 2, 3, and 5 by introducing a flexible active power decoupling control strategy with bidirectional power flow support.

Chapter 6 aims to implement a new concept of interleaved commongrounded switched-boost multilevel inverter (CGSB-MLI). It offers several important features including bidirectional power flow support, modularity, higher power handling capability through the interleaved circuit configuration, compatibility with PS-PWM technique, and uniform maximum voltage stress across the switches while retaining its single-stage dynamic voltage boosting. The common-grounded structure makes this converter an attractive candidate particularly for the applications where the negligible leakage current generation is a priority (e.g., PV sources). The presented topology in this chapter aligns with research objectives 1, 4, and 5, and its control strategy follows research objectives 2 and 4.

Finally, Chapter 7 summarizes the results and implications of this work, and provides recommended directions for the future works.

### Chapter 2

### Literature Review

DC-AC power converters are one of the essential building blocks in modern electricity grids and AC microgrids. In this chapter, an overview of the available circuit topologies and control approaches for DC-AC power converters has been presented. Firstly, suitable circuit topologies in the literature have been categorized and reviewed based on their features and characteristics. Next, conventional and advanced control strategies in this context have been summarized based on their structure. Finally, some of the identified research gaps and major design challenges in terms of topology and control methods have been explained.

### 2.1 DC-AC Converters

DC-AC converters can be categorized into three main groups based on their output characteristics:

- Voltage-Source Converters: The vast majority of the available DC-AC converters fall into this group due to easier implementation and component availability, especially for low- and medium-power converters. In this type, the output voltage of the converter is synthesized by connecting the circuit capacitors in different combinations to generate a switched voltage waveform (which can be filtered to obtain a smooth current waveform). Hence, the output of these converters behaves as a voltage source. Therefore, these converters are vulnerable to short-circuit faults, and over-current protection is essential to ensure a safe operation. Moreover, usually, all the power switches should be opened in case of a fault occurrence [12].

- Current-Source Converters: As opposed to voltage-source convert-

ers, in this group, the output current is synthesized by routing the current of an inductor to the output to generate a switched current waveform (which can be filtered to obtain a smooth voltage waveform). Hence, the output of these converters acts as a current source [13]. Consequently, they are vulnerable to open-circuit faults, and over-voltage protection is a key requirement [14]. The most important feature of this group of converters is their inherent immunity against short-circuit faults. However, their power density and efficiency are limited due to the required additional circuit components and magnetic elements compared to voltage-source converters [15].

• Impedance-Source Converters: Unlike voltage-source and currentsource converters, impedance-source converters can handle both opencircuit and short-circuit fault conditions at their outputs for a short time. They also can offer voltage-boosting capabilities based on their unique structure [16–18]. In this type of converter, an impedancesource circuit based on arrangement of passive elements (i.e., inductors and capacitors) is followed by a switching circuit to generate a switched voltage waveform to be filtered at consequent stages [19].

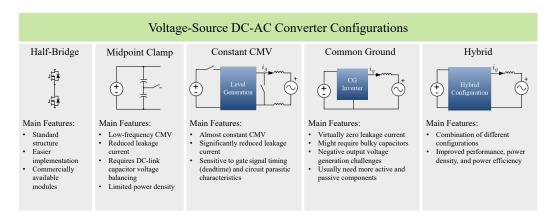

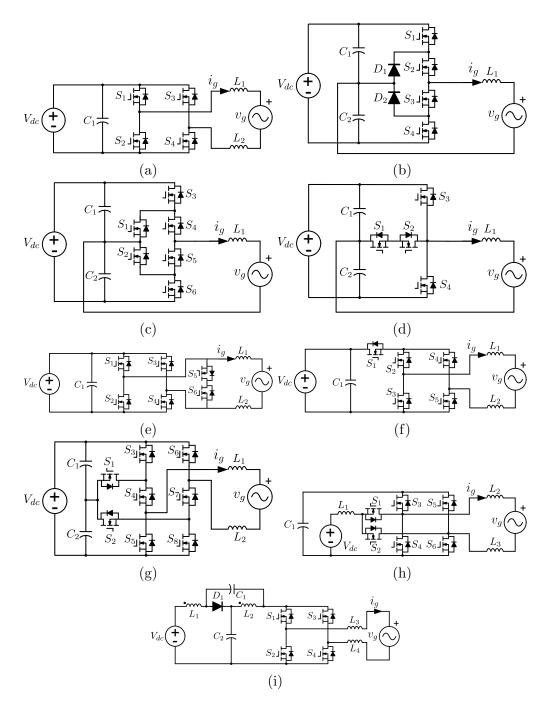

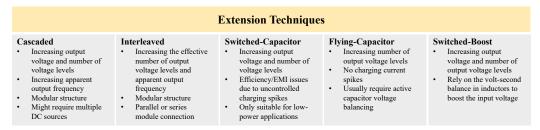

|                   | DC-AC Converters                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                             |  |

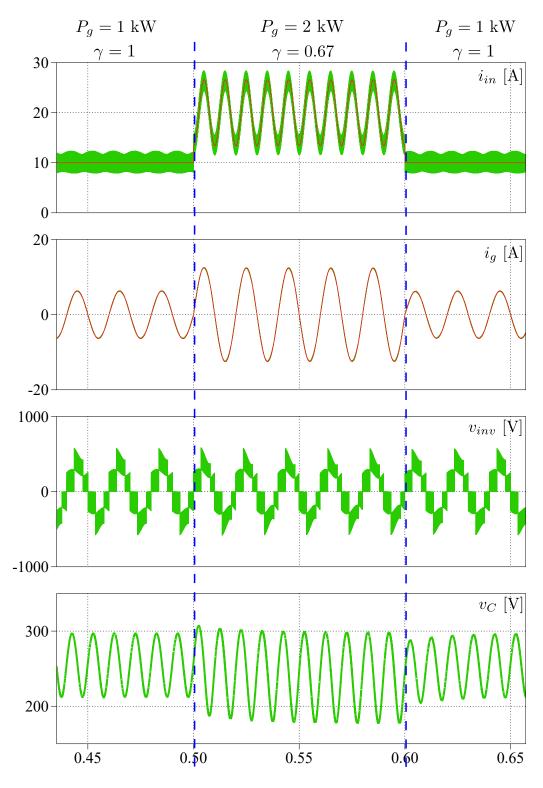

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|